ARM CoreSight:多核SoC调试追踪架构解析

目录

1.核心目标与优势

2.架构组成:“源→链路→接收端” 的数据流逻辑

3.三大核心通路:覆盖调试、追踪、触发需求

4.物理接口与工具支持

补充:

2.各组件的定义与作用

(1)SWV(Serial Wire Viewer,串行线查看器)

(2)SWO(Serial Wire Output,串行线输出)

(3)SWD调试接口

(4)ITM(Instrumentation Trace Macrocell,指令跟踪宏单元)

(5)TPIU(Trace Port Interface Unit,跟踪端口接口单元)

(6)组件之间的联系(工作流程)

3.ITM的使用

ARM CoreSight 是 ARM 推出的系统级调试与追踪(Debug & Trace)架构,为 SoC(尤其是多核场景)提供实时调试、事件追踪、功耗 / 时钟域管理及系统拓扑自描述的统一解决方案,核心特点与组成如下:

1.核心目标与优势

-

非干预性可见性:调试 / 追踪时无需暂停 CPU,不影响系统实时运行(如支持

printf类输出、指令流跟踪的同时,程序仍正常执行)。 -

跨组件 / 厂商互操作性:不同厂商的 CoreSight 组件(如 ETM、ITM、TPIU 等)按规范集成,保证兼容性。

-

复杂场景适配:应对多核、多功耗域、多时钟域的调试需求;支持自动拓扑发现(通过 ROM Table),无需预存硬件信息即可识别所有调试组件。

2.架构组成:“源→链路→接收端” 的数据流逻辑

CoreSight 通过三类核心组件组织调试 / 追踪数据流:

3.三大核心通路:覆盖调试、追踪、触发需求

CoreSight 通过三条逻辑通路协同工作:

-

Trace 通路(跟踪通路):负责 “CPU / 总线行为的实时跟踪”——ETM/STM 等 Source 生成跟踪数据,经 Funnel、Replicator 等 Link 转发,最终由 TPIU(输出到外部调试器)或 ETB(片上存储)等 Sink 接收。

-

Debug 通路(调试通路):负责 “外部调试器对 SoC 的访问”—— 外部调试器(如 J-Link)通过 JTAG/SWD 接口连接 DAP(Debug Access Port),DAP 将请求转换为片上总线(如 APB、AHB)访问,进而操作 CoreSight 组件(如配置 ETM)或 SoC 外设 / 内存。

-

Trigger 通路(触发通路):负责 “多组件间的触发信号同步”——CTI/CTM(Cross Trigger Interface/Matrix) 实现触发信号的 “接收 - 路由 - 发送”,支持 “一组件触发,多组件响应”(如断点触发时,同步启动跟踪、停止计时等)。

4.物理接口与工具支持

-

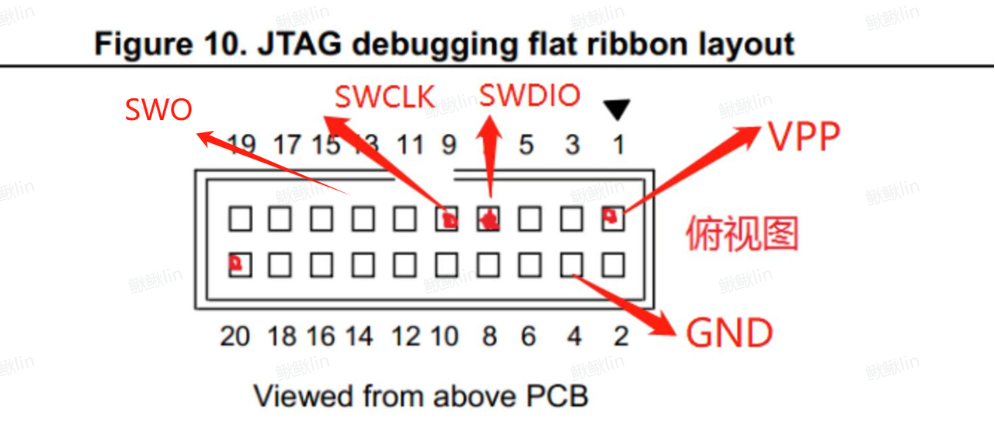

调试接口:支持传统 JTAG-20(兼容 IEEE 1149.1)、高速 CoreSight-10/20(引脚少、串并复用)、实验室级 MICTOR(大带宽并行 Trace)等。

-

工具生态:ARM 开发工具、Keil、IAR 等超 25 种调试 / 性能分析工具支持 CoreSight,确保生态友好。

综上,ARM CoreSight 是一套面向复杂 SoC 的 “模块化、可扩展、自动化” 调试与追踪架构,通过分层组件、逻辑通路和系统级设计,解决了多核、多域场景下的调试难题,同时兼顾实时性、安全性与工具兼容性。

补充:

SoC(System on Chip,系统级芯片 / 片上系统)是指在单个芯片上集成电子系统所需全部功能的超大规模集成电路,将处理器、内存、接口、通信模块等硬件,以及操作系统、应用程序等软件相关的设计,从算法、架构到电路器件层面一体化集成,通常为定制化产品。

2.各组件的定义与作用

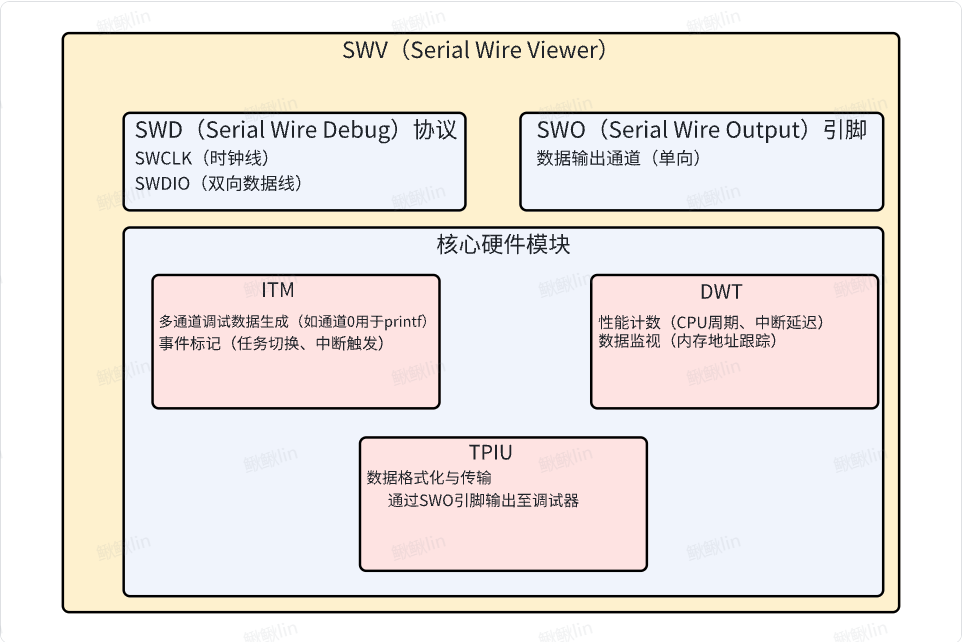

SWV(Serial Wire Viewer,串行线查看器)不是 “物理上包含” ITM、TPIU、SWO 的单一模块,而是基于 ARM CoreSight 调试架构,通过 ITM、TPIU、SWO 等硬件组件协作,实现 “从 MCU 内部获取调试信息并在上位机可视化” 的技术方案 / 功能体系。

(1)SWV(Serial Wire Viewer,串行线查看器)

-

定义:ARM CoreSight 调试架构中的上位机工具组件,用于实时监测嵌入式系统的运行状态。

-

作用:

-

实现实时数据跟踪:监控变量、内存区域的数值变化;

-

支持程序流跟踪:分析函数调用关系、中断触发顺序等执行流程;

-

完成事件跟踪:捕捉异常、断点、任务切换等关键事件;

-

开展性能分析:统计 CPU 使用率、函数执行耗时等性能指标;

-

进行变量监控:无需暂停程序,即可观察指定变量的动态变化。由于数据传输机制高效,SWV 对目标系统的性能干扰极小,是低成本、低侵入性的实时调试方案。

-

(2)SWO(Serial Wire Output,串行线输出)

-

定义:Cortex-M 内核 CoreSight 架构中的单引脚、单向物理接口(通常与 JTAG 的

TDO引脚复用)。 -

作用:作为片上跟踪数据到外部调试器(如 J-Link、ST-Link)的 “桥梁”,传输 ITM/TPIU 处理后的调试信息。支持UART 编码或曼彻斯特编码(不同调试器支持类型不同,如 J-Link 主要支持 UART 编码),是调试数据从芯片到上位机的 “物理传输通道”。

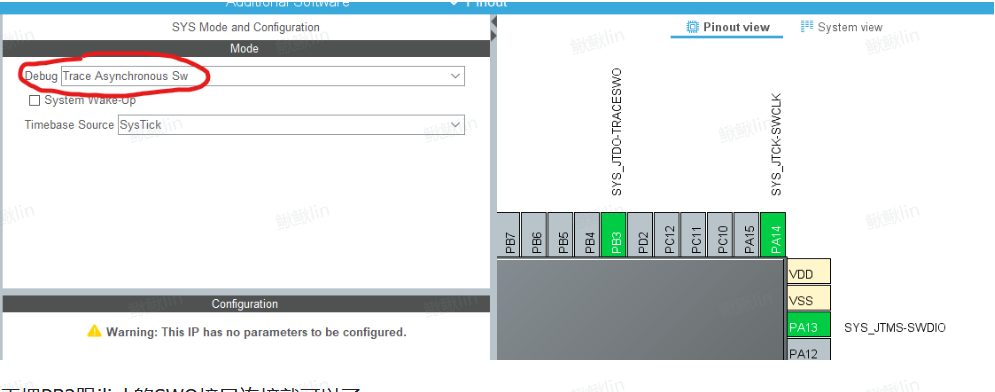

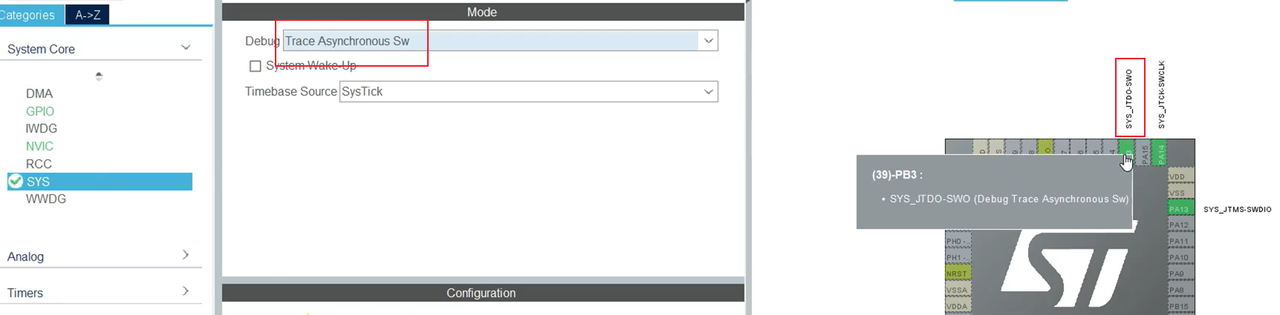

cubemx中将debug配置为trace模式,会自动使能PB3为SWO接口

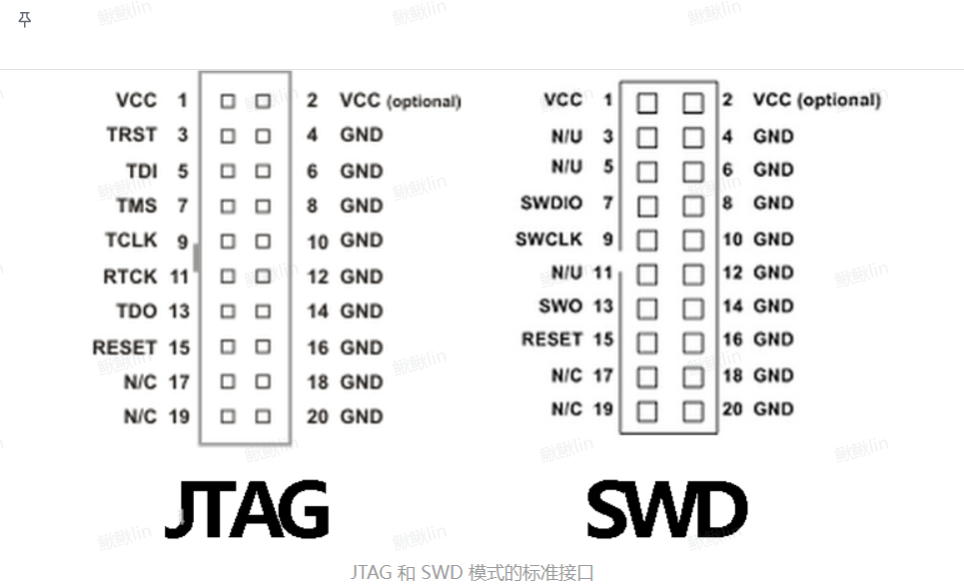

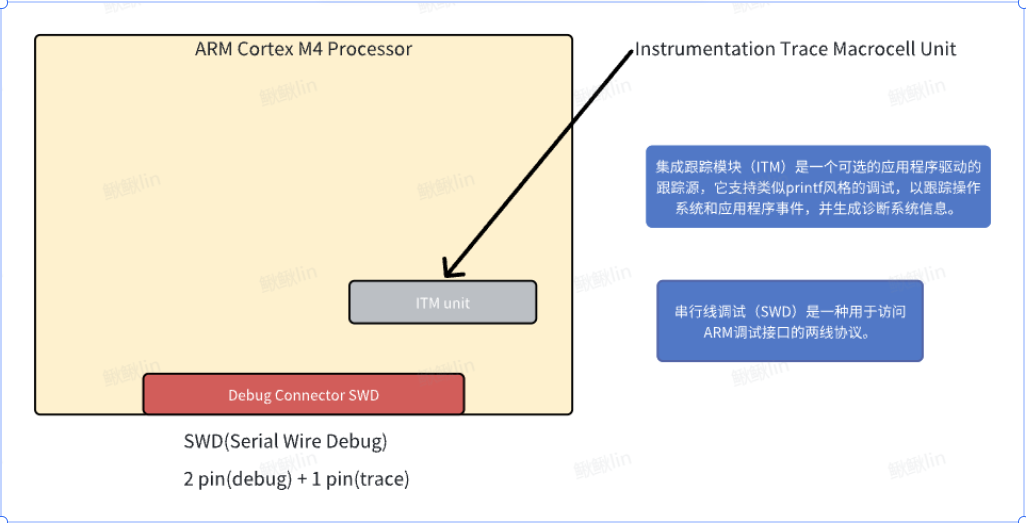

(3)SWD调试接口

cubemx里将debug设置成SWD接口,这就是SWD

-

串行线调试(SWD)是一种用于访问ARM调试接口的两线协议。

-

它是ARM调试接口规范v5的一部分,是JTAG的一种替代方案。

-

SWD的物理层由两条线组成:

-

SWDIO:一条双向数据线,主要是发送指令和数据。

-

SWCLK:由主机驱动的时钟。

-

-

通过使用SWD接口,应该能够对微控制器(MCU)的内部闪存进行编程,你可以访问内存区域、添加断点、停止/运行CPU。我们调试的过程中,点击单步运行,复位等功能就是通过SWD接口给MCU发送指令,MCU已经有相应的协议,会对这些指令进行相应的操作。

-

SWD的另一个优点是,可以使用串行线查看器来调试printf语句。

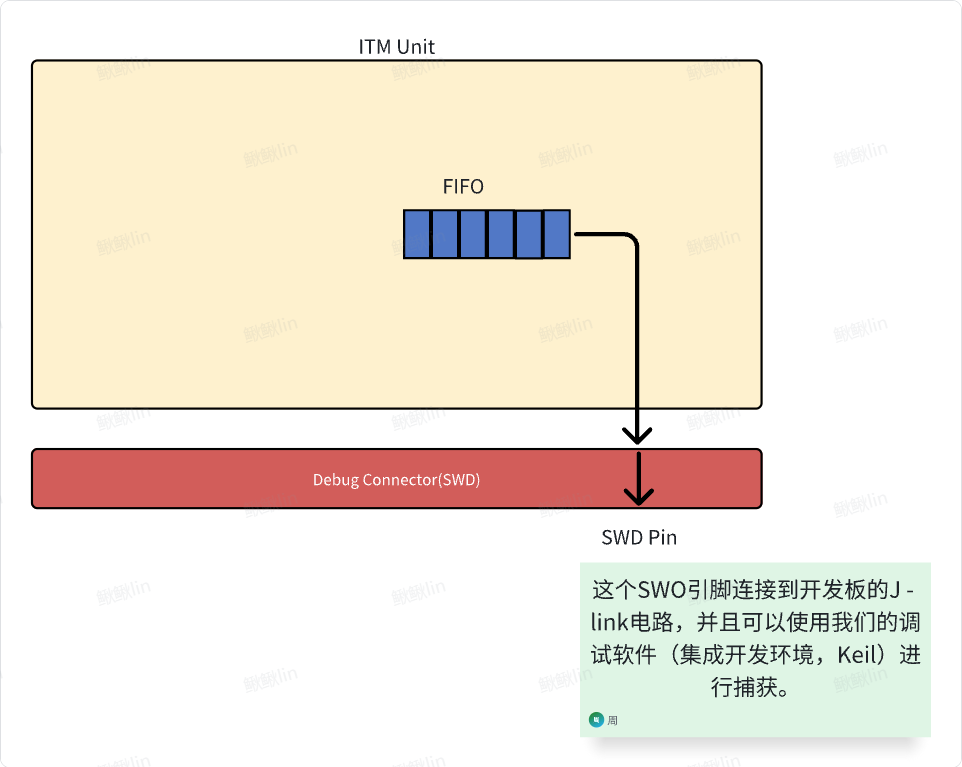

(4)ITM(Instrumentation Trace Macrocell,指令跟踪宏单元)

-

定义:Cortex-M 内核内置的调试数据生成模块。

-

作用:

-

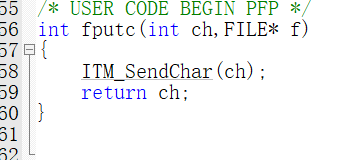

支持

printf风格的调试输出:通过重定向printf到 ITM 端口,无需占用 UART 等外设即可输出调试信息; -

提供32 个刺激端口(Stimulus Ports):不同软件可通过不同端口输出数据,方便调试主机区分多源信息;

-

内置 FIFO 缓冲:减少调试输出对程序执行的延迟影响,保证系统实时性;

-

辅助性能分析:支持事件标记(如任务切换、中断触发)、时间戳插入等功能。

-

(5)TPIU(Trace Port Interface Unit,跟踪端口接口单元)

-

定义:CoreSight 架构中数据格式化与传输的中间模块。

-

作用:接收 ITM(或其他跟踪模块,如 DWT)输出的原始数据,进行格式化处理(如适配 SWO 的编码要求),再通过 SWO 引脚将数据传输到外部调试器。是连接内核调试模块与 SWO 物理接口的 “中转站”。

(6)组件之间的联系(工作流程)

嵌入式系统运行时,各组件按以下流程协作,实现 “不暂停程序的实时调试”:

-

数据生成:

ITM生成调试数据(如printf输出、事件 / 时间戳信息),并通过内部端口发送给TPIU; -

数据处理:

TPIU对 ITM 传来的原始数据进行格式化(如编码为 SWO 支持的格式); -

数据传输:格式化后的数据通过

SWO引脚(物理通道)传输到外部调试器(如 J-Link); -

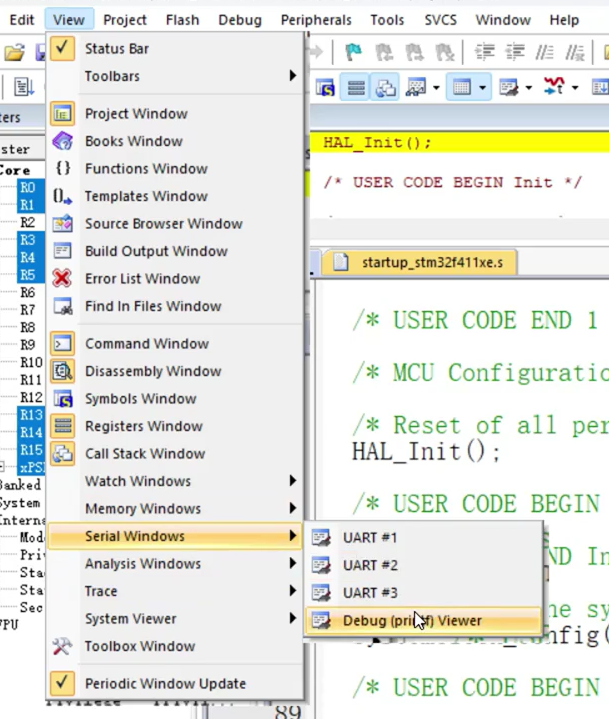

数据查看:上位机中的

SWV工具(如 Keil 的 “Debug (printf) Viewer”、IAR 的 “Terminal IO”)接收调试器转发的数据,以可视化界面展示给开发者。

简单总结:ITM是 “调试数据的生产者”,TPIU是 “数据的格式化中转站”,SWO是 “物理传输通道”,SWV是 “数据的可视化查看器”。四者共同构成一套低开销、实时性强的嵌入式调试链路。

3.ITM的使用

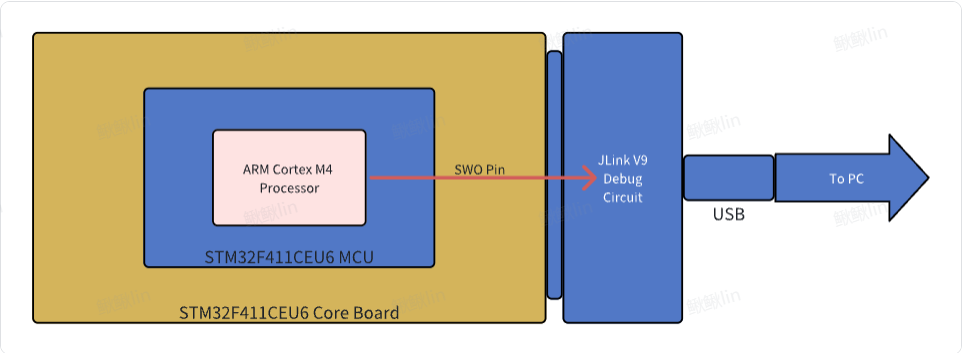

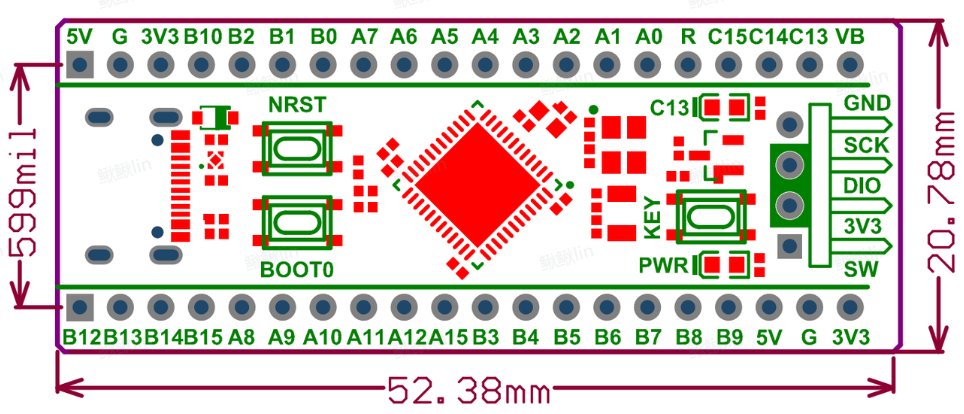

首先将f411ceu6单片机的PB3引脚和Jlink的SWO引脚进行连接

配置为trace模式要比SWD模式多出一个引脚

开启微库

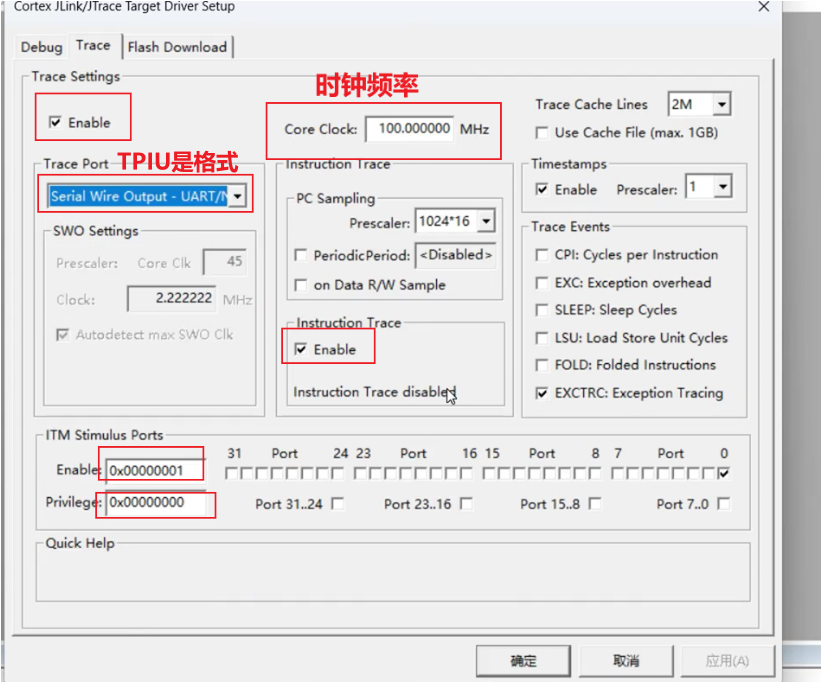

Debug选择jlink

Trace里进行相应的配置

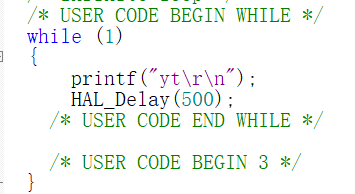

进行重定向

进行相关测试

实验现象