19.9咖啡项目:工程项目级别的IIC主从机模块

闲言碎语

知识无价,但学习有价,计划推出食品级FPGA项目系列。

* 4.9冰淇淋项目:只要少吃一个冰淇淋,就可以解锁一个 冰淇淋项目(matlab+fpga)。

* 9.9奶茶项目:只要少点一杯奶茶,就可以解锁一个奶茶项目(matlab+fpga)。

* 19.9咖啡项目:只要少点一杯咖啡,就可以解锁一个咖啡项目(matlab+fpga)。

* 29.9汉堡项目:只要少点一个汉堡,就可以解锁一个汉堡项目(matlab+fpga)。

……

目录

一、IIC协议

二、FPGA仿真验证结果

三、代码

1、百度网盘链接

IIC(Inter-Integrated Circuit,也写作I2C或I²C)总线是一种由飞利浦半导体(现恩智浦半导体)于1982年设计的同步、多主从、串行通信协议,旨在简化集成电路之间的短距离通信。其核心设计理念是通过两线制(串行数据线SDA和串行时钟线SCL)实现设备间的双向数据传输,大幅减少硬件连接的复杂性。

一、IIC协议

IIC协议使用两条双向开漏信号线进行通信:

- SCL(Serial Clock):时钟线,由主设备(Master)控制,用于同步数据传输。

- SDA(Serial Data):数据线,用于传输数据。

IIC总线支持多主多从架构,即多个主设备和多个从设备可以连接在同一总线上,通过地址识别来选择通信对象。

IIC通信由以下几个基本时序组成:

- 起始条件(START)

- SCL为高电平时,SDA从高电平跳变为低电平。

- 表示通信开始。

- 停止条件(STOP)

- SCL为高电平时,SDA从低电平跳变为高电平。

- 表示通信结束。

- 数据传输(Data Transfer)

- 数据在SCL高电平时必须保持稳定。

- SDA的变化只能在SCL为低电平时发生。

- 每个时钟周期传输1位数据,高位(MSB)先传。

- 应答信号(ACK)与非应答信号(NACK)

- 每传输完一个字节(8位),接收方在第9个时钟周期拉低SDA表示应答(ACK)。

- 若SDA保持高电平,则表示非应答(NACK),通常表示接收失败或数据传输结束。

- 从设备地址(7位或10位)

- 主设备发送的第一个字节为从设备地址(7位) + 读/写标志位(1位)。

- 例如:1010000R/W,其中R/W=0表示写,R/W=1表示读。

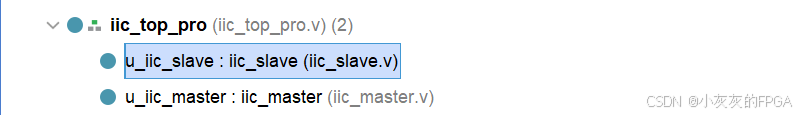

在IIC的主从机模块架构中,通过IIC的sclk和sdo将主从机进行回环测试验证。

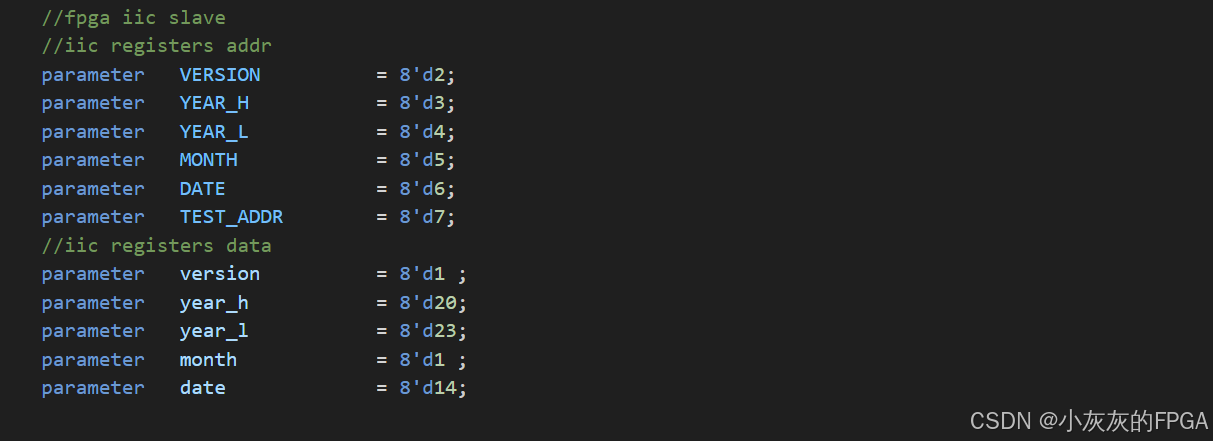

支持两种类型寄存器的配置

一是:只读IIC寄存器

通过用户自定义iic寄存器的地址以及内容,比如版本寄存器和时间寄存器,通过iic开放给主机master。此处是fpga的iic_master模块,当然也支持cpu或者arm的iic主机模块。

二是:可读可写IIC寄存器

通过iic_master模块写入iic自定义寄存器,此处用了一个test寄存器0x07,写入数据0x10。之后通过iic_master模块读取0x07寄存器,从而得到对应的数据内容为0x10。

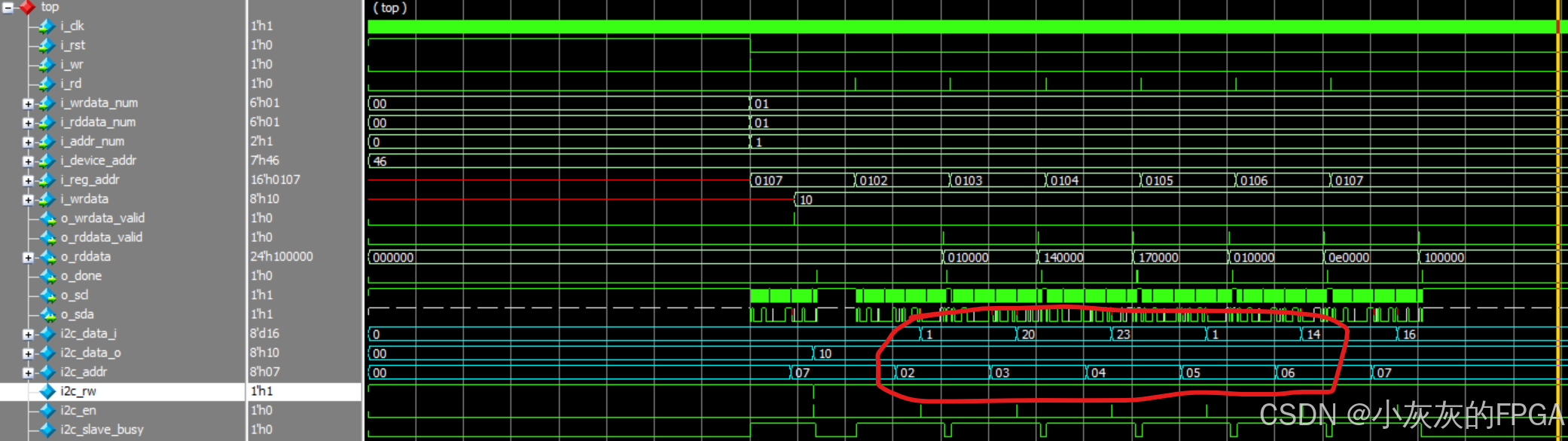

二、FPGA仿真验证结果

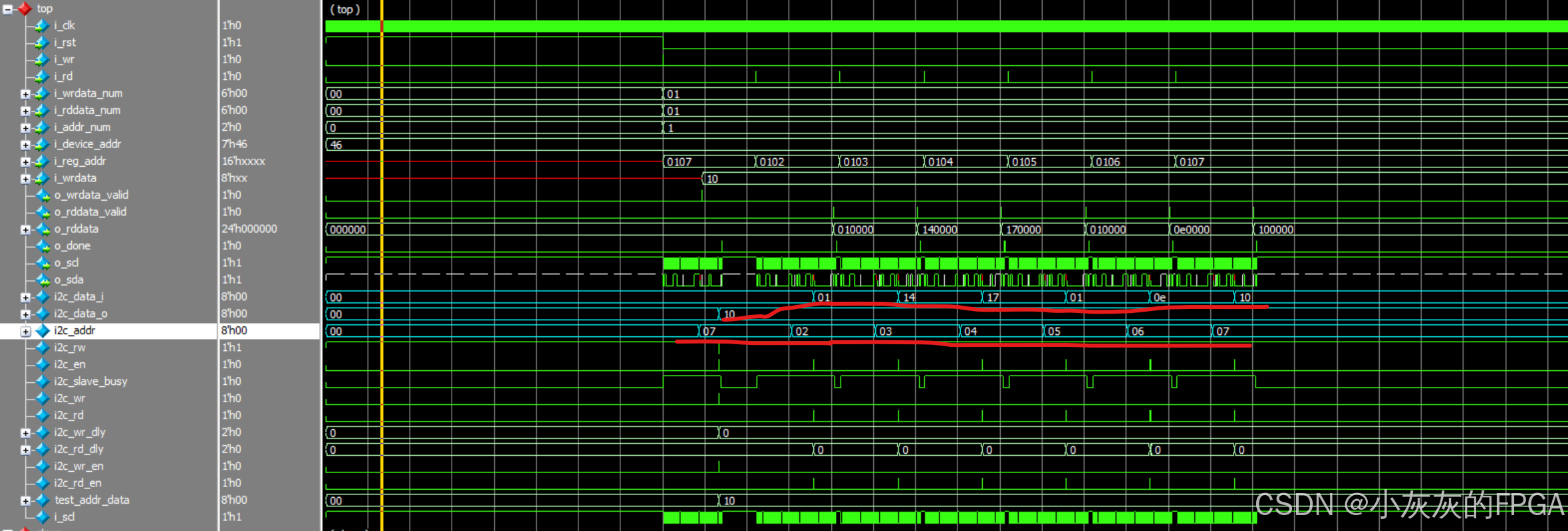

通过配置对IIC的设备地址进行同步更新,保证主从机模块的iic的设备地址一致。

通过读写控制实现iic的写操作和读操作。

通过寄存器地址数实现不同位宽的寄存器地址写入。

通过寄存器地址数实现不同位宽的寄存器数据写入。

从仿真中可以看出,写入设备地址0x46,寄存器地址0x07,寄存器内容0x10,经过一定时间读取0x07的地址内容,得到数据位0x10。

从仿真中可以看出,读取设备地址0x46,寄存器地址分别为0x02,0x03,0x04,0x05,0x06,对应的寄存器内容分别为8’d1,8’d20,8’d23,8’d1,8’d14。

与自定义的寄存器地址和内容保持一致,满足设计要求。

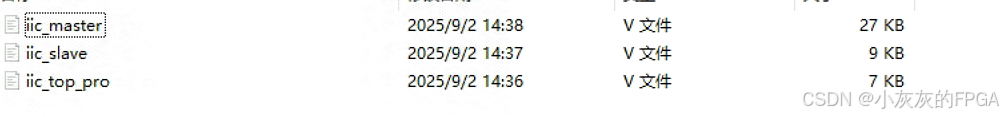

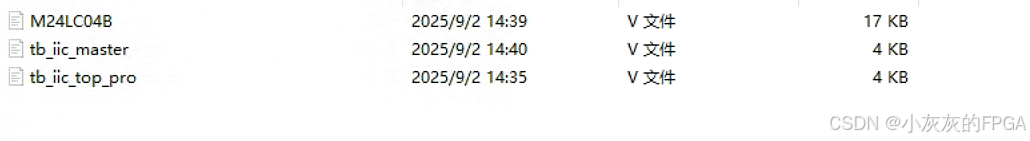

三、代码

详情见链接:

19.9咖啡项目:工程项目级别的IIC主从机模块