为什么单片机的外接晶振要并连两个电容?

电容的作用是什么?

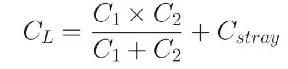

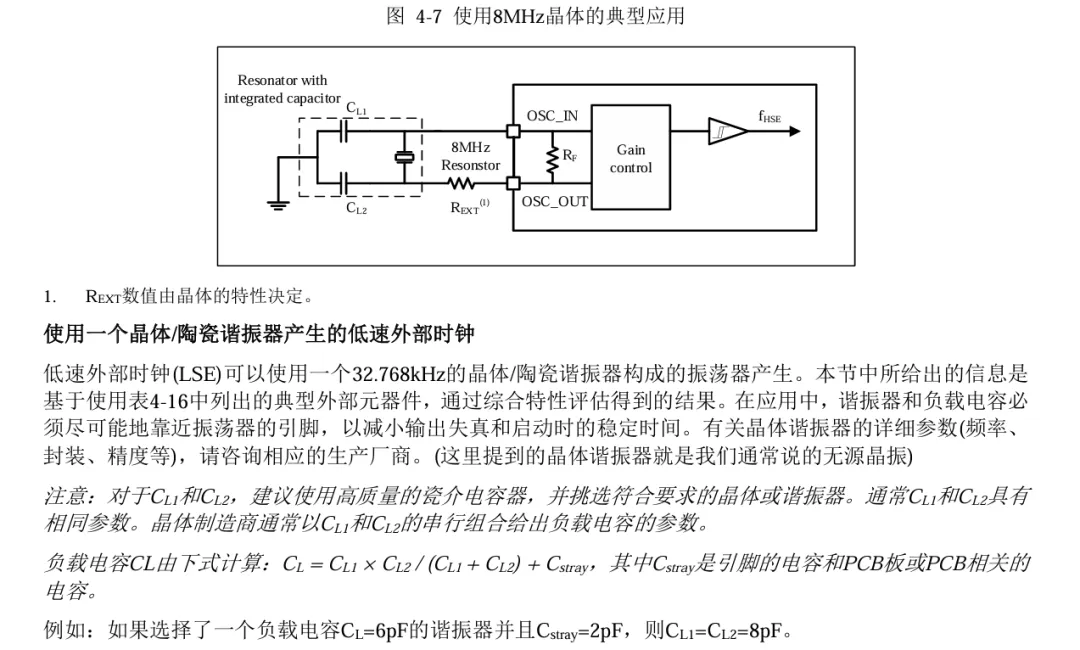

提供相移,满足振荡条件晶振是一个高Q值的谐振器,需要配合外部电路构成皮尔斯振荡器(PierceOscillator)。两个电容与晶振内部等效电容(C0)和等效电感(L)共同形成π型网络,提供180°相移,与反相放大器共同满足振荡的相位条件(总相移360°)。匹配晶振的负载电容(CL)晶振的标称频率是在特定负载电容(CL)下定义的。两个外部电容(C1,C2)与电路中的杂散电容(Cs)共同构成晶振的实际负载电容:

若实际负载电容与晶振规格书要求的CL不匹配,会导致频率偏移甚至不起振。限流保护晶振电容的容抗限制了流过晶振的电流,避免因过驱动导致晶振老化或损坏。

2.如何确定容值?

容值选择需严格参考晶振规格书,核心步骤如下:

1、查找晶振的负载电容参数(CL)晶振规格书中会明确标注负载电容(如CL=18pF或20pF)。这是设计依据。

2、估算电路杂散电容(Cstray)PCB走线、引脚寄生电容等通常为2~5pF(高频电路需精确计算或测量)。

3、计算外部电容值(C1,C2)使用公式:C1 = C2 = 2 x (CL - Cstray)举例:若晶振要求CL=20pF,Cstray=3pF,则:C1=C2=2 = 2 x (20-3) = 34pF实际可选标称值33pF或36pF。

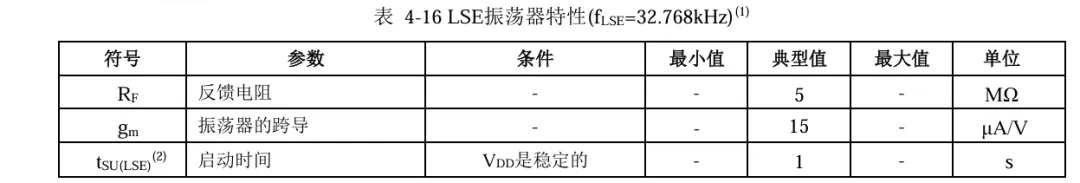

4、常见取值参考:低频晶振 (32.768kHz) :常用12.5~18pF·中高频晶振 (4~48MHz) :常用18~33pF高频/低功耗场景:可能需5~10pF注意:若频率仍不准确,需用频谱分析仪/频率计测量并微调电容值。

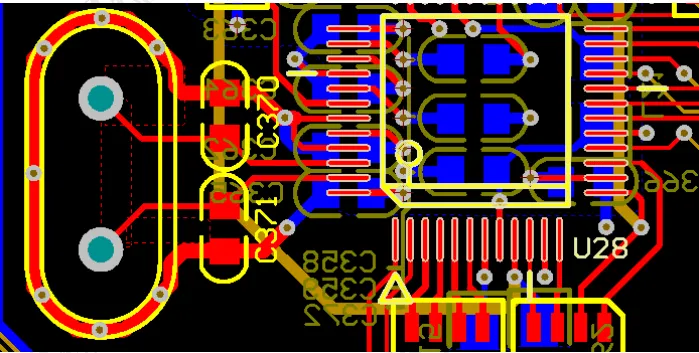

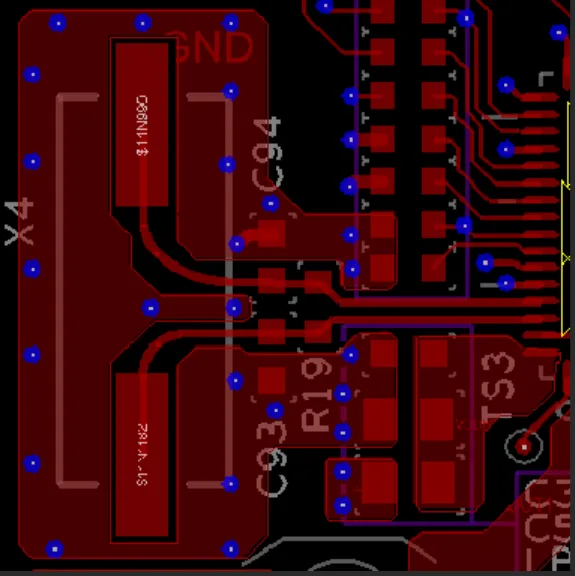

3.晶振电路布局要点?

最短走线原则晶振 (X1)、电容 (C1/C2)、单片机OSC引脚组成的小环路面积最小化(通常<1cm2),减少天线效应和EMI辐射。电容紧靠晶振引脚C1和C2分别直接连接到晶振的两个引脚(无过孔),接地端就近打孔到地平面。远离干扰源远离电源、电机、高速信号线(如USB、时钟线),避免耦合噪声。地平面屏蔽晶振下方铺设完整地平面,并在周围布置接地铜箔围栏(Guard Ring),形成法拉第笼。避免过孔分割走线信号路径禁用过孔(增加电感),必要时在晶振下方挖空其他层(防止寄生电容)

常见问题与解决·不起振:检查CL匹配、电容焊接、晶振损坏、布局环路过大。·频率偏移:测量实际频率,调整C1/C2(可并联小电容微调)。·温漂大:选择高精度晶振,避免电容使用Y5V材质(选NPO/COG)。总结:两个电容是晶振稳定振荡的“黄金搭档”,需精确匹配晶振的负载电容要求,并通过紧凑布局避免干扰。设计时务必以晶振规格书为准,结合实测优化参数。

总结

单片机外接晶振并联的两个电容(通常称为负载电容)是晶振电路正常、稳定。