半导体制造常提到的Fan-Out晶圆级封装是什么?

"Fan Out"晶圆级封装(Fan-Out Wafer-Level Packaging,简称FOWLP)是一种半导体封装技术,它允许在芯片的边界之外进行更多的I/O布线,从而提高了I/O密度,减小了封装尺寸,同时也改善了电性能。

在传统的晶圆级封装(WLP)中,芯片的连接点(或称为I/O点)是直接在芯片的表面上。但是,随着半导体技术的发展,芯片的尺寸越来越小,而I/O点的数量却越来越多,这使得在芯片表面上找到足够的空间来放置所有的I/O点变得越来越困难。

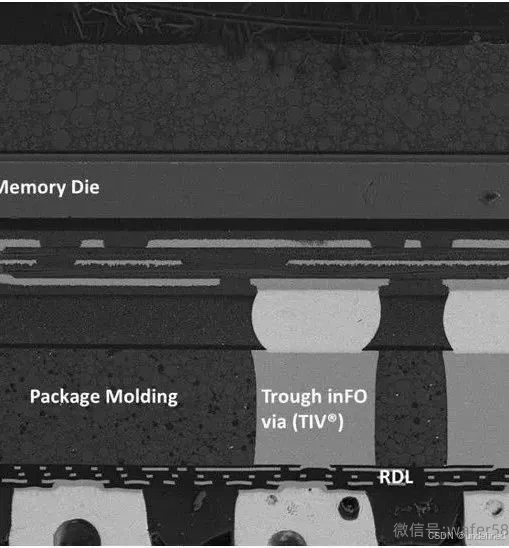

FOWLP技术解决了这个问题。在FOWLP中,芯片首先被放置在一个更大的载体(通常是一个晶圆)上,然后通过一层重分布层(RDL)将芯片的I/O点连接到载体的表面。这样,I/O点就可以“扇出”到芯片的边界之外,从而实现更高的I/O密度。

FOWL分别有三种工艺形式:face-up,face-down,RDL-fist.

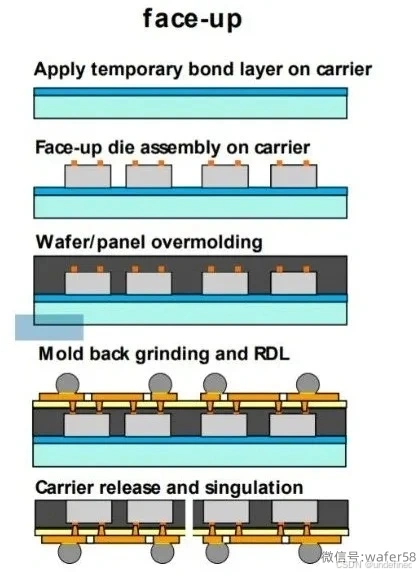

face-up(面朝上):

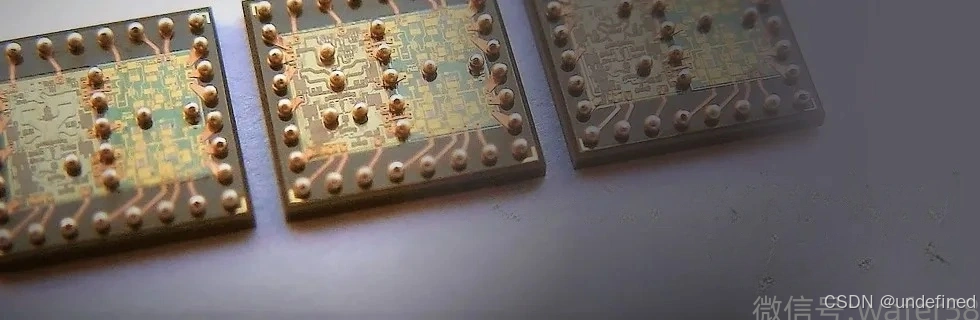

面朝上(Die-Up)的Fan-Out Wafer-Level Packaging(FOWLP)是一种常见的封装工艺。在这个工艺中,半导体芯片(die)是面朝上放置在载体上的。以下是面朝上FOWLP工艺的基本步骤:

1.芯片放置:首先,将半导体芯片面朝上放置在一个临时载体(通常是晶圆)上。

2.模塑:然后,使用模塑材料(通常是环氧树脂)将芯片和载体封装在一起。这个步骤可以提供机械支撑,同时也可以保护芯片。

3.重分布层(RDL)制作:接下来,通过光刻和电镀等工艺在模塑材料上制作重分布层。RDL可以将芯片的I/O点连接到载体的表面,从而实现I/O点的“扇出”。

4.焊球附着:然后,通过焊球附着(Ball Attach)工艺在RDL上形成焊球。这些焊球可以用于将封装后的芯片连接到电路板上。

5.去载体:最后,通过一种叫做去载体(Debonding)的工艺将封装后的芯片从临时载体上移除。

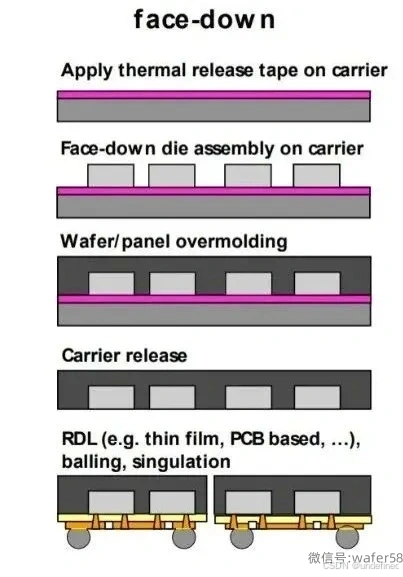

face-down(面朝下)

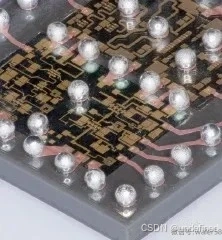

面朝下(face-Down)的Fan-Out Wafer-Level Packaging(FOWLP)是另一种常见的封装工艺。在这个工艺中,半导体芯片(die)是面朝下放置在载体上的。以下是面朝下FOWLP工艺的基本步骤:

- 芯片放置:

- 模塑

- 去载体

- 重分布层(RDL)制作:

5,焊球附着

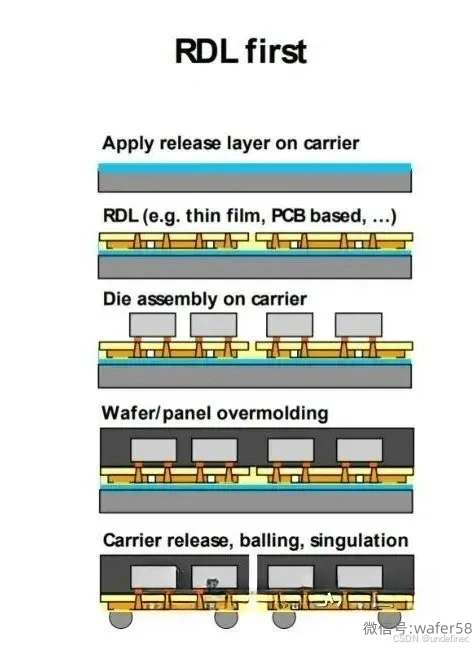

RDL-fist:

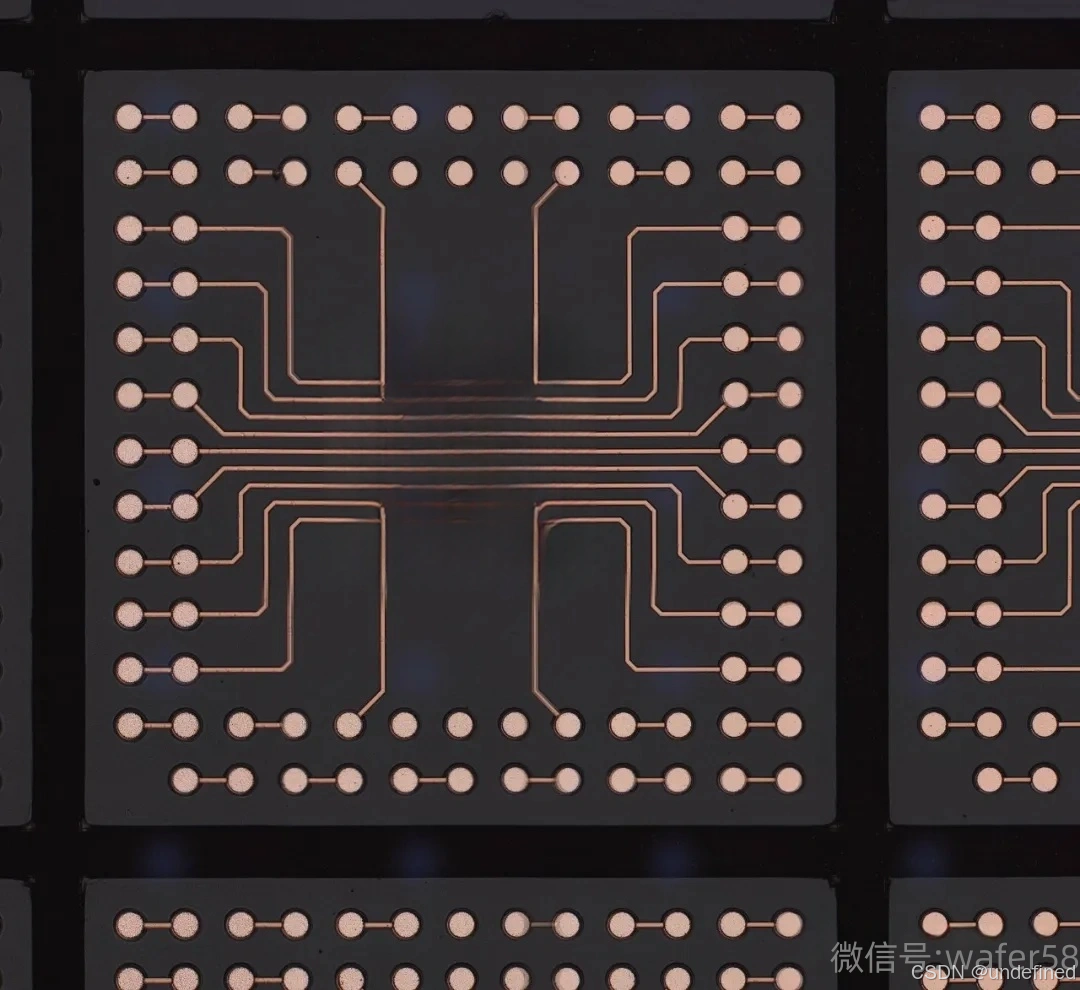

RDL-first(重分布层先行)是Fan-Out Wafer-Level Packaging(FOWLP)的一种工艺流程。在这个工艺中,重分布层(RDL)是在芯片放置之前制作的。以下是RDL-first FOWLP工艺的基本步骤:

- 重分布层(RDL)制作

- 芯片放置

- 模塑

- 去载体

5,焊球附着

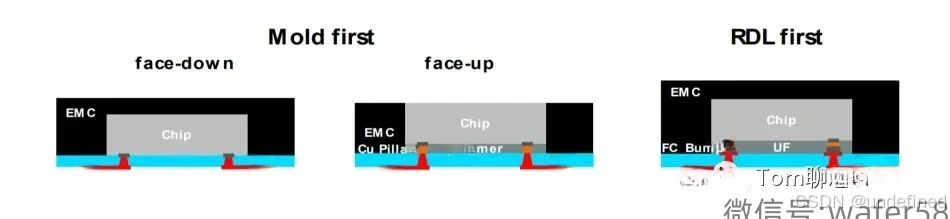

这些不同的方法提供了不同的成本和性能权衡。在成本方面,先开模面朝下的方式避免了制作铜柱和背面研磨的需要,因此制作成本较低。它最适合低 I/O 数量的情况;然而,芯片偏移、晶圆翘曲等问题限制了其在复杂多芯片封装中的应用。

面朝上的方法减少了这些问题,并且在热管理方面具有优势,因为芯片背面完全暴露,有助于散热。

在性能上,面朝下的方法比其他两种方法具有更短的连接路径。这两种方法都使用铜柱将连接延伸到 RDL,并在芯片下方增加了一层材料,增加了连接之间的寄生电容,从而影响了它们的高频性能。

转载需注明出自本处。