硬件 - RK3588部分(2) - 原理图 - 最小系统

目录

一、最小系统设计

1.1 时钟电路

1.1.1 高速时钟

1.1.2 低速时钟

1.1.3 RK3588S为外设提供时钟(记得电平要匹配)

1.2 复位/看门狗/TSADC电路

1.2.1 复位部分

1.2.2 看门狗

1.2.3 TSADC

1.2.4 双PMIC方案

1.3 PMU单元电路

1.4 系统启动引导顺序

1.5 系统初始化配置信号

1.6 JTAG和UART Debug电路

1.6.1 JTAG

1.6.2 UART Debug

1.7 DDR电路

1.7.1 DDR控制器介绍

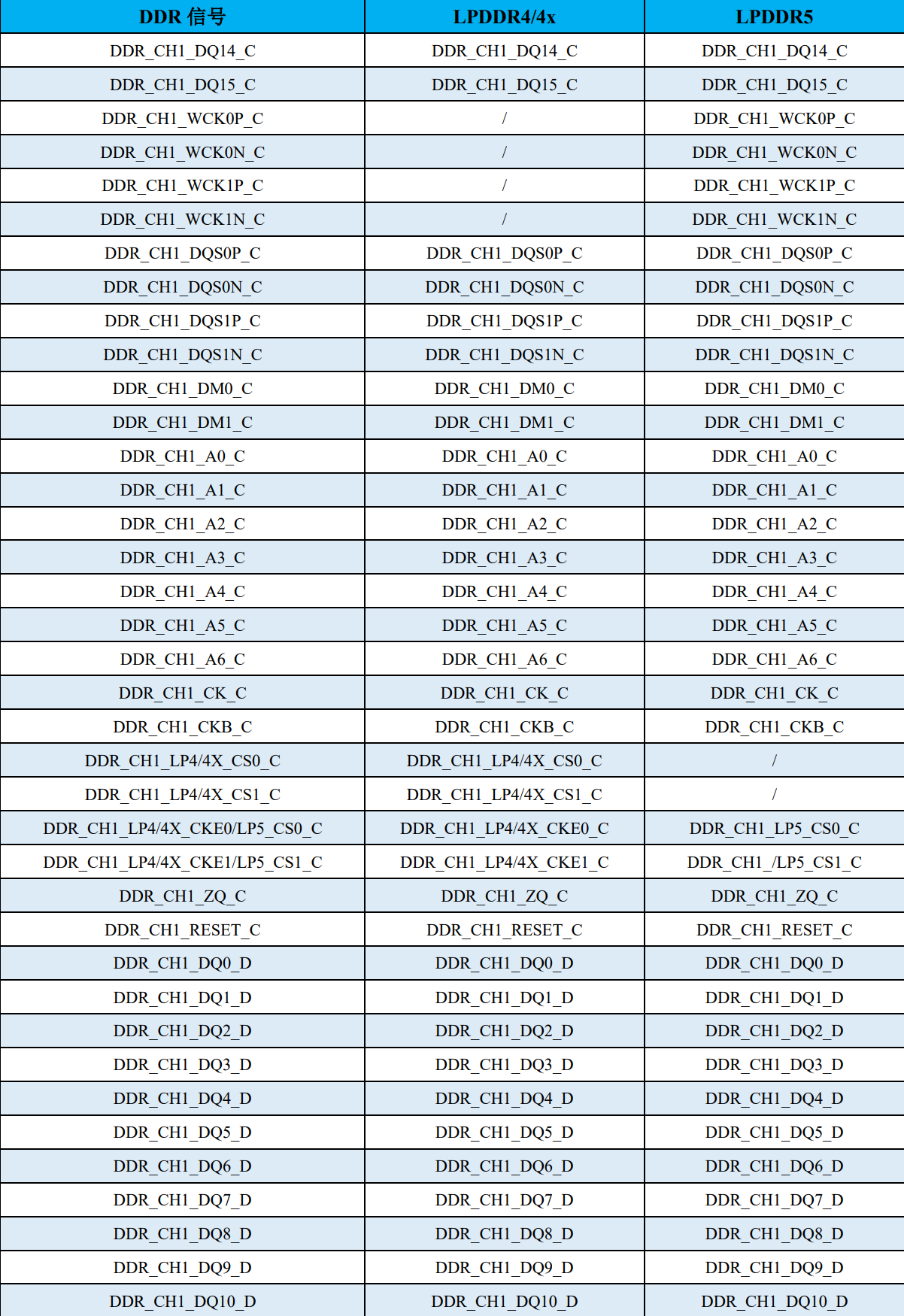

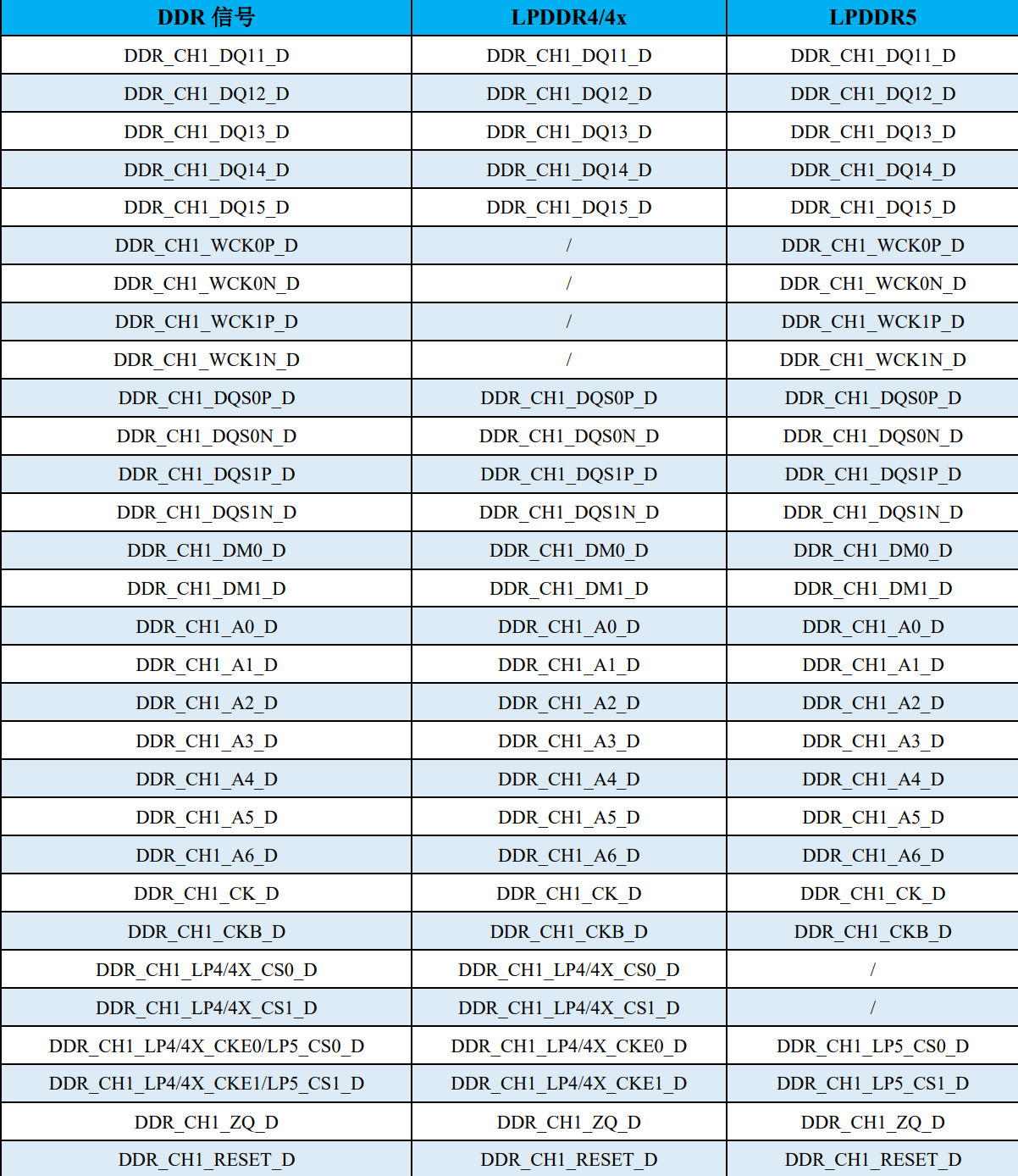

1.7.2 RK3588S DDR PHY IO Map表

1.7.3 LPDDR时的注意点

1.7.4 DDR颗粒外围电路设计

1.7.5 DDR拓扑结构和匹配方式设计

1.7.6 DDR电源设计和上电时序要求

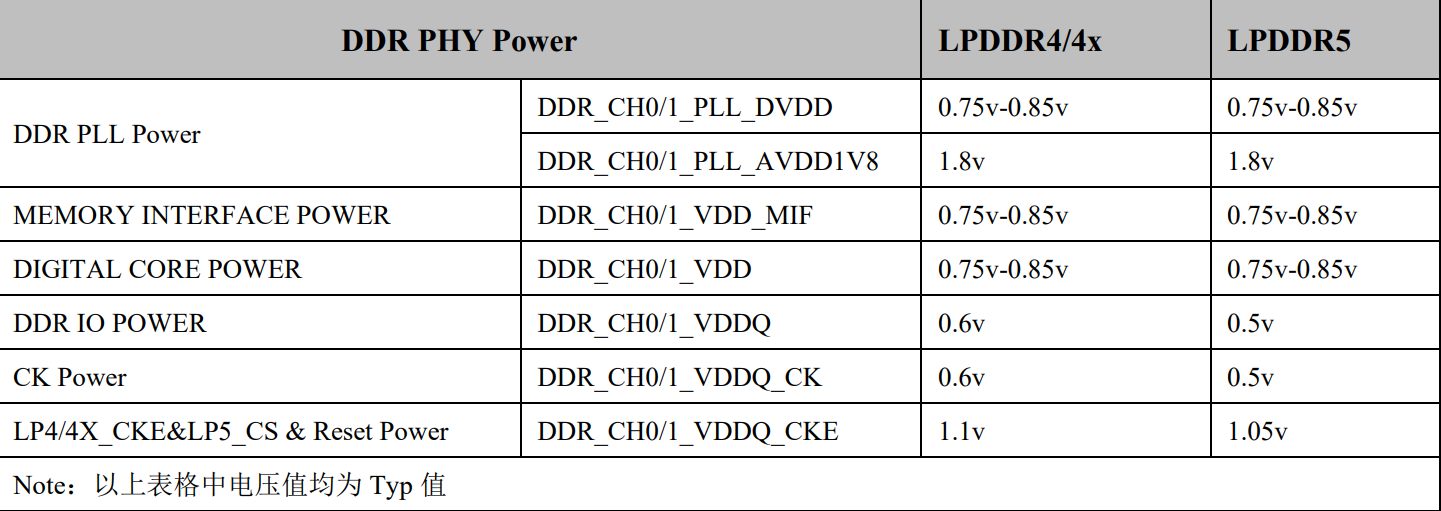

1.7.6.1 DDR PHY 供电电源

1.7.6.2 LPDDR4/4x/5 颗粒供电电源

1.7.6.3 双PMIC电源方案供电

1.7.6.4 单PMIC电源方案供电

1.7.6.5 LPDDR4和LPDDR4x 的电源选择

1.7.6.6 上电时序要求

1.7.6.7 RK3588S DDR颗粒支持列表

1.8 eMMC电路

1.8.1 eMMC控制器介绍

1.8.2 eMMC电路设计建议

1.8.3 eMMC上电时序

1.8.4 eMMC支持的型号

1.9 FSPI Flash电路

1.9.1 FSPI Flash 接口介绍

1.9.2 FSPI Flash电路设计

1.9.3 SPI Flash支持型号

1.10 GPIO电路

1.10.1 电平类型

1.10.2 IO口说明

1.10.3 GPIO驱动能力

1.10.4 GPIO电源

一、最小系统设计

1.1 时钟电路

1.1.1 高速时钟

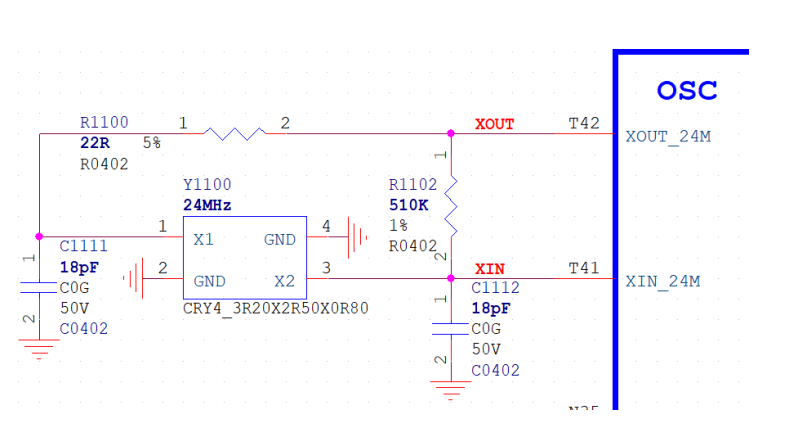

电路

RK3588S系统时钟由内部振荡与外置24Mhz晶振组成;

XOUT_24M 外面那个22R的电阻要留着,用于限流,防止过驱;

XOUT和XIN之间 510KR 的电阻的阻值不要去动;

晶振选取

1.晶振的CL值不要超过12pF;

2.CL电容常温频率容限在20ppm以内;

3.下方原理图中晶振的GND记得要接,加强时钟抗ESD干扰能力;

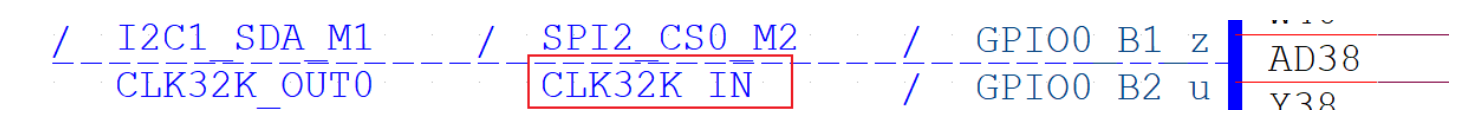

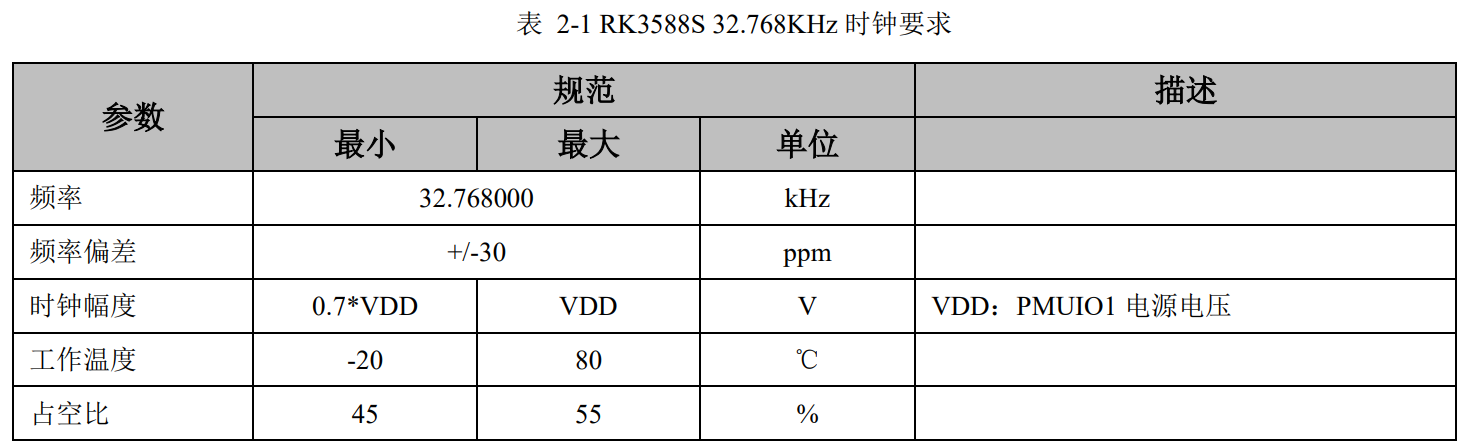

1.1.2 低速时钟

关于低功耗:

在RK3588S待机的时候,可以把时钟源切换到PMU_PVTM模块提供的,或者外置的32.768Khz时钟,从而关断内部OSC振荡电路,从而优化功耗。这时候仅支持PMUIO1和PMUIO2电源域里的IO中断唤醒;

假如PVTM模块也要关掉,那就直接用外部32.768Khz时钟源;

1.1.3 RK3588S为外设提供时钟(记得电平要匹配)

REFCLK_OUT:预留时钟输出引脚;

CLK32K_OUT0:32.768K时钟输出,一般给WIFI,BT,PCIe做休眠用的;

ETH1_REFCLKO_25M:25Mhz时钟输出,给Ethernet PHY 当工作时钟;

GMAC1_CLKINOUT:50Mhz,125Mhz的输入输出时钟,给Ethernet PHY作为RMII数据发送接收参考时钟;

MIPI_CAMERA0_CLK ~ MIPI_CAMERA4_CLK:24Mhz时钟输出,给相机当工作时钟用的,这个也可以靠PLL分频获得其它频率,这四路不必相同;

CIF_CLKOUT:24Mhz输出,给相机当工作时钟;

PCIE20_REF_CLKP/N:输入输出100Mhz,给PCIE2.0用的;

1.2 复位/看门狗/TSADC电路

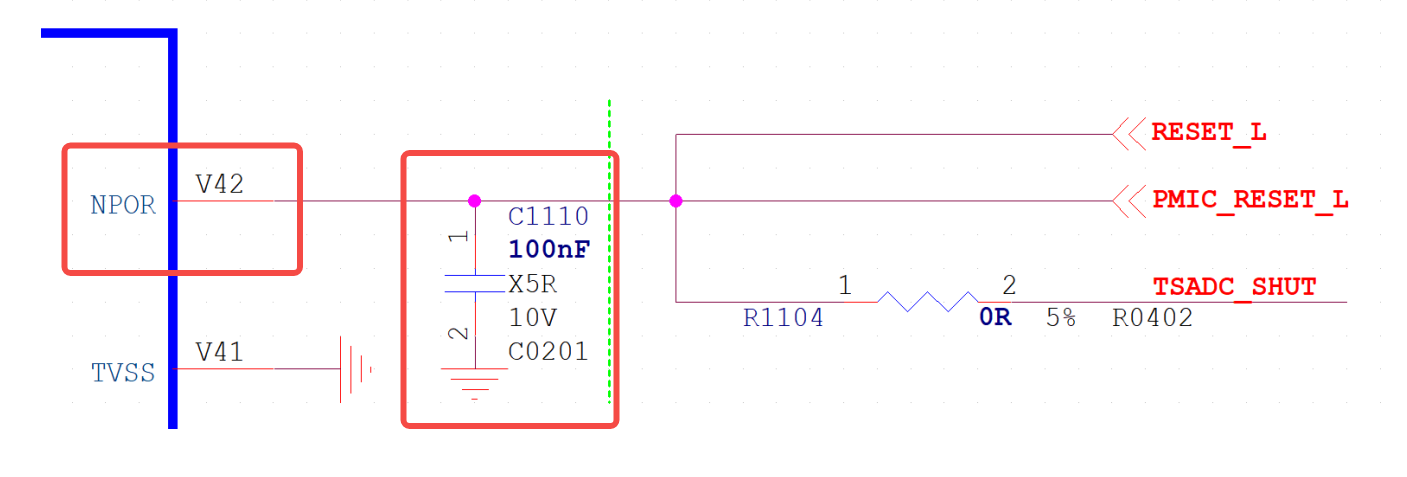

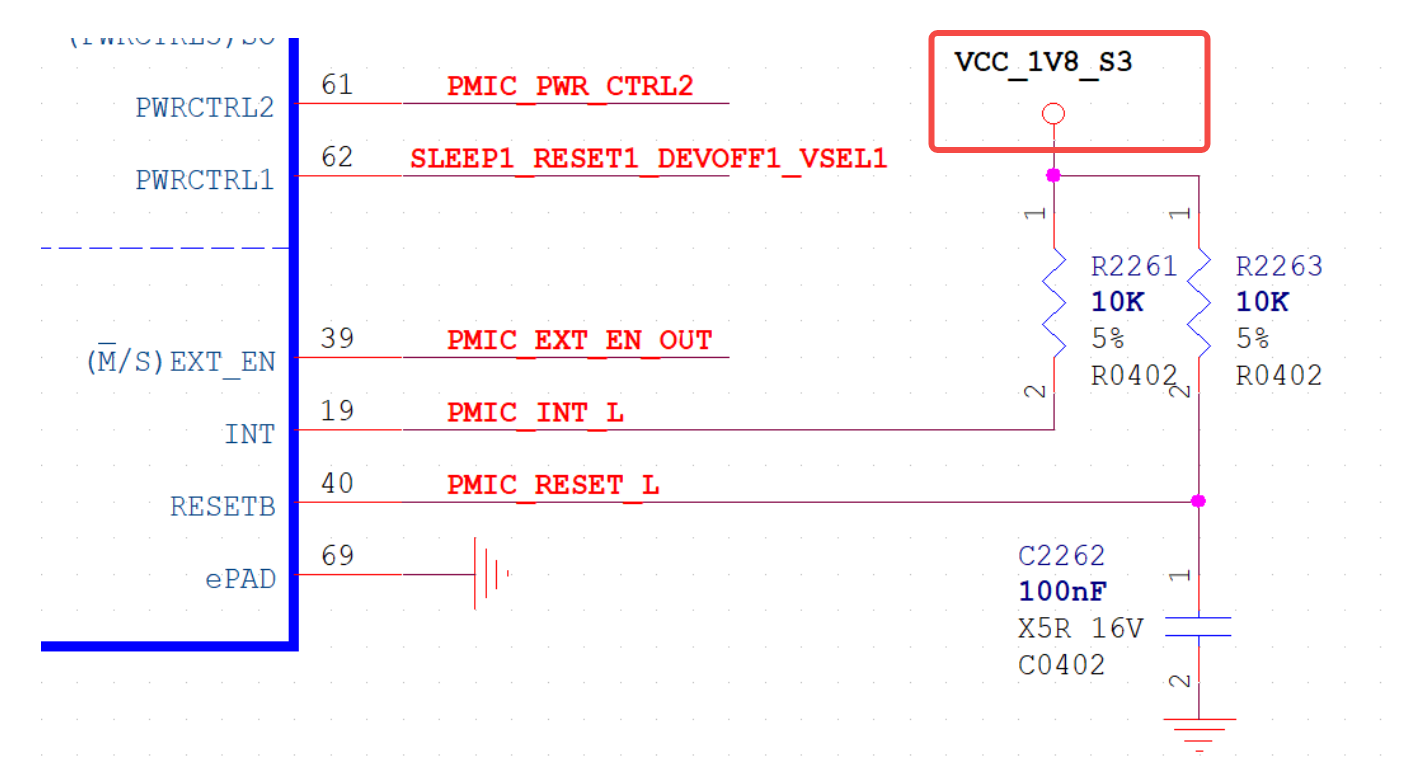

1.2.1 复位部分

RK3588S的硬件复位通过 PinV42(NPOR) 输入控制,低电平有效,所需最短复位时间为100个24Mhz主时钟周期,也就是至少4us以上;

PinV42(NPOR) 引脚需要加一个0.1uF电容来防抖;

RESET_L的上拉电源,需要和NPOR所在的电源域一致 PMUIO1_1V8;

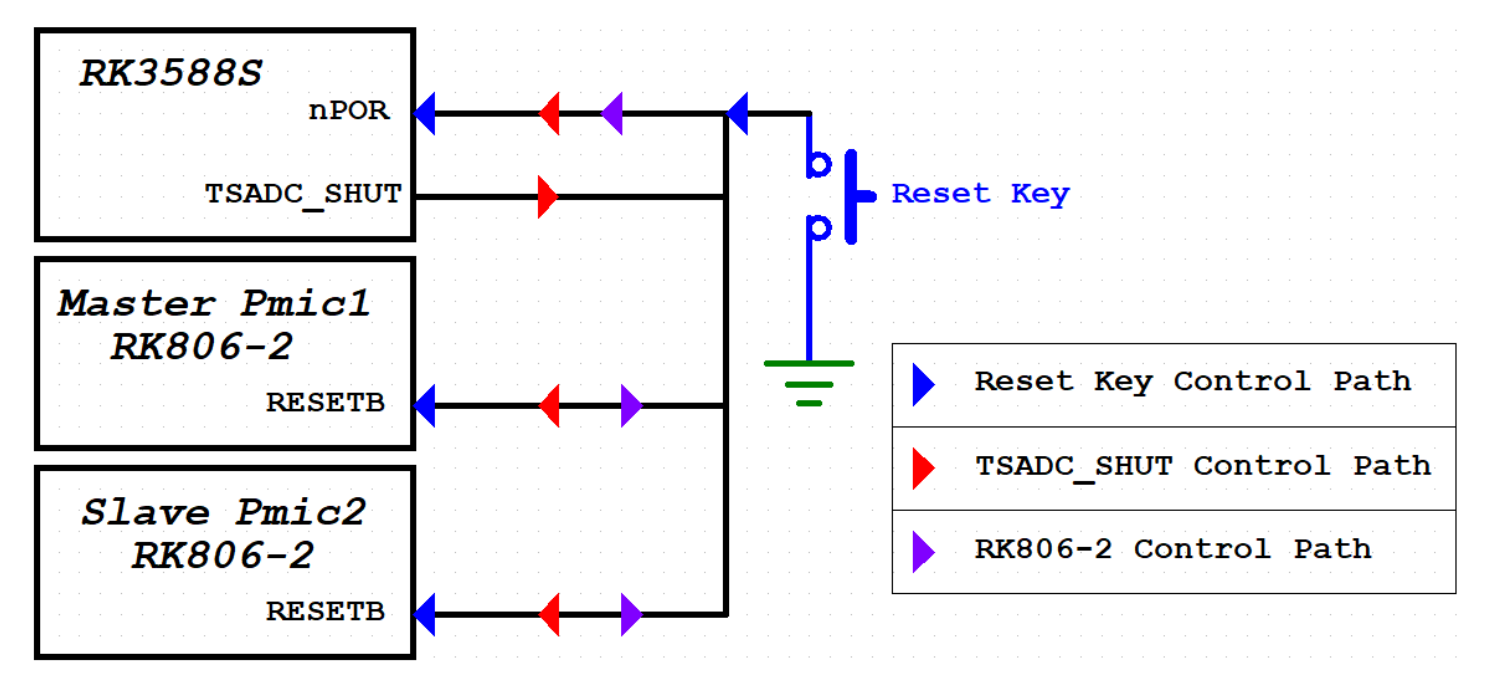

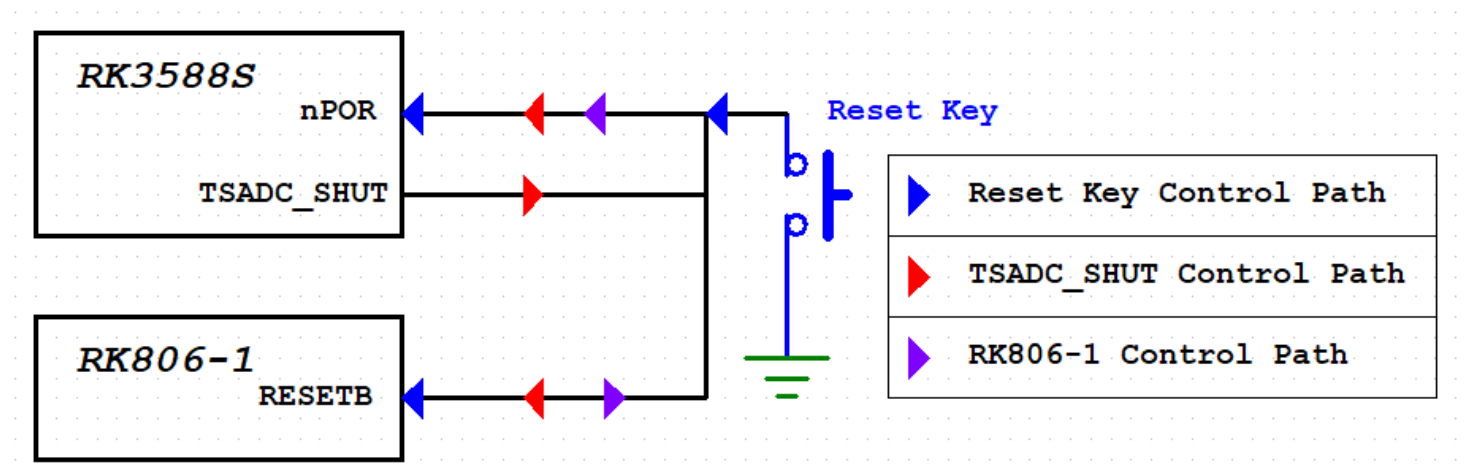

1.2.2 看门狗

RK3588S的Watchdog Timer 产生的复位信号,是从TSADC_SHUT引脚输出低电平,从而对RK3588进行硬件复位;

1.2.3 TSADC

也就是 Temperature-Sensor ADC模块,防止芯片内部过温的,

当过温时,内部 TSHUT信号给到 CRU模块,然后让芯片复位;

或者是通过 TSADC_SHUT 输出低电平,硬件复位;

1.2.4 双PMIC方案

对比的单PMIC

PMIC是Power Management Integrated Circuit(电源管理集成电路)主要功能是:

1.电压转换,因为设备需要多种电源域;

2.时序控制,因为不同模块对上电顺序有一些要求的;

3.充电管理;

4.功耗控制;

5.电源保护,比如OVP、OCP、OTP、SCP那些的;

比如RK806就是PMIC,RK806的RESETB引脚在第一次上电时,各路电源上电完成后,RESETB会在经过设定的延时后,再从低电平变高,完成上电复位;如果RK806在工作或者SLEEP模式时,RESETB引脚被拉低,那么RK806也会重启;

1.3 PMU单元电路

RK3588S有个PMU(电源管理单元),用于控制管理芯片内部电源;

该模块可以支持芯片内部寄存器,或者PMUIO电源域的IO控制外围电源电路,使其对其他功能模块供电、断电;

也可以支持IO中断唤醒,实现芯片待机、唤醒功能;

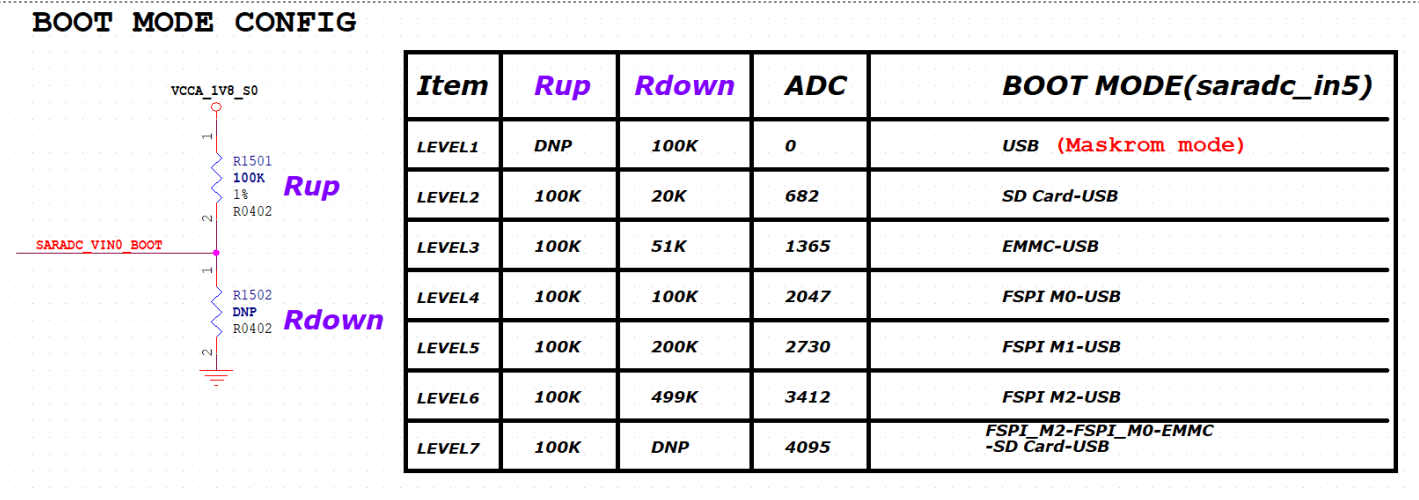

1.4 系统启动引导顺序

芯片复位结束后,内部引导代码可以从下列设备从加载系统引导代码,重启系统:

1.Serial Flash(FSPI):串行闪存;2.eMMC:嵌入式多媒体卡;

3.SD/MMC Card:SD卡或者MMC卡;

如果这些设备都没引导代码,可以用USB2.0OTG0口,也就是TYPEC0_USB20_OTG_DP和TYPEC0_USB20_OTG_DM把代码下进去;

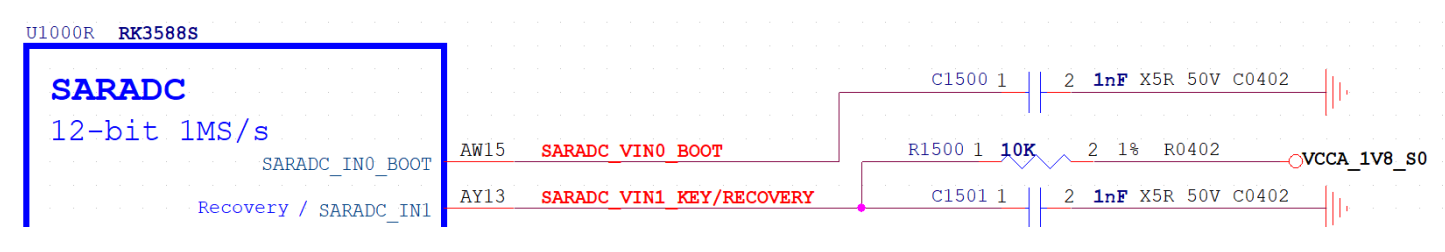

引导顺序选择:Boot启动顺序可以通过SARADC_IN0_BOOT(PIN A W15)进行设置

这里是使用LEVEL1设置,SARADC_IN0_BOOT接地,SARADC_IN1用于接地时进入Recovery状态;

USB(Maskrom mode)这是一种强制通过 USB 接口烧写固件的模式,当芯片无法从其他存储设备(如 eMMC、SD 卡、SPI Flash 等)正常引导时(比如新芯片无任何启动代码、原有固件损坏),可通过 USB 连接电脑,用专用工具强制烧写系统镜像。

SD Card-USB

优先从 SD 卡 加载引导程序;如果 SD 卡中没有有效的引导代码,则尝试通过 USB 接口加载。

适合开发调试阶段,可通过 SD 卡快速测试不同版本的系统,若 SD 卡未准备好,也能临时用 USB 烧写。

EMMC-USB优先从 eMMC(嵌入式多媒体卡,常见于手机、平板等设备的内置存储)加载引导程序;若 eMMC 无有效引导代码,再尝试 USB。

量产设备常用(eMMC 是内置大容量存储,适合存储完整系统),保证量产设备从内置存储稳定启动,同时保留 USB 应急烧写的可能。

FSPI M0-USB优先从 FSPI(四通道串行闪存接口) 连接的 M0 闪存设备 加载引导程序;若 M0 无有效代码,再尝试 USB。

FSPI 闪存(如 SPI Nor Flash)常用于存储小型引导程序(体积小、启动快),适合对启动速度有要求,且需保留 USB 调试的场景。

FSPI M1-USB

优先从 FSPI 连接的 M1 闪存设备 加载引导程序;若 M1 无有效代码,再尝试 USB。

类似 LEVEL4,但指定从 FSPI 的 M1 设备引导,可用于多闪存设备的区分(比如不同功能的引导分区存在不同闪存)。

FSPI M2-USB优先从 FSPI 连接的 M2 闪存设备 加载引导程序;若 M2 无有效代码,再尝试 USB。

与 LEVEL4/5 逻辑一致,只是引导设备指向 FSPI 的 M2。

FSPI_M2-FSPI_M0-EMMC -SD Card-USB引导优先级依次为:FSPI M2 设备 → FSPI M0 设备 → eMMC → SD 卡 → USB。

提供了 “多设备依次尝试” 的最完整优先级,确保在多种存储设备存在时,按预设顺序逐个尝试引导,最大程度保证系统能从有效设备启动。

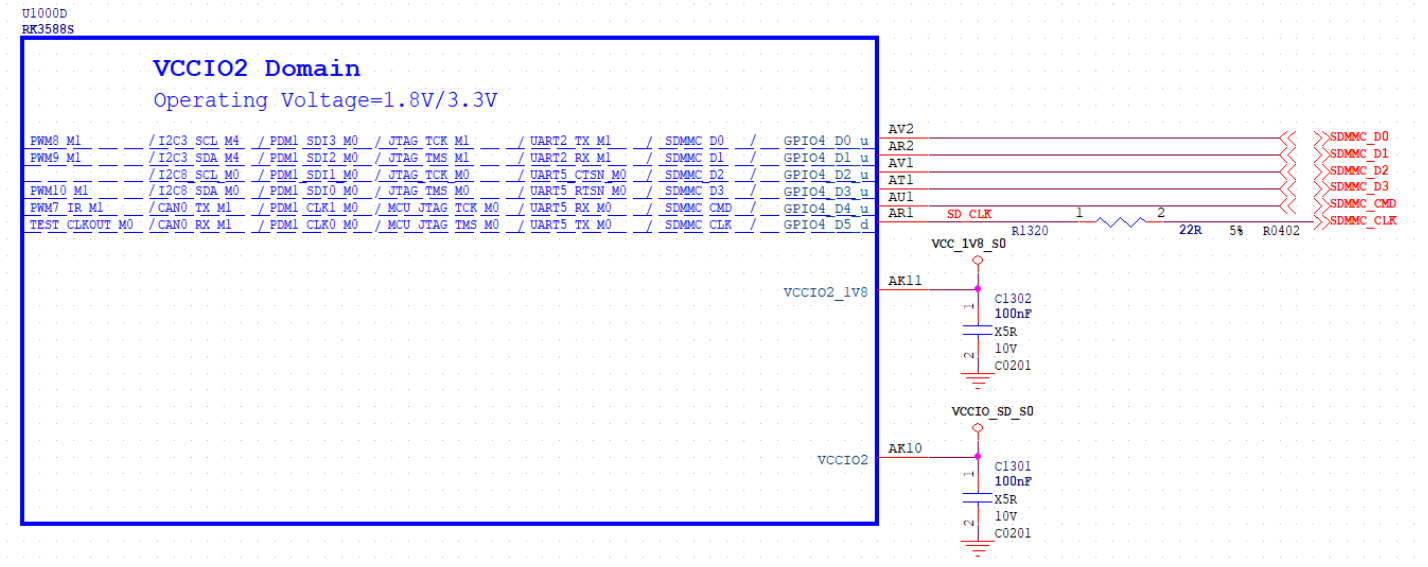

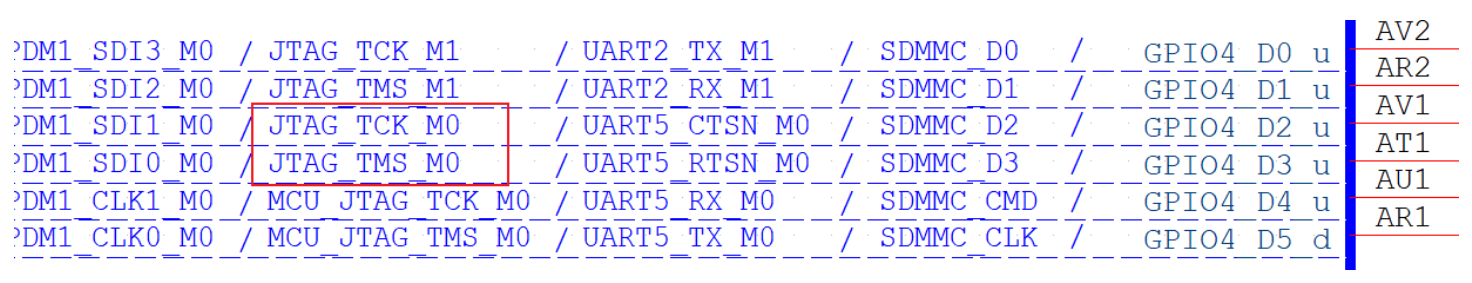

1.5 系统初始化配置信号

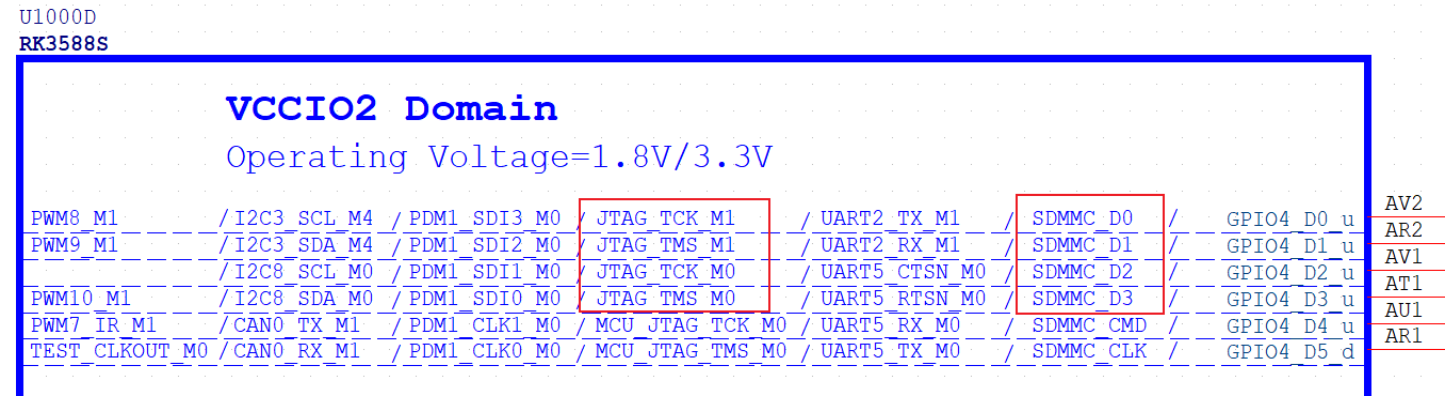

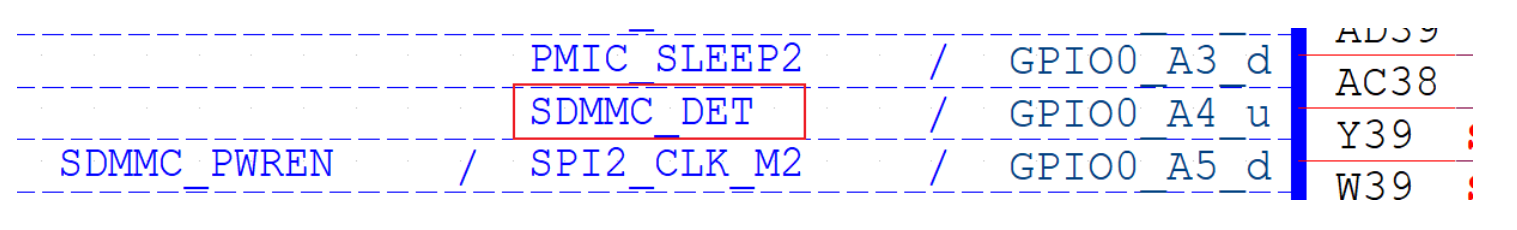

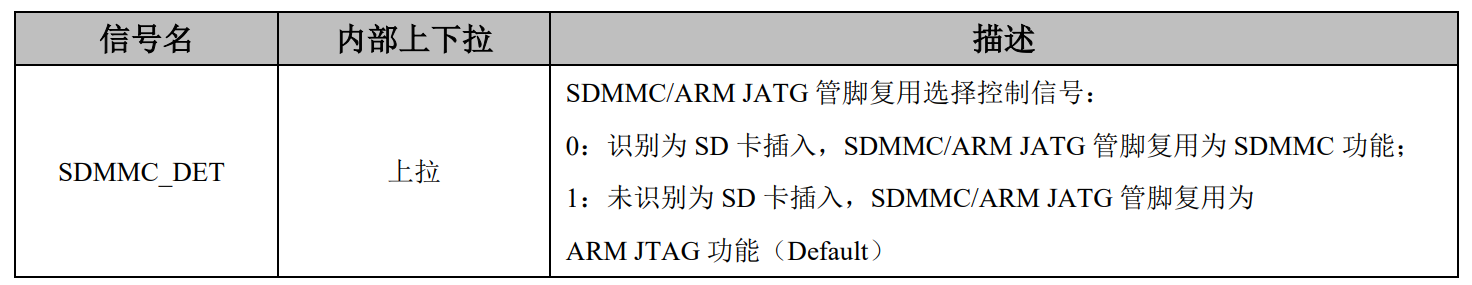

SDMMC_DET(PIN AC38):决定了VCCIO2电源域IO是SDMMC还是JTAG功能;

系统复位后,会检测这个脚电平,从而判断是ARM JTAG功能,还是SDMMC功能;

内部上拉,因为SD卡一般有个接入检测,SD卡插入后该脚低电平,自动切换为SDMMC功能;

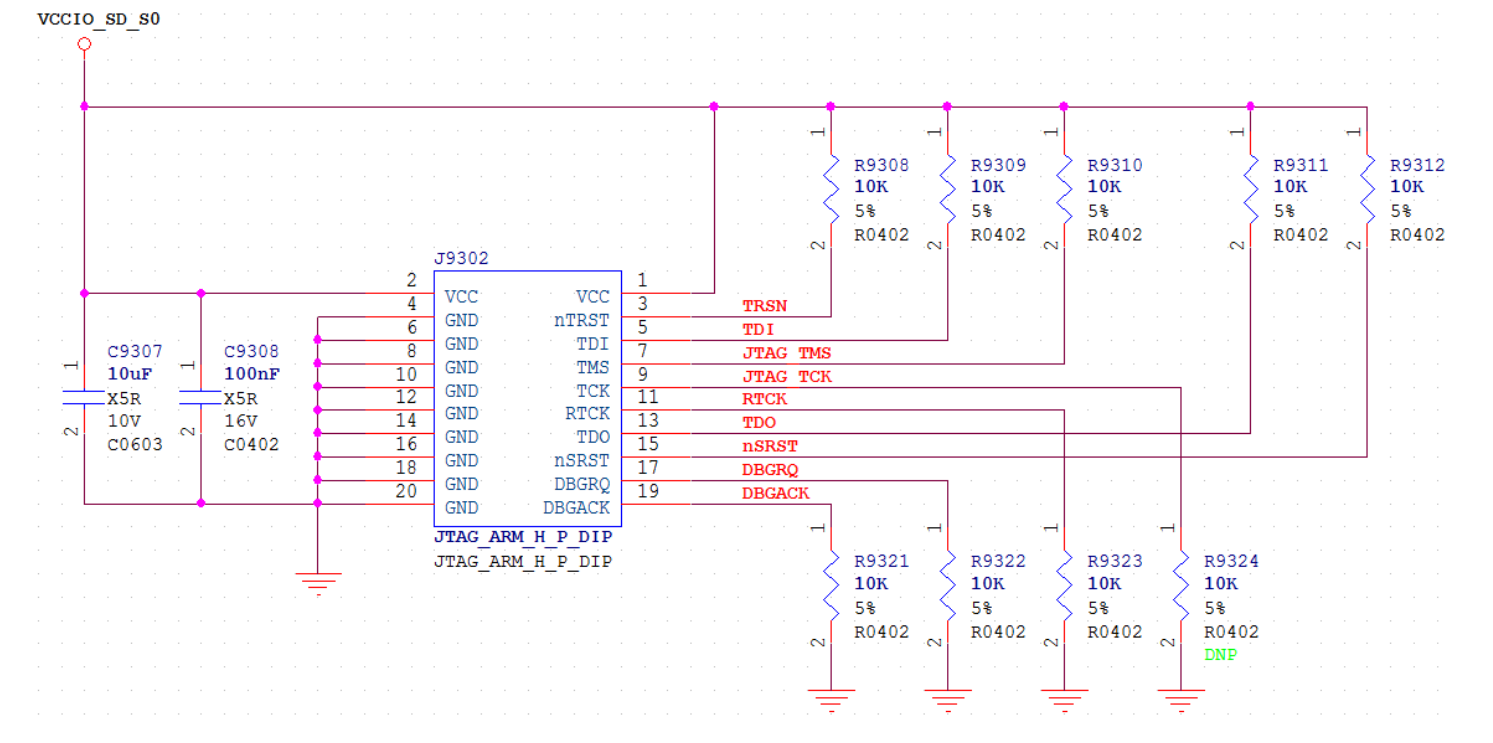

1.6 JTAG和UART Debug电路

1.6.1 JTAG

ARM JTAG接口符合IEEE1149.1标准;

要接仿真器的时候,需要把“1.5 系统初始化配置信号”那里说的SDMMC_DET引脚拉高;

系统起来后,会切换成寄存器控制IOMUX;

JTAG_TCK_M0/M1 是SWD模式时钟输入,

JTAG_TMS_M0/M1 是SWD模式数据输入输出;

预留JTAG功能时,VCCIO2_1V8和VCCIO2记得供电;

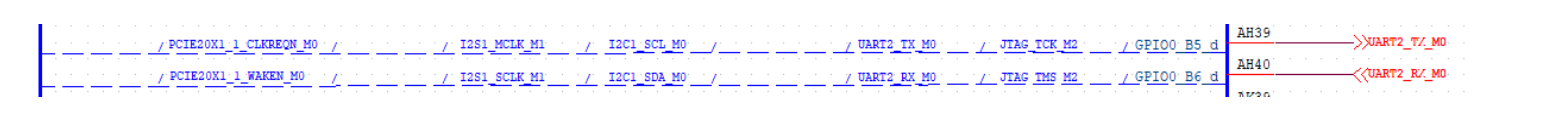

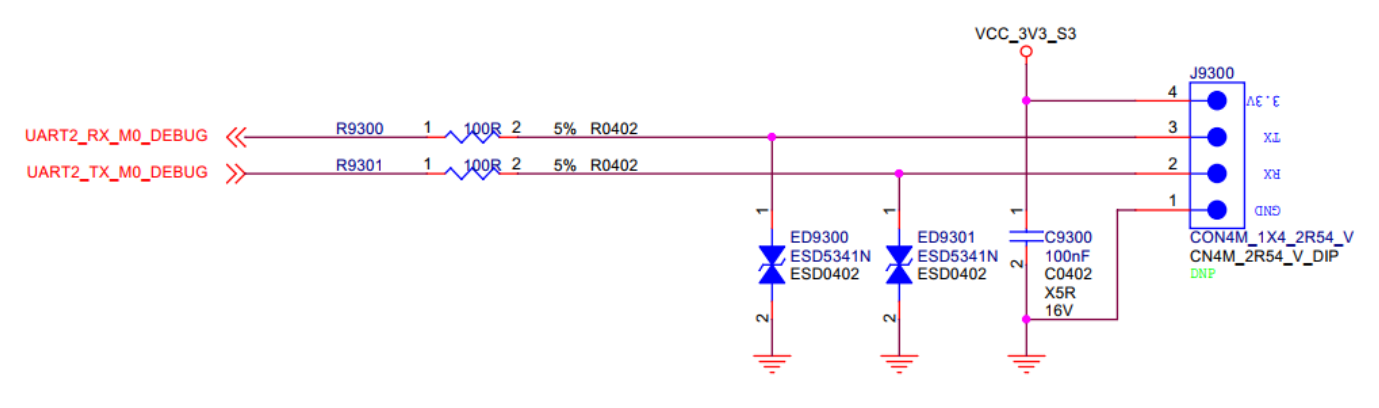

1.6.2 UART Debug

默认选择是UART2_RX_M0和UART2_TX_M0,默认波特率是1500000Bd;

这两个100R的电阻不能删;可以再加一下TVS管,用于抗静电浪涌;

1.7 DDR电路

1.7.1 DDR控制器介绍

RK3588S的DDR控制器接口支持 JEDEC SDRAM标准接口,

兼容 LPDDR4 / LPDDR4X / LPDDR5标准;(比如用在NAS里);

支持64bits数据总线宽度,(4个16bits的DDR通道组成),每个通道容量最大寻址地址8GB,所以4个通道容量可以支持总容量32GB;

两个16bits组成一个32bits通道,2个32bits组成不能采用不同容量颗粒配置,比如4GB+2GB;

支持Power Down / Self Refresh模式;

具有动态PVT补偿的可编程输出 和 ODT阻抗调整;

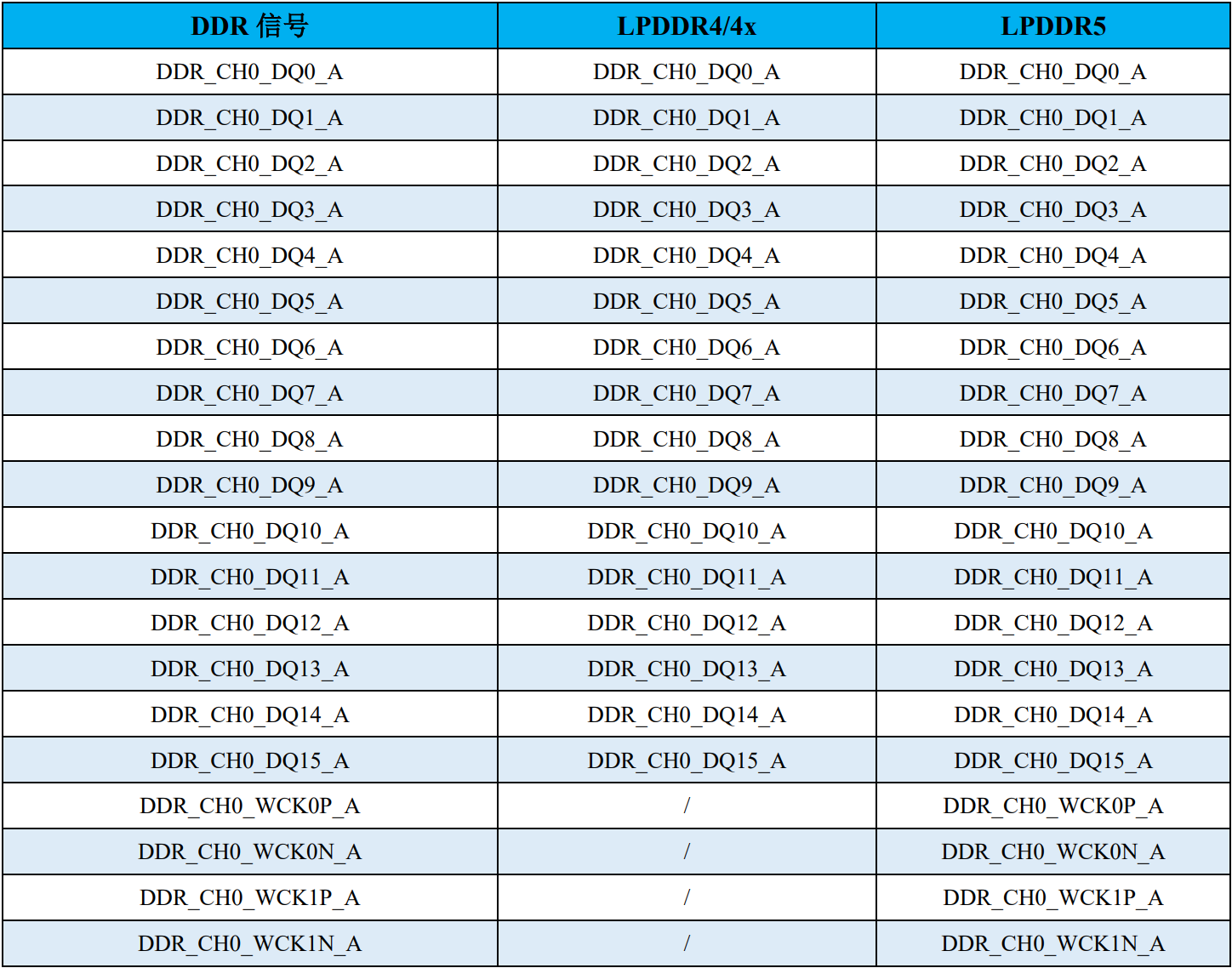

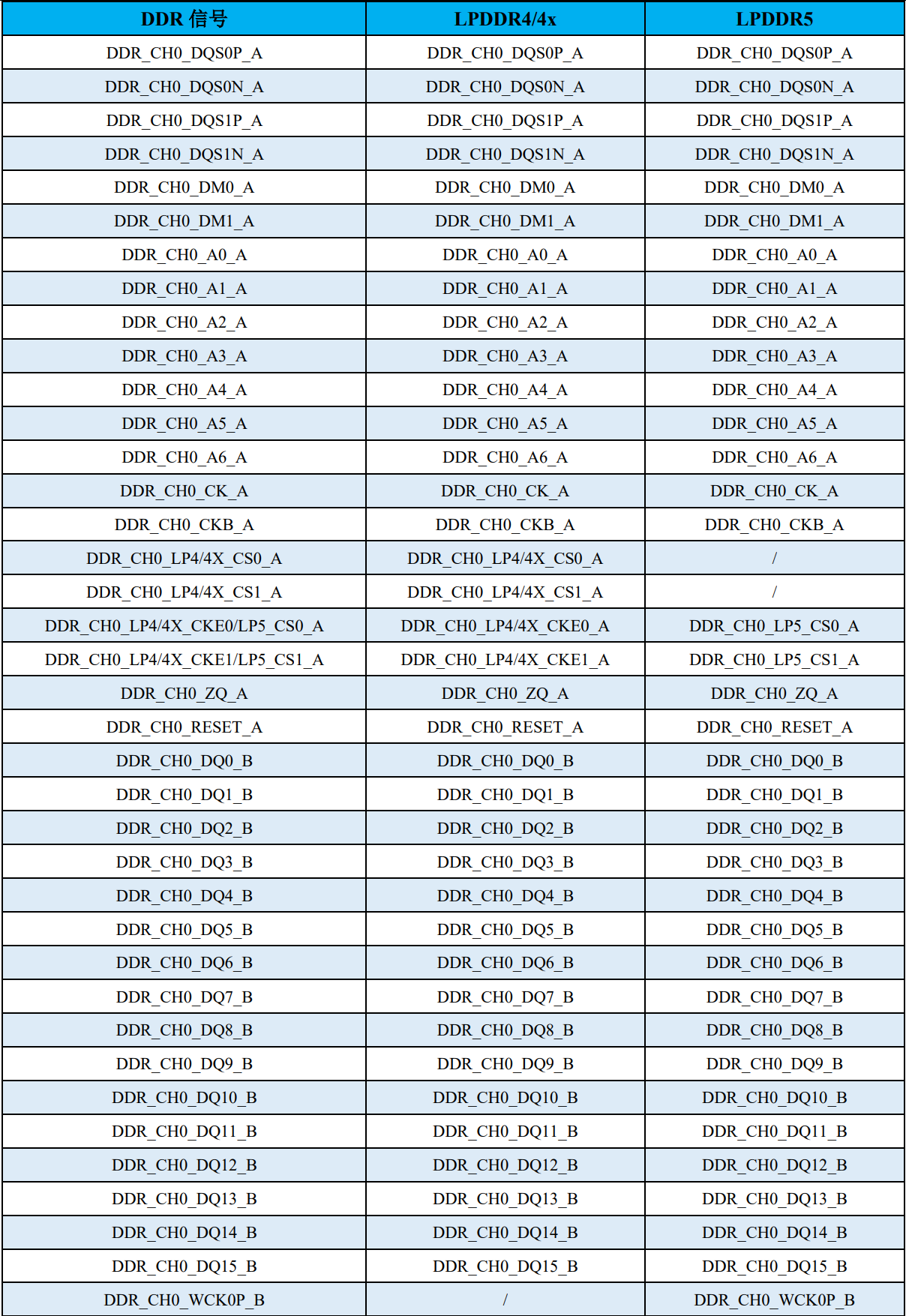

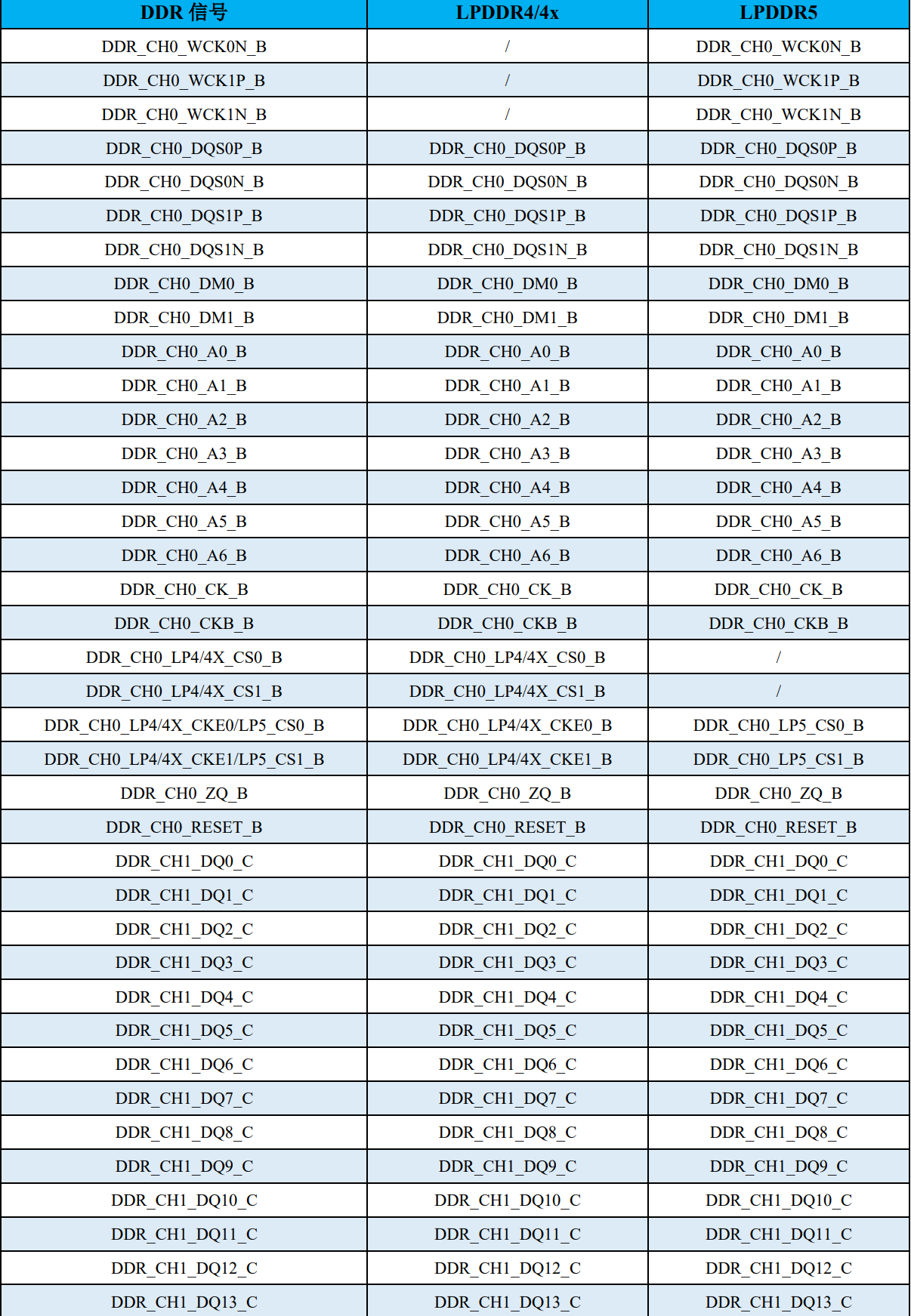

1.7.2 RK3588S DDR PHY IO Map表

1.7.3 LPDDR时的注意点

DQ,CA顺序不支持对调,需要按Map图中的分配;

DDR PHY ZQ 必须接 240R 1% 到VDDQ_DDR_S0电源上;

内置Retention功能(DDR 为了 “低功耗下保留数据” 而设计的模式) ,DDR自刷新期间,

DDR控制器端DDR_CH_VDDQ_CKE电源脚需要保持供电,其它电源可以关;

DDR颗粒的VDDQ电源在tCKELCK关闭5ns后也可以关,其它电源不能关;

LPDDR5里有WCK时钟,也就是LPDDR5有两个工作时钟,一个是CK_t和是CK_c,用于控制命令、地址的操作;

一个是WCK_t和WCK_c ,WCK可以是CK频率的2倍、或者4倍,当Write时,WCK是时钟,也是Write data stobe,当Read时,WCK是DQ和RDQS的时钟,RDQS是Read data strobe信号;

RK3588S在LPDDR5时,支持DVFSC Mode,可以在VDD2L(0.9V)和VDD2H(1.05V)电压间进行切换,高频时用VDD2H,低频时用VDD2L;

1.7.4 DDR颗粒外围电路设计

LPDDR4 / 4x / 5 的颗粒ZQ必须接 240R 1% 到 VDDQ_DDR_S0电源上;

LPDDR4 / 4x 的颗粒 ODT_CA 必须接 10K 5% 到 VDD2_DDR_S3电源上;

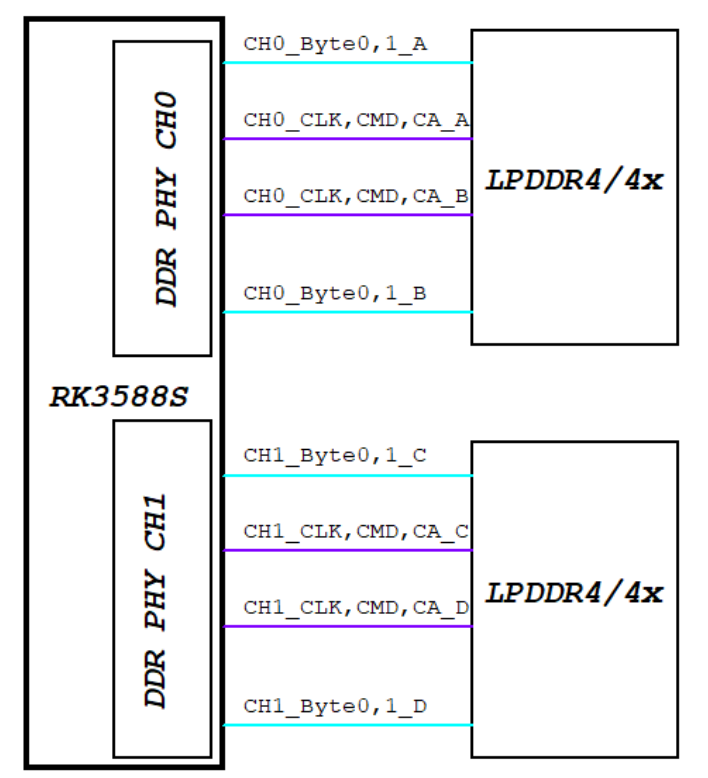

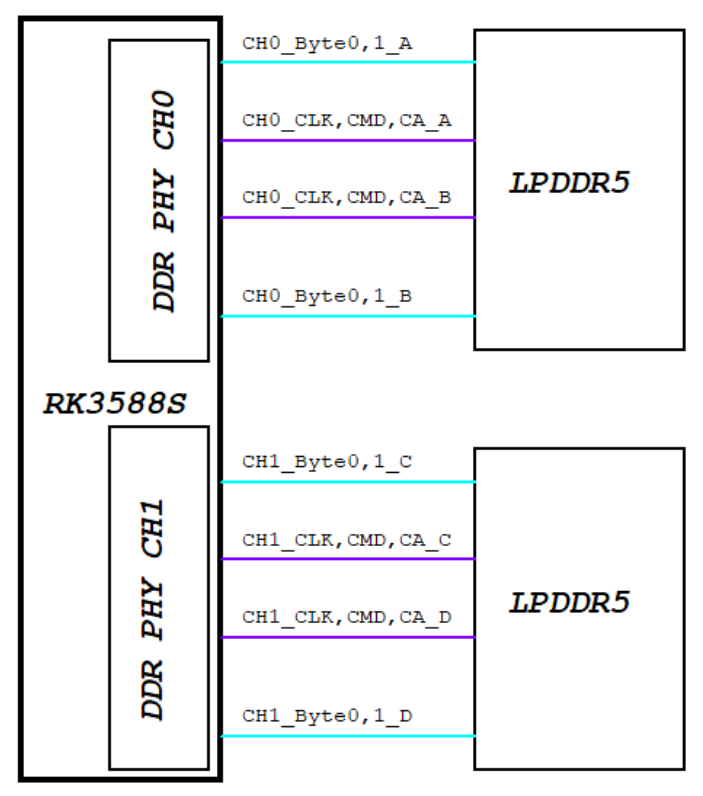

1.7.5 DDR拓扑结构和匹配方式设计

LPDDR4 / 4x 用2颗 32bit 时,DQ、CA采用点对点,DQ、CLK、CMD、CA都支持ODT,全部点对点;

LPDDR5 2颗32bit时,DQ、CA用点对点,DQ、CLK、CMD、CA都支持ODT,全部点对点;

1.7.6 DDR电源设计和上电时序要求

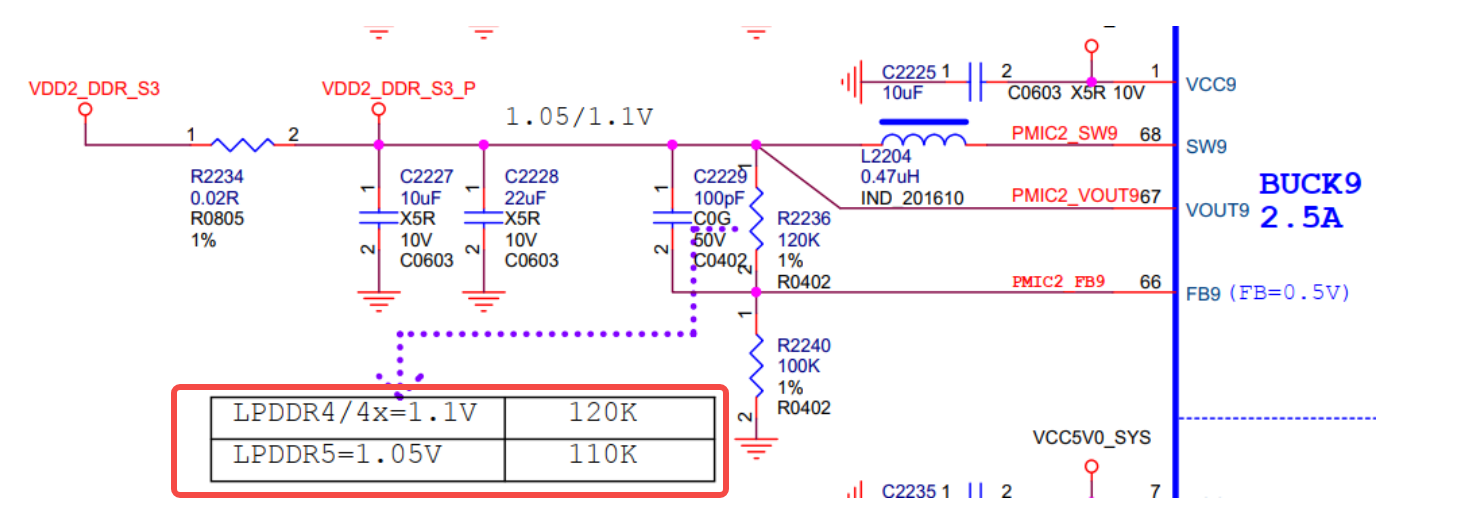

1.7.6.1 DDR PHY 供电电源

1.7.6.2 LPDDR4/4x/5 颗粒供电电源

1.7.6.3 双PMIC电源方案供电

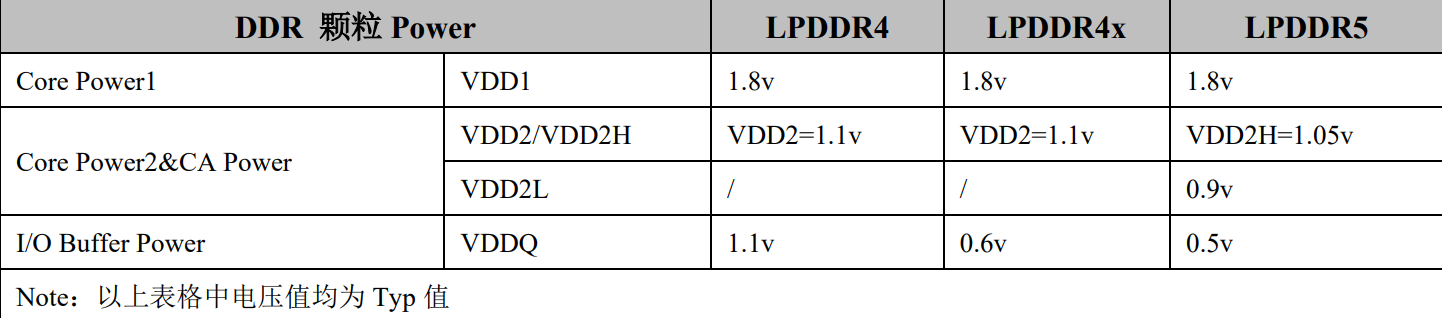

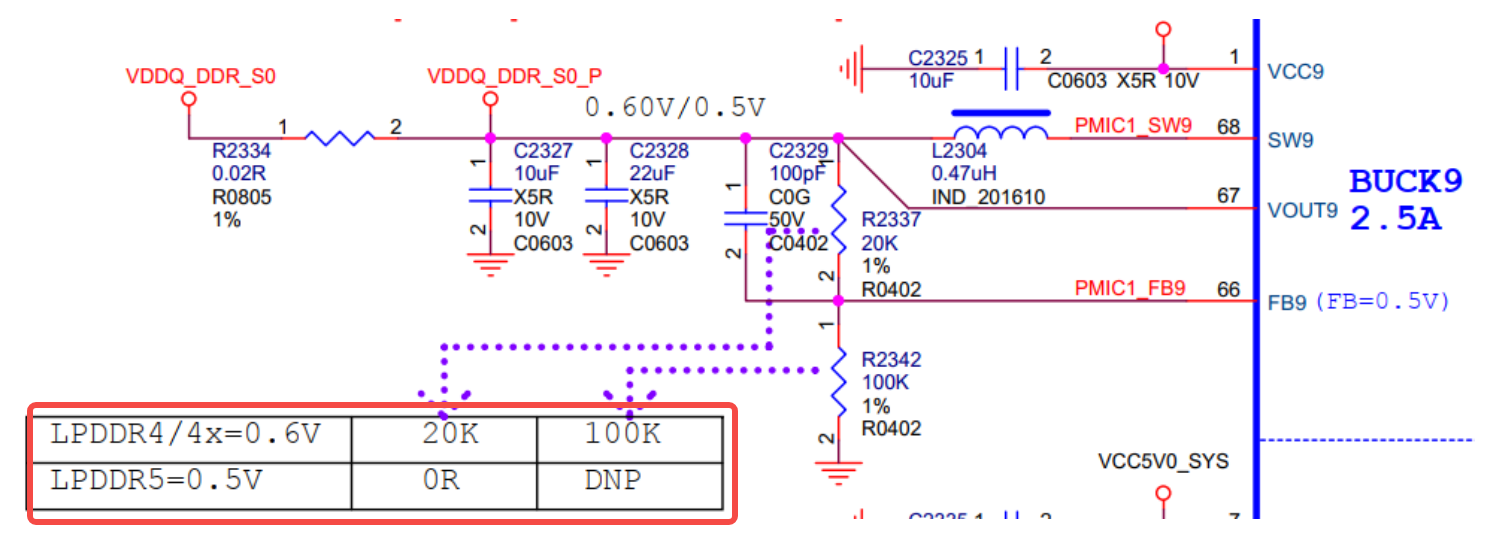

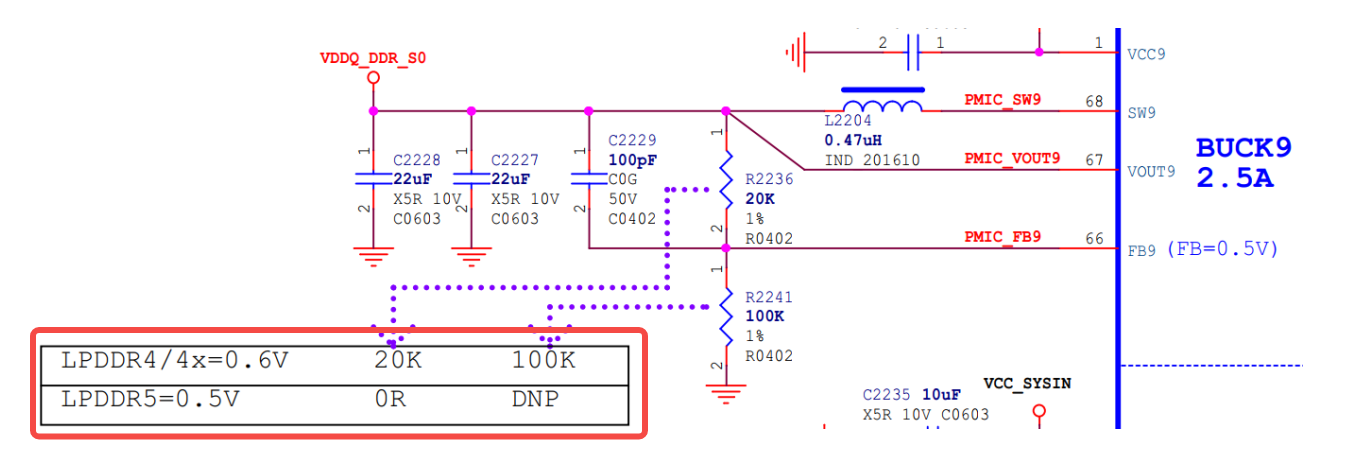

PMIC型号为 RK806-2,这里需要根据DRAM颗粒,来修改FB9引脚的分压电阻阻值,使得VDDQ_DDR_S0输出电压与颗粒匹配;

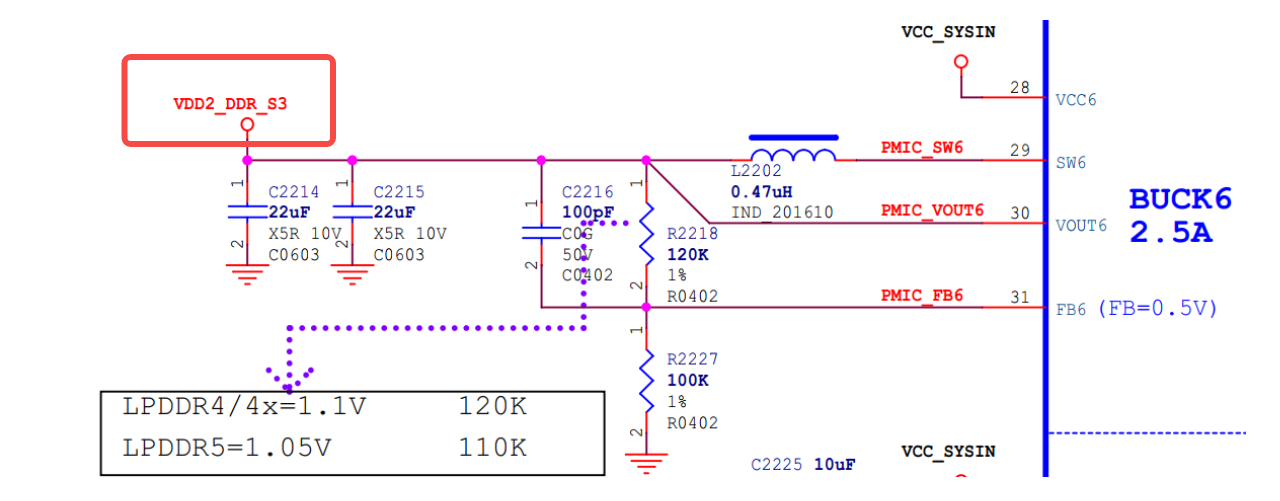

还有VDD2_DDR_S3输出电压要与颗粒匹配;

1.7.6.4 单PMIC电源方案供电

PMIC型号为RK806-1,还是一样,需要改分压电阻,让VDDQ_DDR_S0与颗粒匹配;

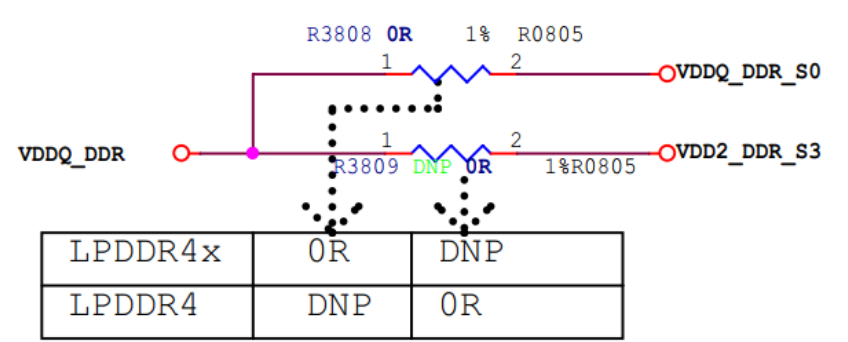

1.7.6.5 LPDDR4和LPDDR4x 的电源选择

用LPDDR4时,不贴R3808;

用LPDDR4x时,不贴R3809;

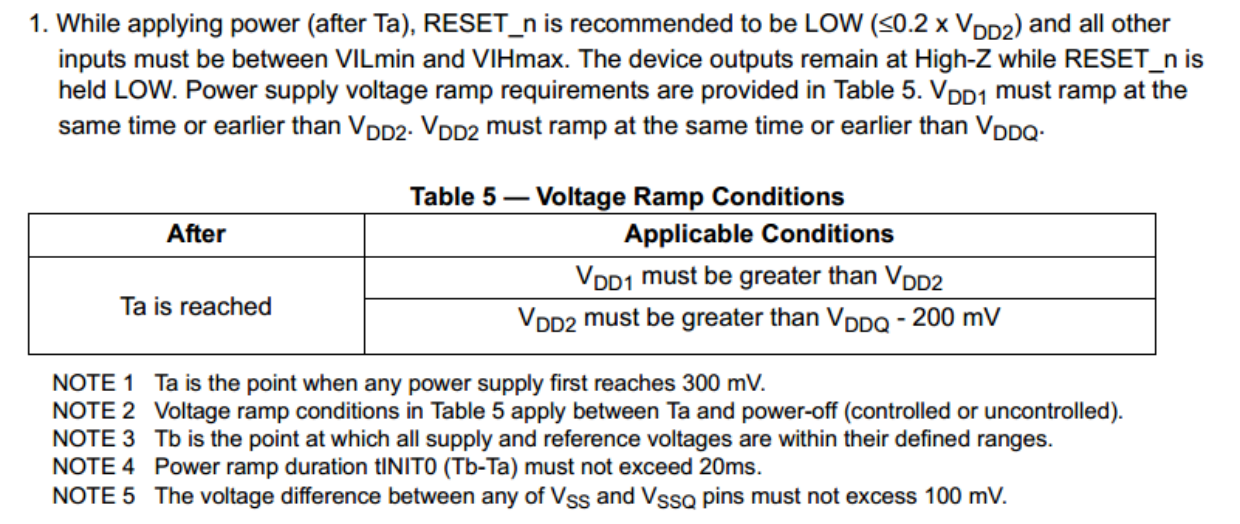

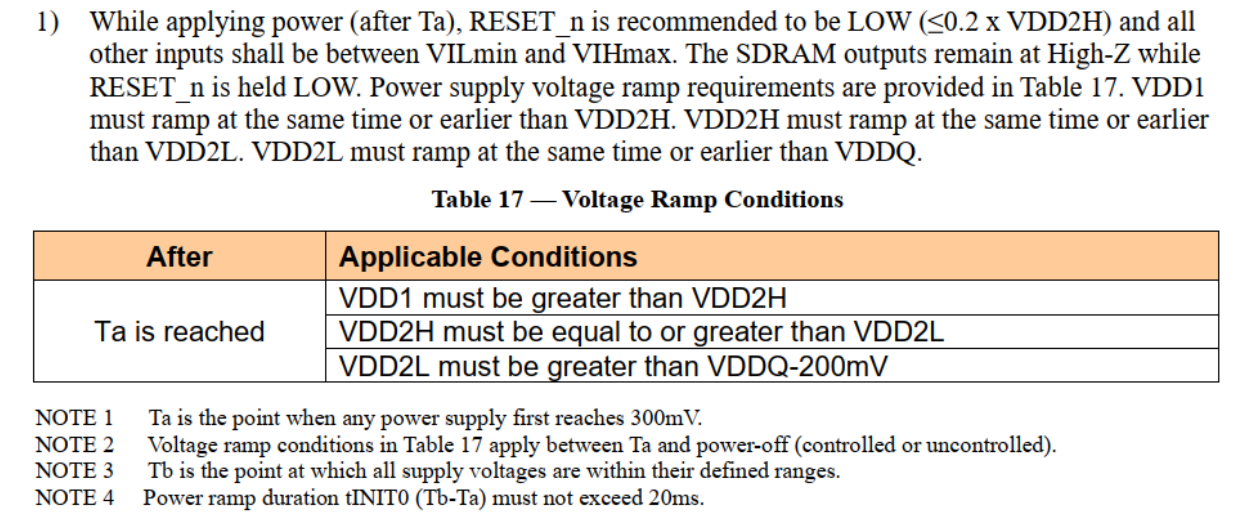

1.7.6.6 上电时序要求

都遵循JEDEC标准;

LPDDR4/4x

LPDDR5

1.7.6.7 RK3588S DDR颗粒支持列表

在《Rockchip_Support_List_DDR》文档里看;

1.8 eMMC电路

1.8.1 eMMC控制器介绍

RK3588S的eMMC兼容 5.1、5.0、4.51、4.41规范;

支持1bit、4bit、8bit 三种数据总线宽度;

支持HS400模式,HS200,DDR50等模式(向下兼容);

支持 CMD Queue;

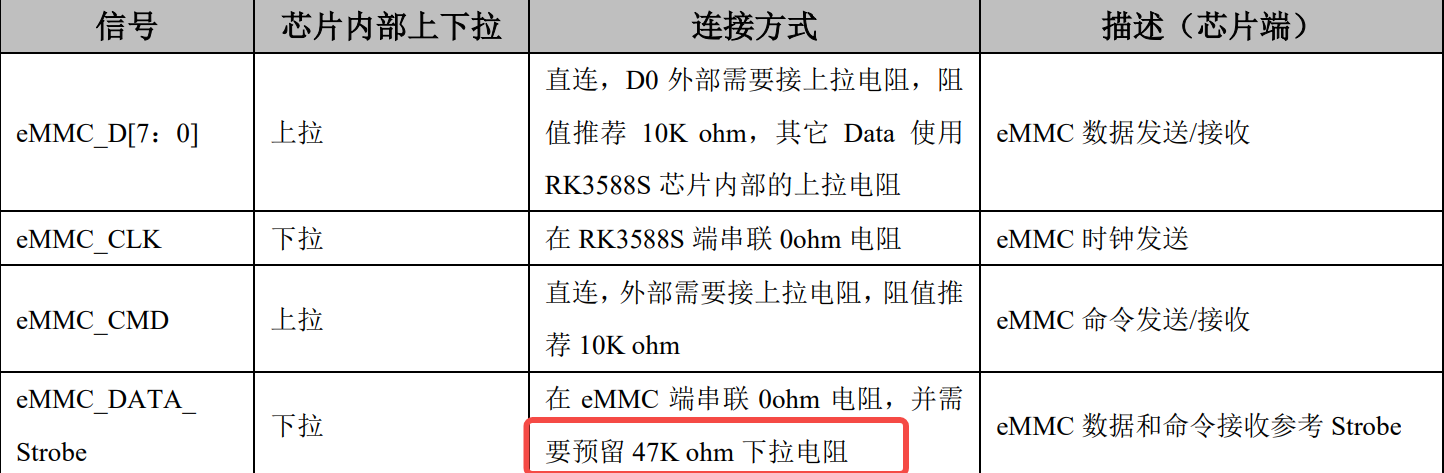

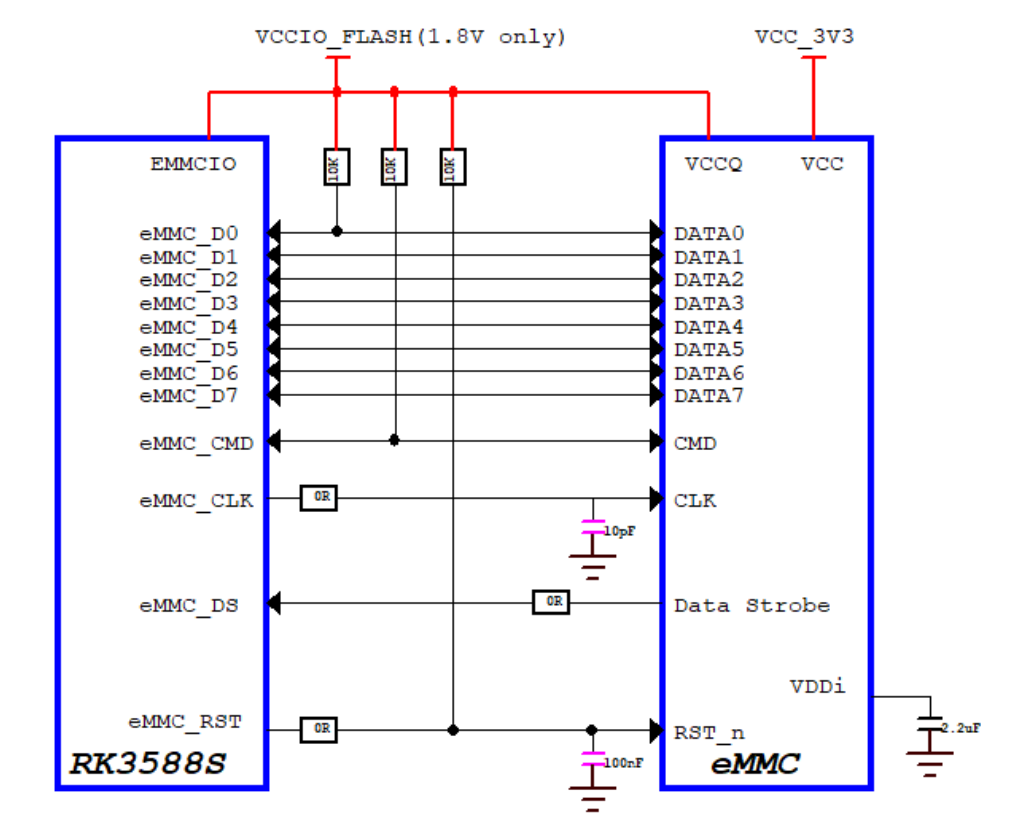

1.8.2 eMMC电路设计建议

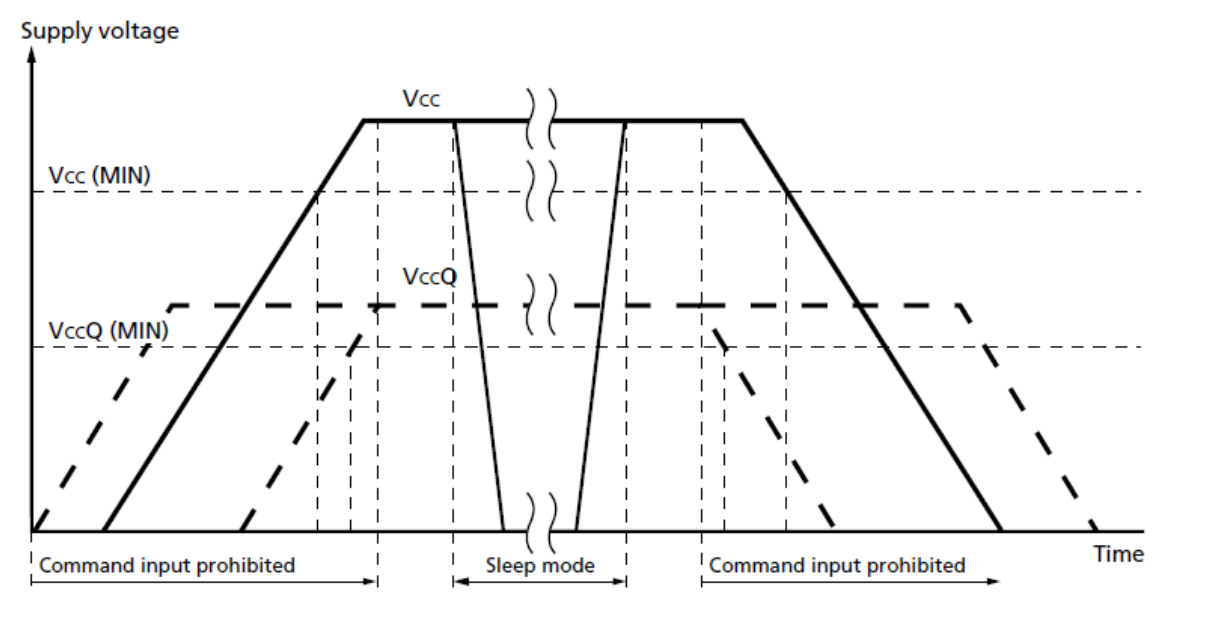

1.8.3 eMMC上电时序

RK3588S的eMMC接口属于EMMCIO电源域,只有一组供电的时候,没有时序要求,

当eMMC颗粒有两组电源的时候,上电时序参考JEDEC标准:

1.8.4 eMMC支持的型号

参考《RKeMMCSupportList》

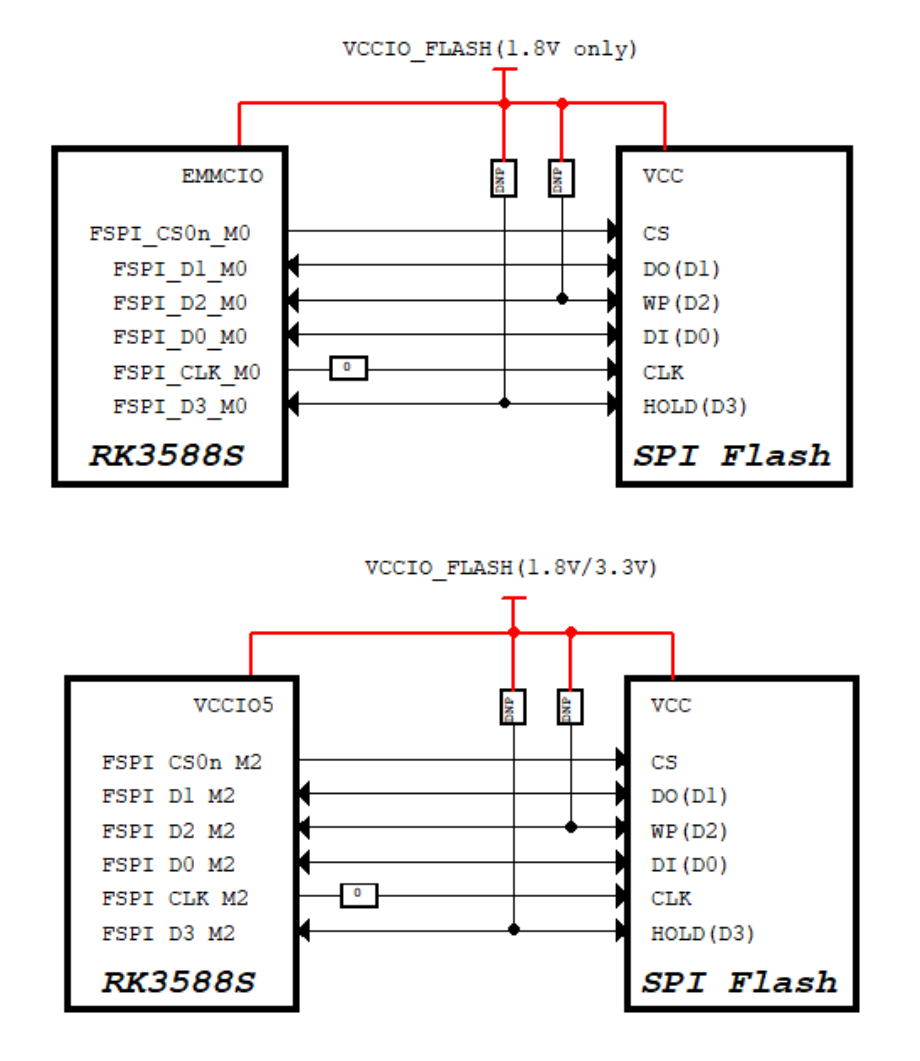

1.9 FSPI Flash电路

1.9.1 FSPI Flash 接口介绍

RK3588 有1个FSPI控制器,

支持串行NOR Flash,串行 Nand Flash;

支持SDR模式;

支持1、2、4线模式;

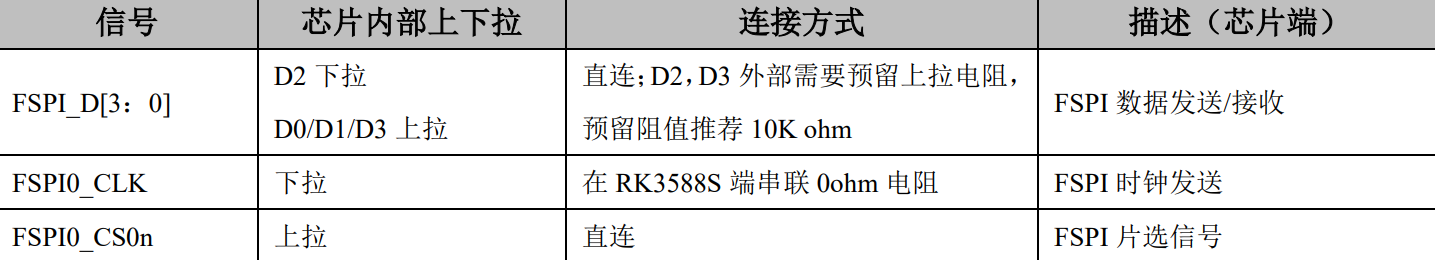

1.9.2 FSPI Flash电路设计

FSPI Flash 接口有两个复用口(M0和M2),只能用一个,它们分布在三个电源域中:

EMMCIO(1.8V)

VCCIO5(1.8V/3.3V)

1.9.3 SPI Flash支持型号

参考《RK_SpiNor_and_SLC_Nand_SupportList》

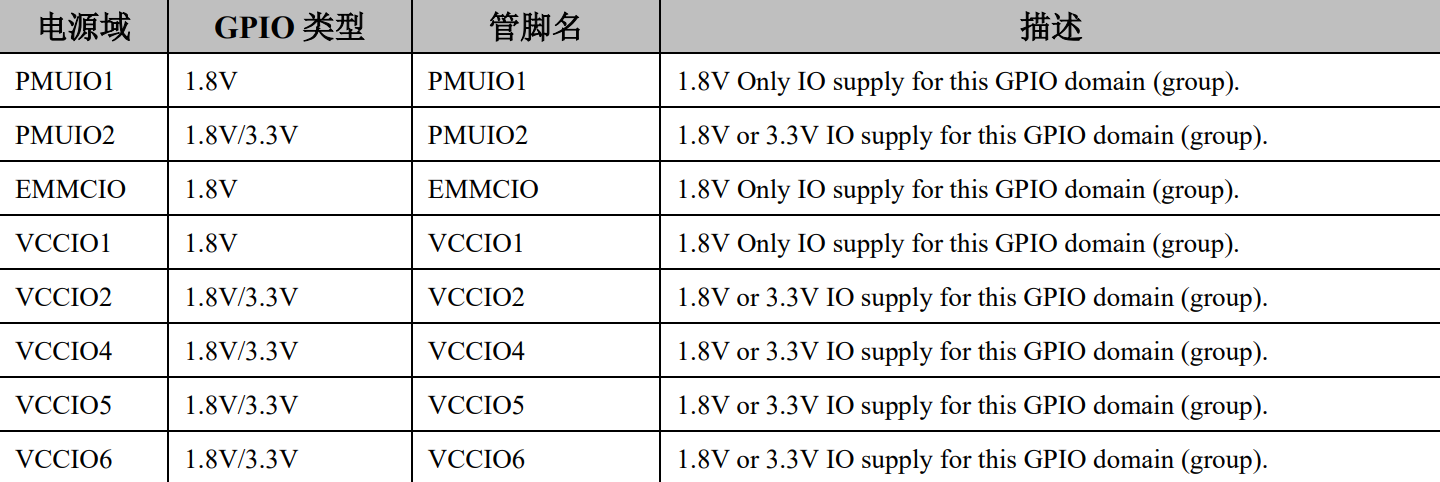

1.10 GPIO电路

1.10.1 电平类型

RK3588S 中只有1.8V,和支持1.8V/3.3V 两种电压的配置;

1.10.2 IO口说明

1.除了引导相关的GPIO,剩下的IO口复位默认为输入;

2.GPIOx_xx_u 其中_u 表示这个 IO 复位默认状态为内部上拉;

3.GPIOx_xx_d 其中_d 表示这个 IO 复位默认状态为内部下拉;

4.GPIOx_xx_z 其中_z 表示这个 IO 复位默认状态为高阻;

5.各功能 name 后缀有加_M0 或 M1 或_M2 代表同一个功能复用到不同 IO 上,同时只能选择其中 一个,比如选择 UART7 功能时,必须选择 UART7_TX_M0 和 UART7_RX_M0 组合,不支持 UART7_TX_M0 和 UART7_RX_M1 组合,对所有功能有不同 IOMUX 的都是这样的约束。

1.10.3 GPIO驱动能力

RK3588S中的IO口驱动能力多档可挑,有两种;

一种是 Level0~5,另一种是Level0~3;

具体参考《RK3588S_PinOut》文档中表5的"SupportDriveStrength"和"DefaultIO DriveStrength"

1.10.4 GPIO电源

PMUIO1、EMMCIO、VCCIO1固定的,不能配置;

PMUIO2、VCCIO2,VCCIO[4:6]电源域 RK3588S 芯片可以自动识别硬件配置的电压,不需要软件 根据硬件供电电压进行配置。比如:PMUIO2 配置成 1.8V,PMUIO2_1V8=1.8V, PMUIO2=1.8V;若配置成 3.3V,PMUIO2_1V8=1.8V, PMUIO2=3.3V

这里区别是PMUIO2的配置,PMUIO2_1V8还是1.8V;

另外要注意这两个电源脚必须同时为 S0 或者 S3 的电源,不能一个为 S0,一个为 S3(S0:待机时关掉;S3 待机时需要打开)。

供电引脚需要一个0.1uF电容去耦;

若一个电源域里的所有 IO 都不使用,那么这个电源域的供电电源可以不供电,该脚悬空即可。 (TYPEC0 除外)