ARM处理器的小常识

一、计算机体系结构中两种核心的指令集

CISC:Complex Istruction Set Computer,复杂指令集计算机

主流架构:x86 架构(Intel、AMD 的 CPU 均基于此,如酷睿 i 系列、锐龙系列)

优势:软件生态极丰富(几乎所有桌面操作系统、工业软件、游戏均支持 x86),兼容性强,单条复杂指令可减少代码量

RISC:Reduced Instruction Set Computer,精简指令集计算机

主流架构:ARM 架构(占比最高)、MIPS、PowerPC

优势:能效比高(相同性能下功耗更低)、硬件成本低、流水线并行效率高,适合移动和嵌入式场景。

二、寄存器

1.通用寄存器

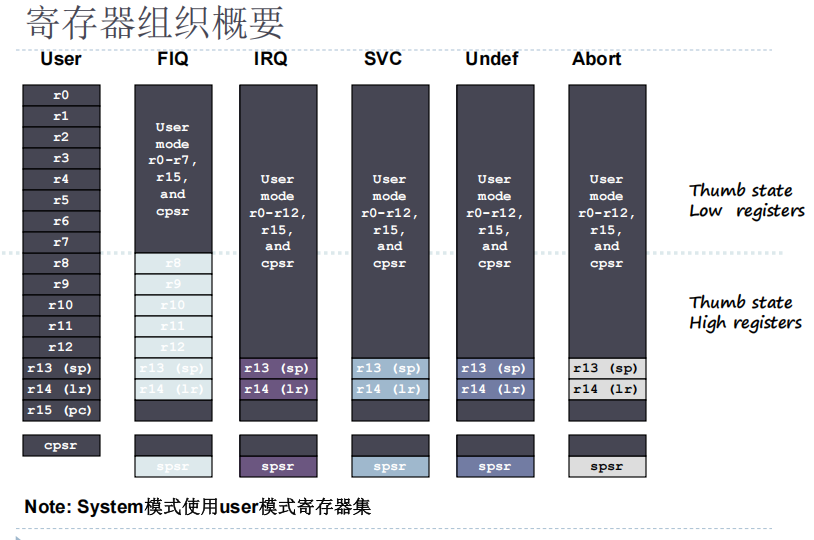

32 位 ARM 架构的通用寄存器按功能可分为通用目的寄存器和程序状态寄存器(PSR),其中通用目的寄存器共 16 个(R0-R15)

SP (Stack Pointer)---栈指针 --> R13,

LR (Linked Register)---链接寄存器---->R14,

PC (Program Counter)---程序计数器--->R15.

CPSR

--- current program status register:--(当前程序状态寄存器)

CPSR 是一个 32 位寄存器,在所有处理器模式下都可访问,用于记录当前 CPU 的运行状态

SPSR

---Saved Program Status Register--(保存程序状态寄存器)

SPSR 是仅在异常模式(如 IRQ、FIQ、SVC 等)下存在的 32 位寄存器,功能单一但关键:保存进入异常前的 CPSR 值,以便异常处理完成后恢复 CPU 原来的状态。

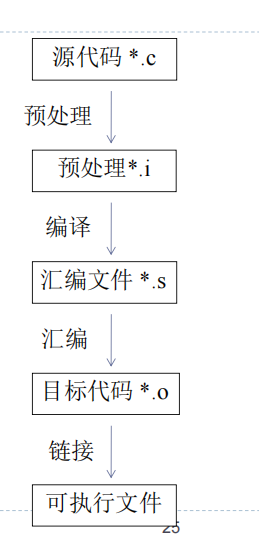

2.编译器的作用

三.计算机系统的硬件组成

三级存储系统:

CACHE-->主存储器-->辅助存储器

Cache -- 高速缓存 采用哈佛架构分为: I-Cache(指令高速缓存)和 D-Cache(数据高速缓存)

Cache 是位于 CPU 与主内存之间的一种高速容量小、速度快的临时存储部件,其核心作用是解决 CPU 与主内存之间的速度不匹配问题,从而提升计算机整体性能。

- 时间局部性:最近被访问的数据,短期内很可能再次被访问(如循环变量、频繁调用的函数)。

- 空间局部性:被访问数据的邻近数据,很可能在近期被访问(如数组遍历、连续的指令序列)。

基于这一原理,Cache 会临时存储 CPU 近期可能需要的数据和指令,当 CPU 再次访问时,可直接从速度更快的 Cache 中获取,而非较慢的主内存,从而减少访问延迟。

MMU

(Memory Management Unit,内存管理单元)

MMU 的核心作用是管理虚拟地址与物理地址的映射

地址转换(虚拟地址 → 物理地址)

现代操作系统中,CPU 执行程序时使用的是虚拟地址(由程序看到的连续内存空间),而实际数据存储在物理地址(内存硬件的真实地址)中。MMU 通过查询页表(Page Table) 完成二者的转换,让程序无需关心物理内存的实际布局。

转换单位:通常以页(Page) 为单位(如 4KB、2MB),虚拟地址和物理地址被划分为大小相等的页,MMU 按页映射。

4.总线结构

AHB(Advanced High-performance Bus):高性能总线

APB(Advanced Peripheral Bus):外设(Peripheral) 总线

DMA(Direct Memory Access,直接内存访问)并非传统意义上的 “总线”,而是一种绕过 CPU、让外设直接与内存进行数据传输的技术,其核心是通过DMA 控制器实现外设与内存之间的高效数据交换,减少 CPU 的干预,提升系统整体性能。

四.处理器的工作模式

1. User:用户模式(非特权模式)大部分任务执行在这种模式。

(特权模式)

2. FIQ:当一个高优先级的中断产生时,会进入到这种模式。

3. IRQ:当一个低优先级(normal)的中断产生时,会进入这种模式。

4.Supervisor:当复位或软中断指令产生时进入这种模式

5. Abort:当存取异常时会进入这种模式。

6.Undef:执行未定义指令时进入这种模式

7. System:使用和 User模式相同存储器集的特权模式。无特定触发方式(内核主动切换)

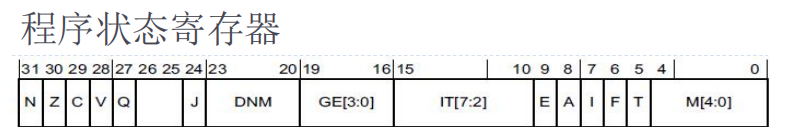

32 位 ARM

- 标志位(N、Z、C、V):

- N(Negative):运算结果为负数时置 1(二进制最高位为 1);

- Z(Zero):运算结果为 0 时置 1(用于条件跳转,如相等则跳转);

- C(Carry):加法进位 / 减法借位时置 1,或移位操作的最后移出位;

- V(Overflow):带符号数运算溢出时置 1(如正数相加得负数)。

- 中断控制位(I、F):

- I:置 1 时禁止 IRQ(普通中断),置 0 时允许;

- F:置 1 时禁止 FIQ(快速中断),置 0 时允许。

- 模式位(M [4:0]):5 位组合定义当前处理器模式(如用户模式、中断模式等)。

- 其他位:如 T 位(Thumb 状态标志)、Q 位(饱和运算标志)等

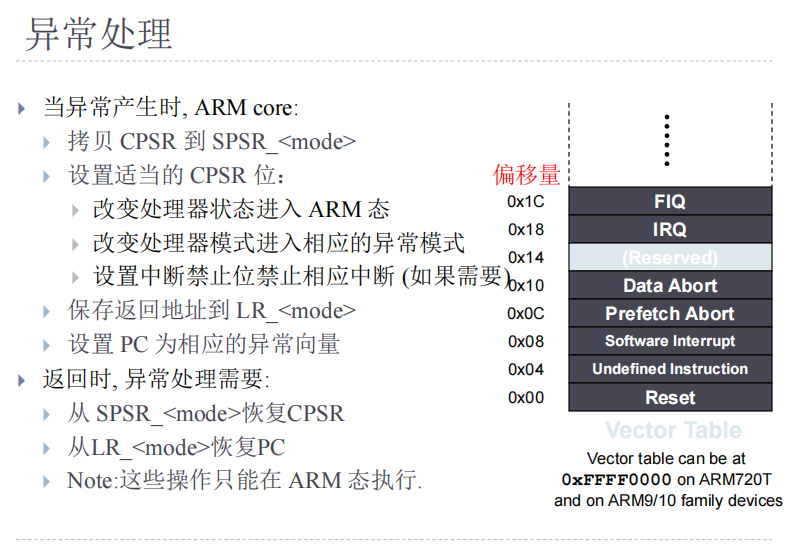

异常向量表

Flash(闪存)

是一种非易失性存储技术(断电后数据不丢失)

NOR Flash:支持地址访问

NAND Flash:以块为单位访问 (512 Byts为一块)