GD32入门到实战39--SRAM

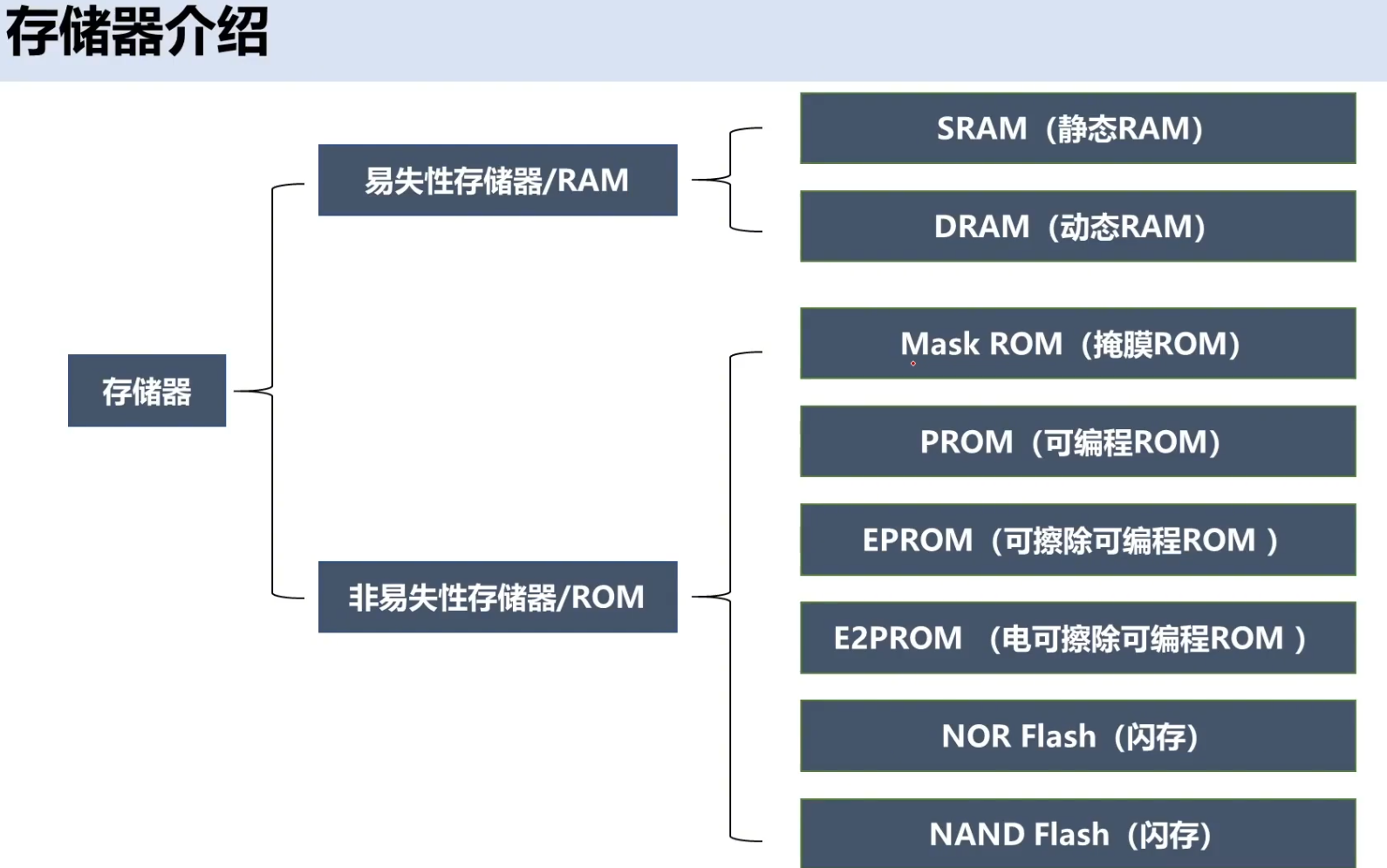

单片机的RAM容量太小了(64k)

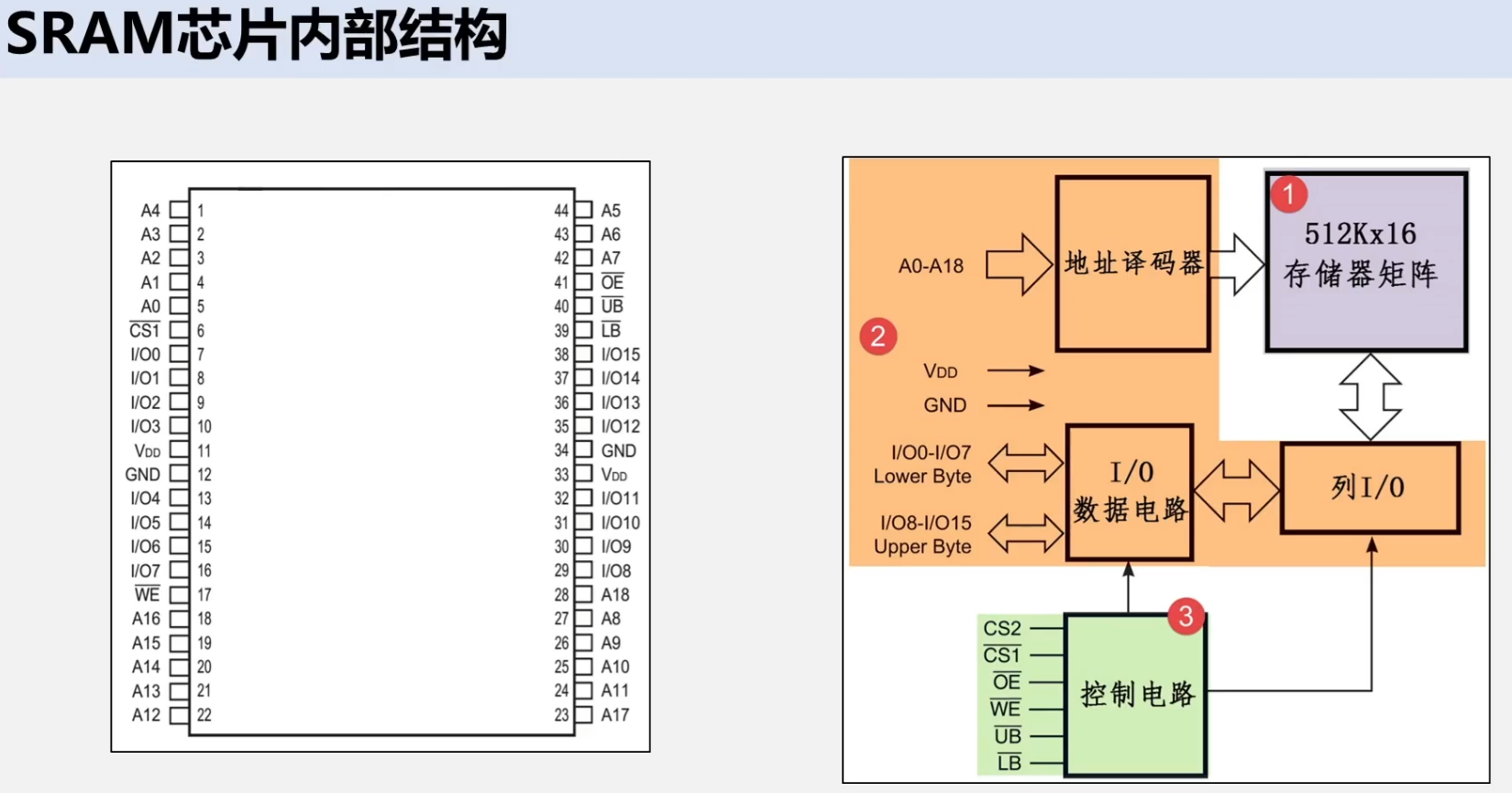

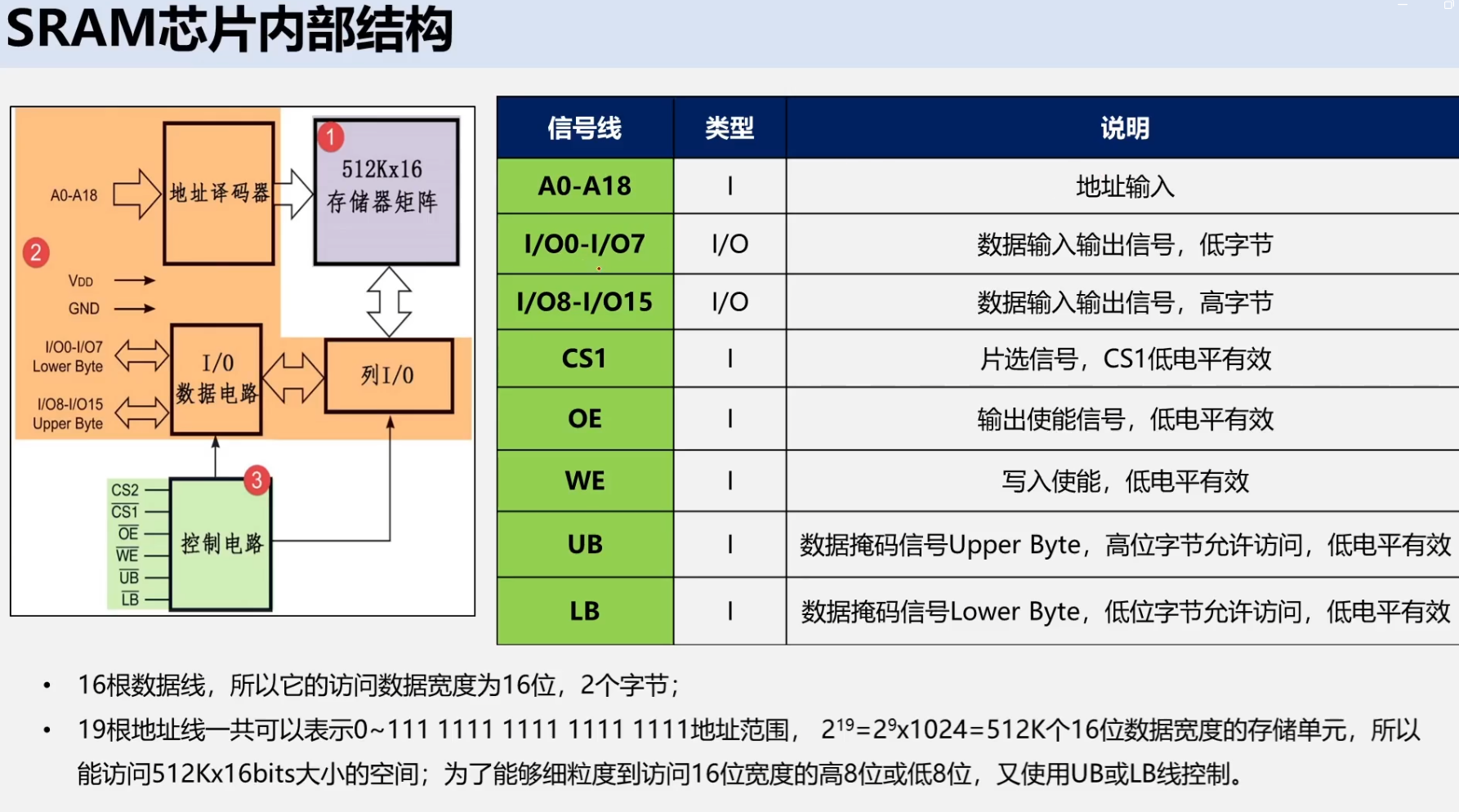

外接SRAM--1M字节(IS62WV51216BLL-55)

512k,16bit,最小读读时间周期55ns

单片机Flash的内存是按8bit(一个字节),每个字节都有对应的地址

而SRAM不一样,是512 * 16bit(两个字节),两个字节一个地址 ,也就是1024k(1M)

一个地址两个字节,操作UB和LB选择高8位还是低8位

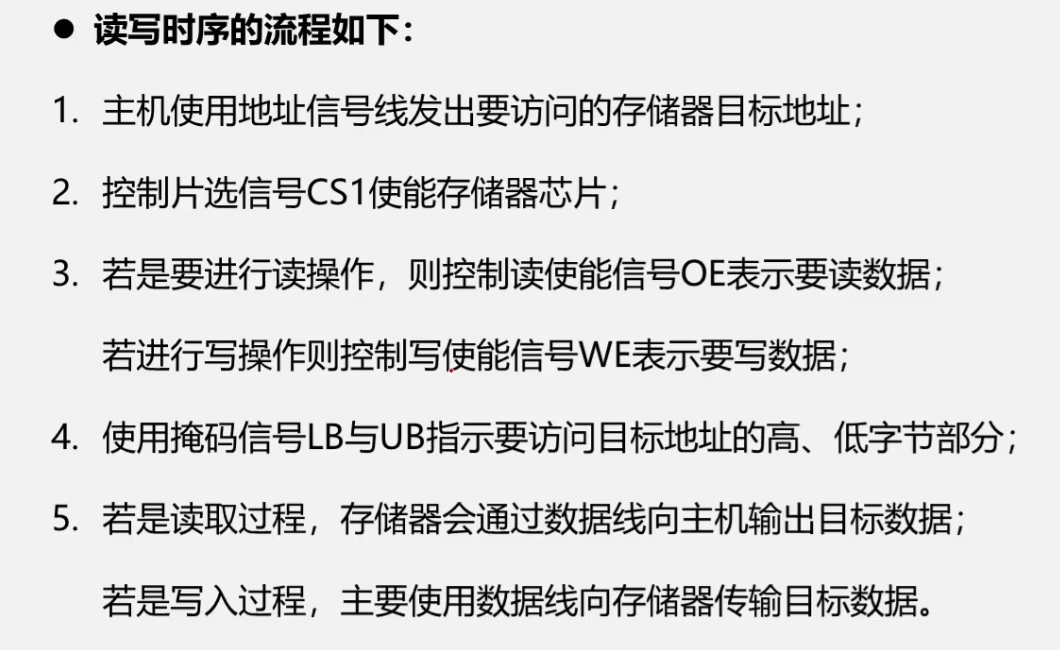

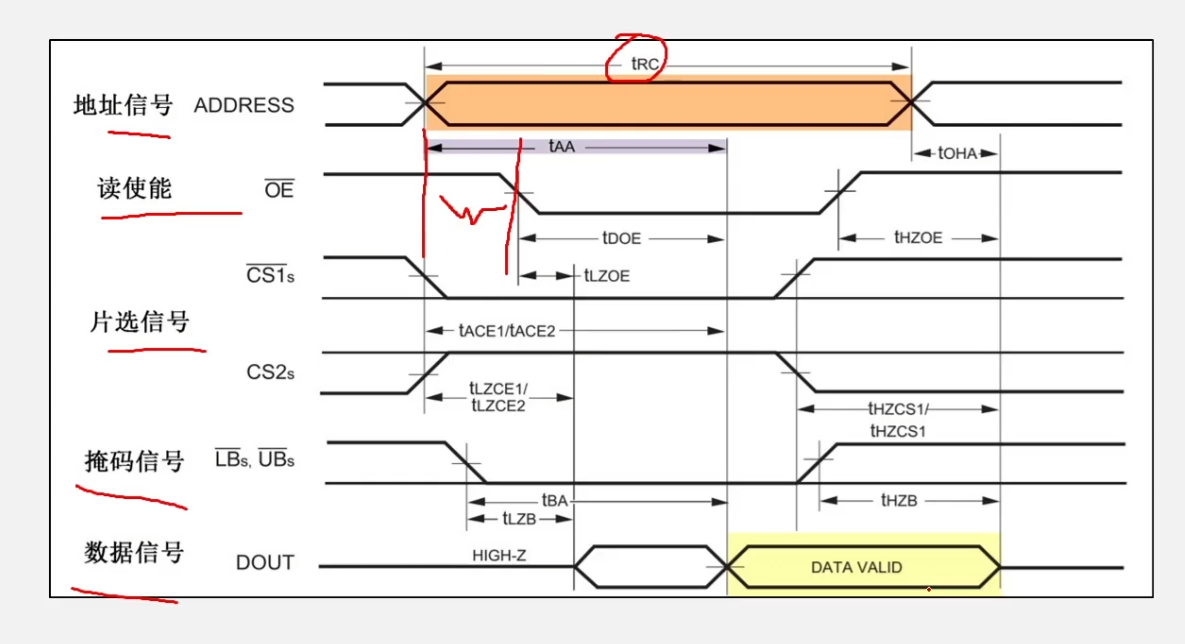

读时序

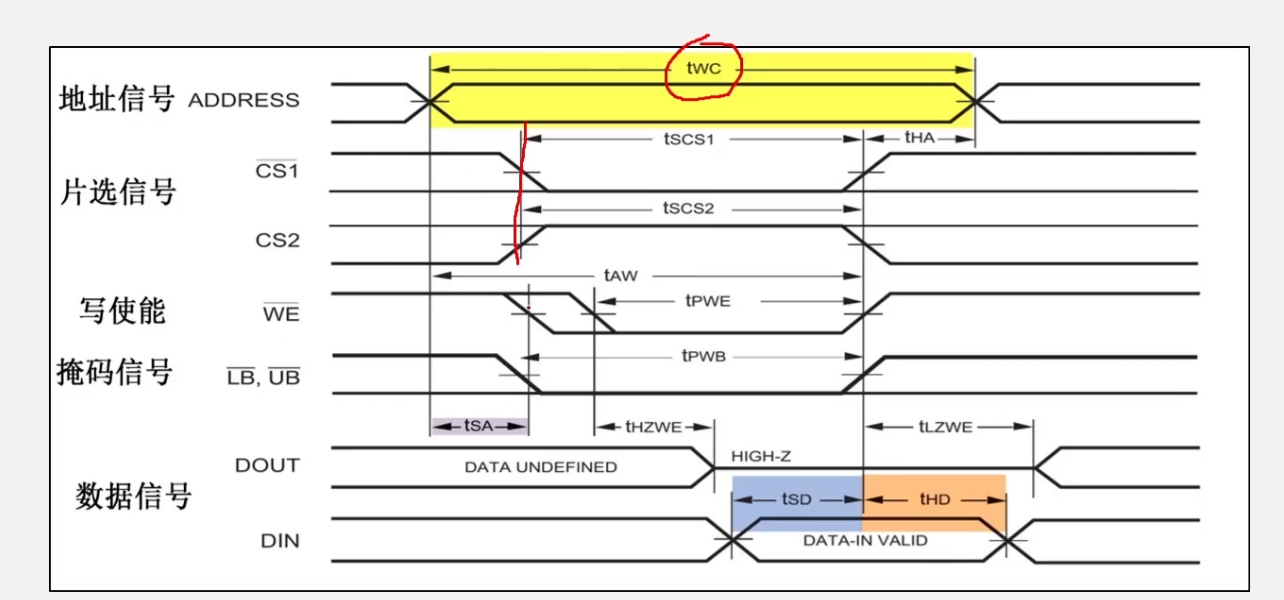

写时序

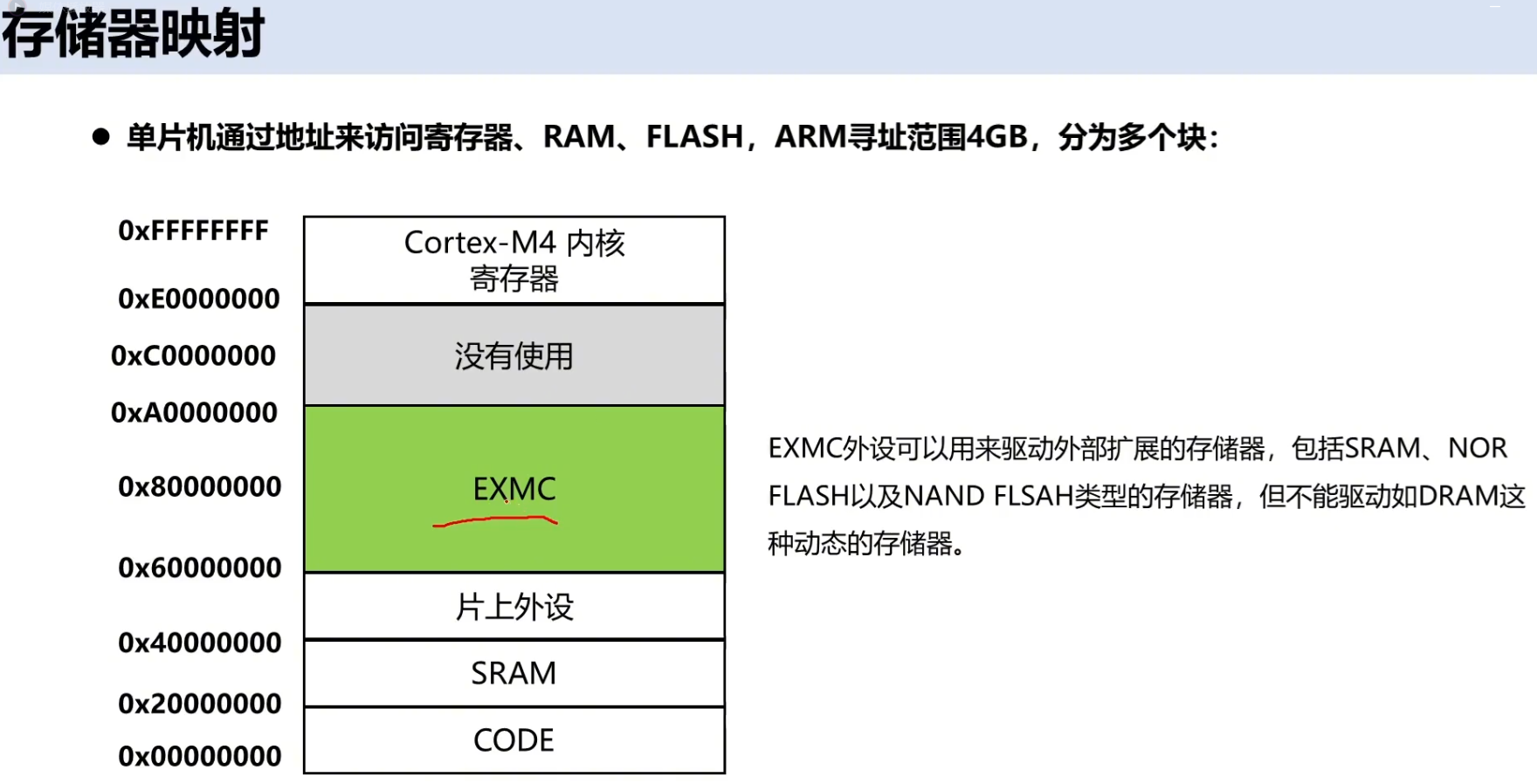

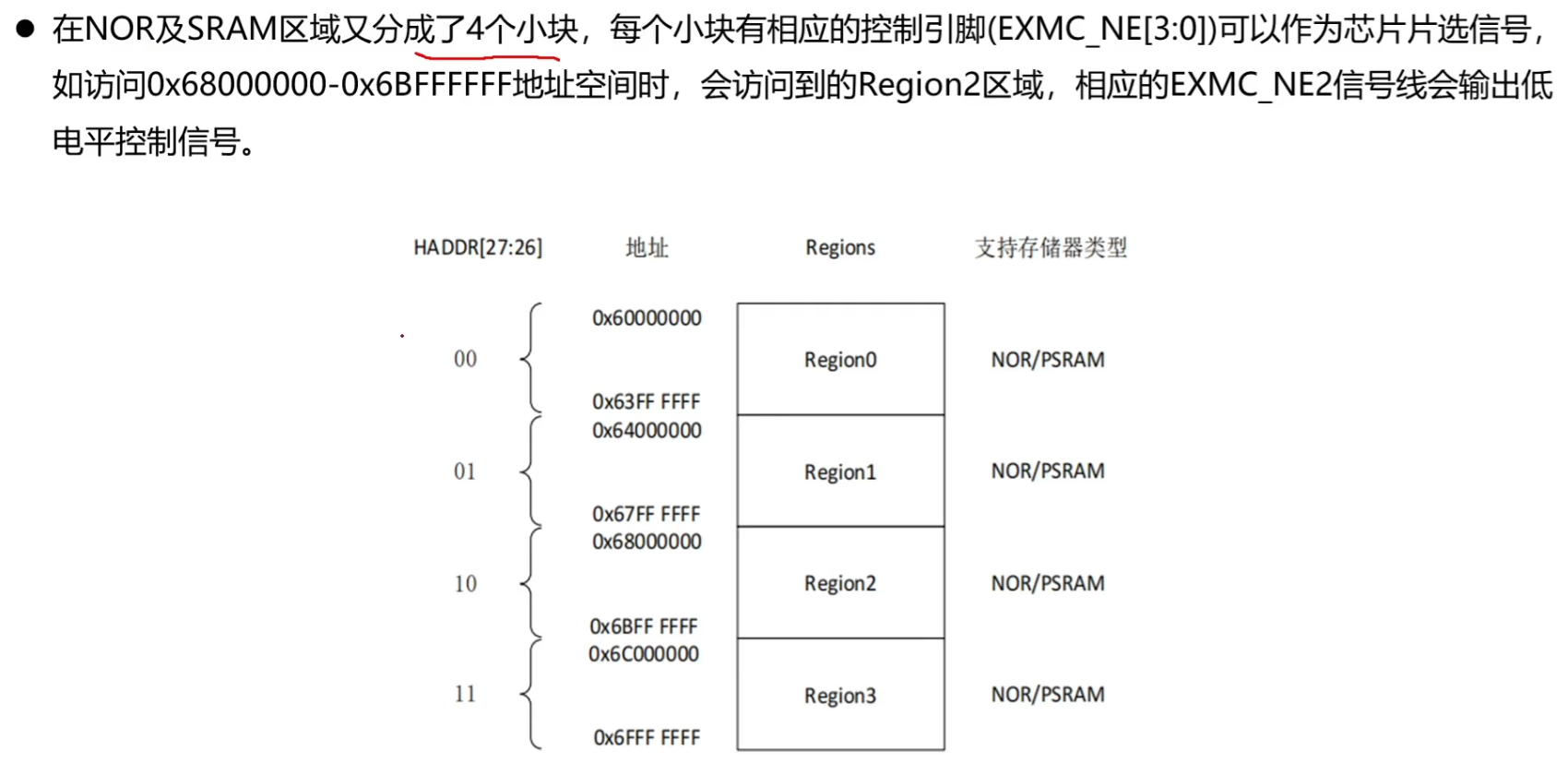

单片机片上外设EXMC(stm32为FSMC)

地址为0x8000000~0xA000000(1GB)

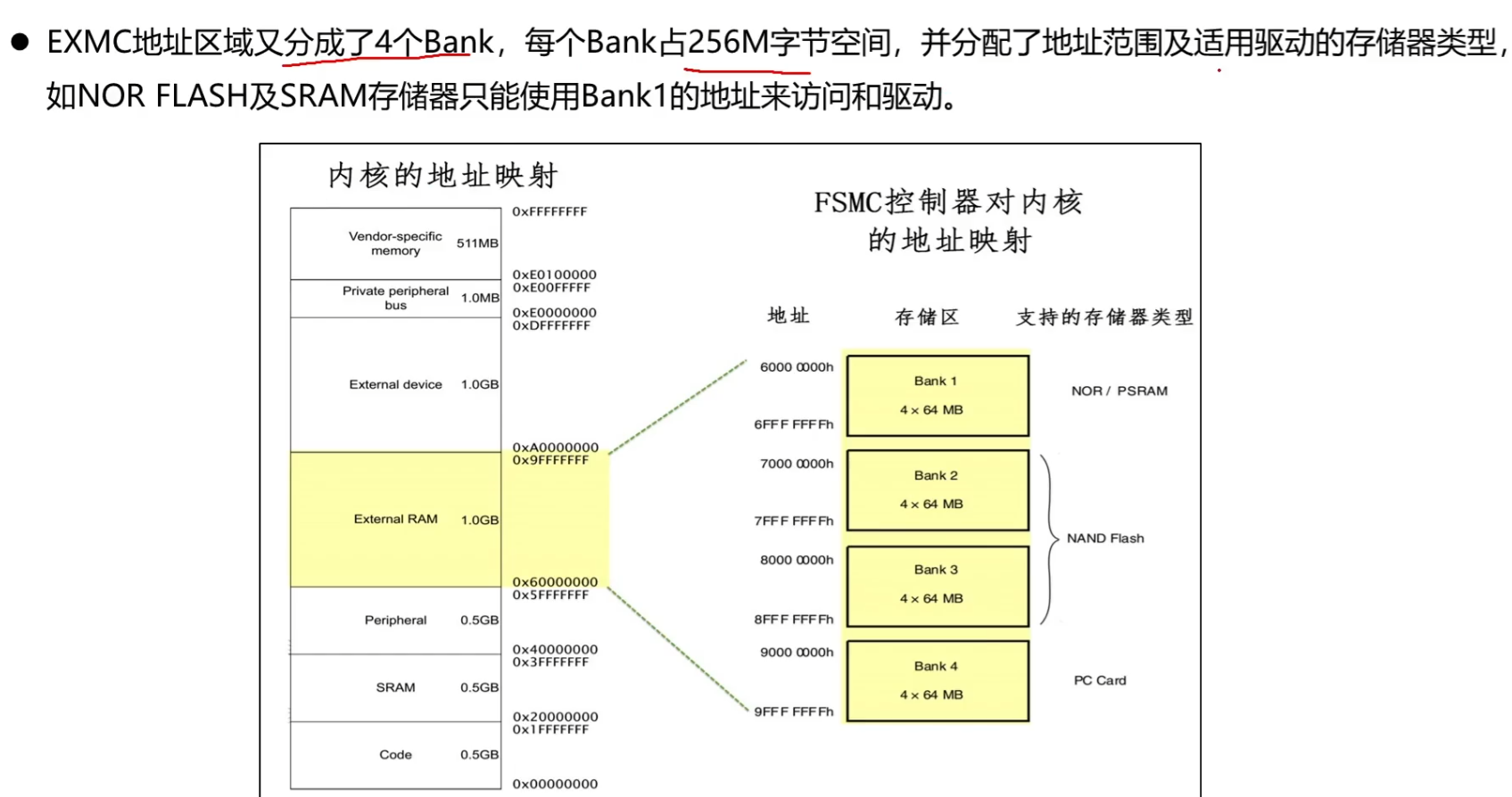

1GB分成4个Bank ,每个Bank256M

第一个Bank是用来驱动NOR/SRAM的

每个Bank又会划分4小块,1块64M,每一块都可以单独的驱动一块NOR/SRAM芯片

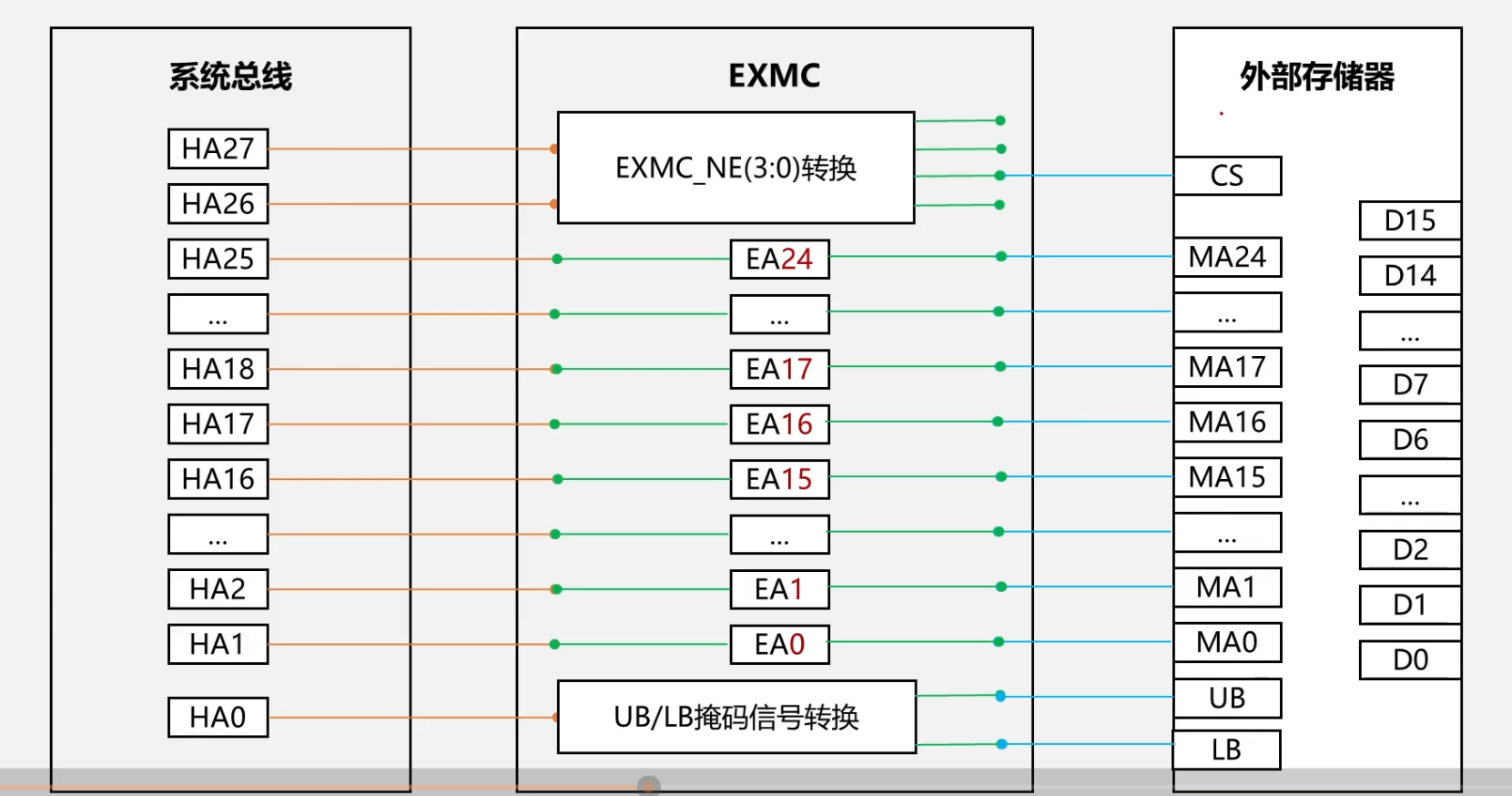

HA0用来控制高8位还是第8位,HA1~HA25为地址线,HA27和HA26用来区分哪一个块

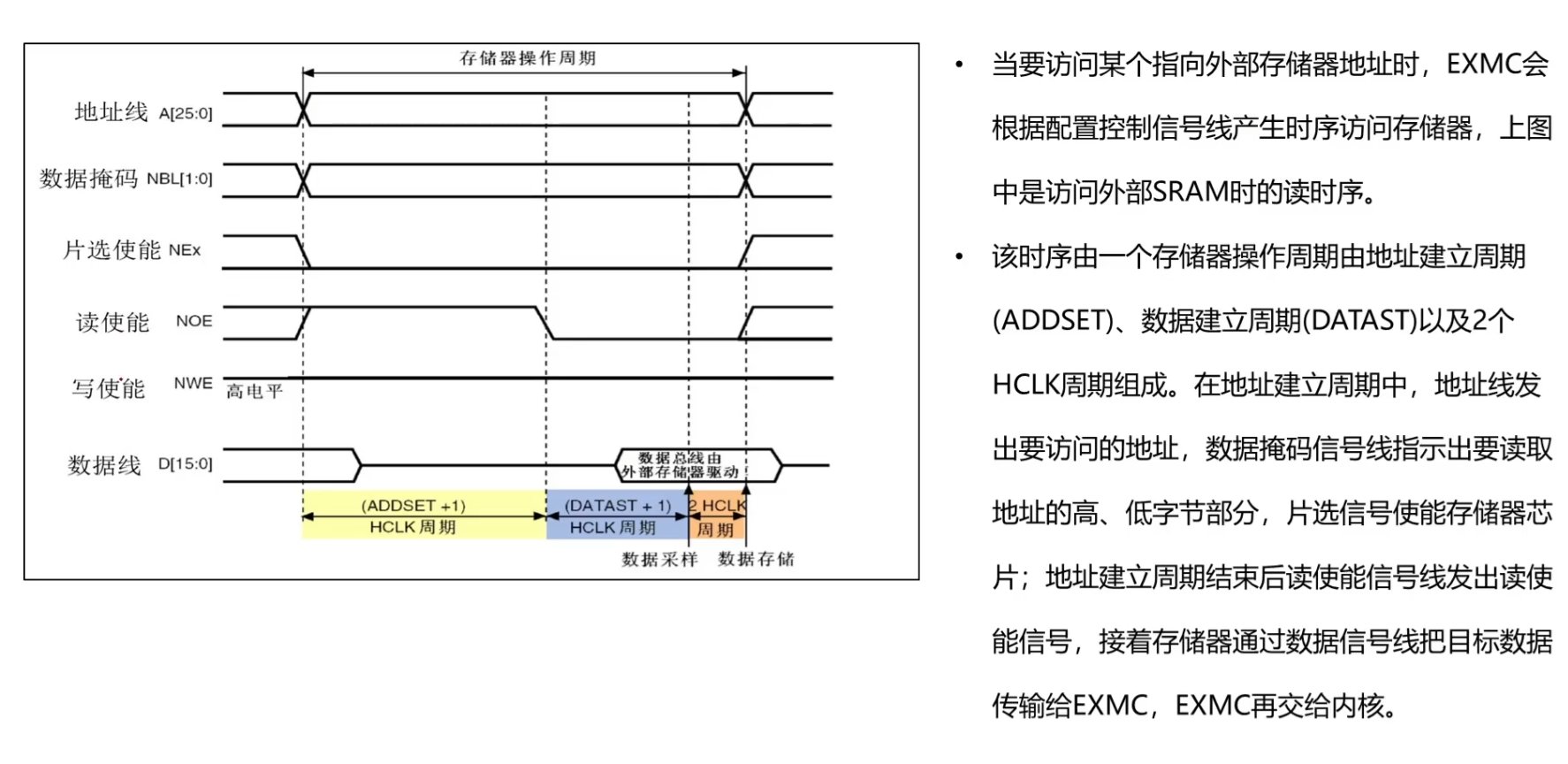

读时序

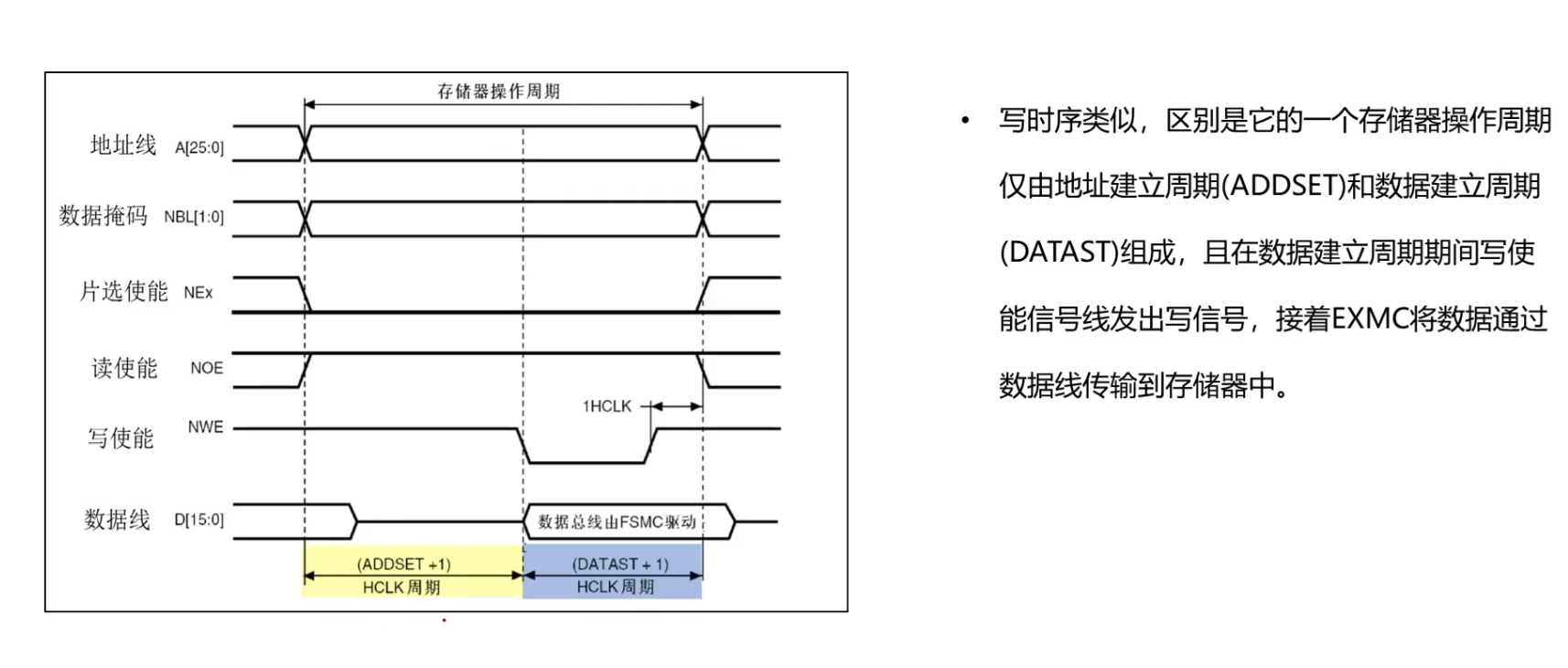

写时序

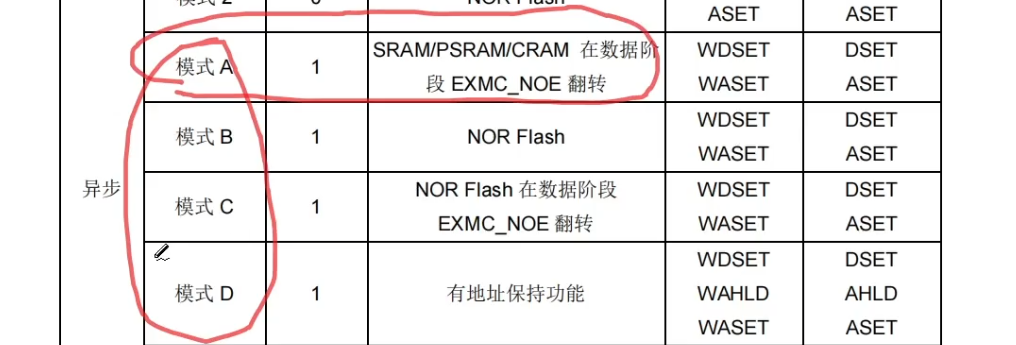

模式1

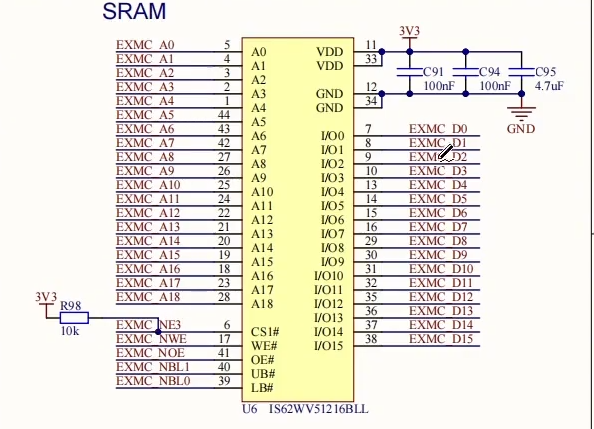

硬件

我们只使用了A0~A18共19根地址信号线,用了D0~15共16根数据信号线,块选用了NE3

驱动SRAM

exram_drv.c

#include <stdint.h>

#include <stdlib.h>

#include <stdio.h>

#include <stdbool.h>

#include "gd32f30x.h"#define BANK0_REGON3_ADDR ((uint32_t)(0x6C000000)) // Bank0 Regon3起始地址

#define EX_SRAM_BUFFER_SIZE (1 * 1024 * 1024) // 外部SRAM缓冲区大小,1M字节

#define EX_SRAM_BEGIN_ADDR (BANK0_REGON3_ADDR)

#define EX_SRAM_END_ADDR (BANK0_REGON3_ADDR + EX_SRAM_BUFFER_SIZE - 1) // 0x6C100000 - 1static void ConfigEXMCGPIO(void)

{/* 使能RCU相关时钟 */rcu_periph_clock_enable(RCU_GPIOD); //使能GPIOD的时钟rcu_periph_clock_enable(RCU_GPIOE); //使能GPIOE的时钟rcu_periph_clock_enable(RCU_GPIOF); //使能GPIOF的时钟rcu_periph_clock_enable(RCU_GPIOG); //使能GPIOG的时钟/* 地址总线 */gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_0 ); //A0gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_1 ); //A1gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_2 ); //A2gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_3 ); //A3gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_4 ); //A4gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_5 ); //A5gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_12); //A6gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_13); //A7gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_14); //A8gpio_init(GPIOF, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_15); //A9gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_0 ); //A10gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_1 ); //A11gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_2 ); //A12gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_3 ); //A13gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_4 ); //A14gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_5 ); //A15gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_11); //A16gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_12); //A17gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_13); //A18/* 数据总线 */gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_14); //D0gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_15); //D1gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_0 ); //D2gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_1 ); //D3gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_7 ); //D4gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_8 ); //D5gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_9 ); //D6gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_10); //D7gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_11); //D8gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_12); //D9gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_13); //D10gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_14); //D11gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_15); //D12gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_8 ); //D13gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_9 ); //D14gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_10); //D15/* 控制信号 */gpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_9 ); //EXMC_NE1gpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_4 ); //EXMC_NOEgpio_init(GPIOD, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_5 ); //EXMC_NWEgpio_init(GPIOG, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_12); //EXMC_NE3gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_0 ); //EXMC_NBL0gpio_init(GPIOE, GPIO_MODE_AF_PP, GPIO_OSPEED_MAX, GPIO_PIN_1 ); //EXMC_NBL1

}

/* 配置Bank0 Region3用于外部SRAM */

static void ConfigBank0Region3(void)

{exmc_norsram_parameter_struct sramInitStruct; // 定义一个外部NOR SRAM初始化结构体变量exmc_norsram_timing_parameter_struct sramTimingInitStruct; // 定义一个外部NOR SRAM时序初始化结构体变量exmc_norsram_struct_para_init(&sramInitStruct); // 使用默认参数初始化外部NOR SRAM初始化结构体/* 使能EXMC时钟 */rcu_periph_clock_enable(RCU_EXMC); // 使能外部存储器控制器(EXMC)时钟/* 配置外部SRAM读写时序 */ sramTimingInitStruct.asyn_access_mode = EXMC_ACCESS_MODE_A; // 设置为异步访问模式A,适用于异步SRAMsramTimingInitStruct.asyn_address_setuptime = 0; // 设置异步访问地址建立时间为0个HCLK周期sramTimingInitStruct.asyn_address_holdtime = 0; // 设置异步访问地址保持时间为0个HCLK周期sramTimingInitStruct.asyn_data_setuptime = 0; // 设置异步访问数据建立时间为0个HCLK周期sramTimingInitStruct.bus_latency = 0; // 设置总线延时周期为0个HCLK周期sramTimingInitStruct.syn_clk_division = 0; // 设置同步访问时钟分频系数为0,不分频sramTimingInitStruct.syn_data_latency = 0; // 设置同步访问数据潜伏期为0个HCLK周期/* 配置Region3 */sramInitStruct.norsram_region = EXMC_BANK0_NORSRAM_REGION3; // 指定配置的区域为Bank0的Region3sramInitStruct.address_data_mux = DISABLE; // 禁用地址/数据多路复用,地址和数据使用独立引脚sramInitStruct.memory_type = EXMC_MEMORY_TYPE_SRAM; // 指定外部存储器类型为SRAMsramInitStruct.databus_width = EXMC_NOR_DATABUS_WIDTH_16B; // 设置数据总线宽度为16位sramInitStruct.burst_mode = DISABLE; // 禁用突发模式sramInitStruct.nwait_config = EXMC_NWAIT_CONFIG_BEFORE; // 等待信号配置在读取/写入操作之前sramInitStruct.nwait_polarity = EXMC_NWAIT_POLARITY_LOW; // 等待信号为低电平有效sramInitStruct.wrap_burst_mode = DISABLE; // 禁用包裹突发模式sramInitStruct.asyn_wait = DISABLE; // 禁用异步等待sramInitStruct.extended_mode = DISABLE; // 禁用扩展模式(控制读时序和写时序是否分开配置)sramInitStruct.memory_write = ENABLE; // 使能写操作sramInitStruct.nwait_signal = DISABLE; // 禁用等待信号sramInitStruct.write_mode = EXMC_ASYN_WRITE; // 设置写模式为异步写sramInitStruct.read_write_timing = &sramTimingInitStruct; // 设置读写时序配置/* 初始化Region3 */exmc_norsram_init(&sramInitStruct); // 根据初始化结构体配置Bank0 Region3的外部存储器/* 使能Region3 */exmc_norsram_enable(EXMC_BANK0_NORSRAM_REGION3); // 使能Bank0 Region3,完成外部SRAM的配置

}/* 初始化外部SRAM驱动 */

void ExSramDrvInit(void)

{ConfigEXMCGPIO(); // 配置外部SRAM的GPIO引脚ConfigBank0Region3(); // 配置Bank0 Region3用于外部SRAM

}/* 定义缓冲区大小 */

#define BUFFER_SIZE 6

/* 定义并初始化缓冲区数组 */

static uint8_t g_buffer[BUFFER_SIZE] = {0, 1, 2, 3, 4, 5,};///* 定义一个具有BUFFER_SIZE大小的uint8_t类型数组g_buffer

// 并使用__attribute__((at(EX_SRAM_BEGIN_ADDR)))将该数组映射到外部SRAM的起始地址 */

//static uint8_t g_buffer[BUFFER_SIZE] __attribute__((at(EX_SRAM_BEGIN_ADDR)));/* 测试外部SRAM驱动 */

void ExSramDrvTest(void)

{printf("********************************\n");printf("********外部SRAM测试开始********\n");printf("********************************\n");/* 以下代码被注释,用于向外部SRAM写入数据 *//*printf("ex sram writing...\r\n");for (uint16_t i = 0; i < BUFFER_SIZE; i++){ g_buffer[i] = i;printf("0x%02X ", i);if (15 == i % 16){printf("\r\n");}}*/printf("ex sram reading...\r\n");/* 从外部SRAM读取数据,并与预期数据进行比较 */for (uint16_t i = 0; i < BUFFER_SIZE; i++){if (i != g_buffer[i]){printf("0x%02X ", g_buffer[i]);printf("\n\nex sram测试故障,请排查!\n\n");return;}printf("0x%02X ", g_buffer[i]);if (15 == i % 16){printf("\r\n");}}printf("********************************\n");printf("********外部SRAM测试结束********\n");printf("********************************\n");

}.h

#ifndef _EXSRAM_DRV_H_

#define _EXSRAM_DRV_H_#include <stdint.h>

#include <stdlib.h>void ExSramDrvInit(void);

void ExSramDrvTest(void);#endif

把数据地址映射到指定地址

方法一:

我们可以用__attribute__把数据映射到0x6C000000地址

/* 定义一个具有BUFFER_SIZE大小的uint8_t类型数组g_buffer并使用__attribute__((at(EX_SRAM_BEGIN_ADDR)))将该数组映射到外部SRAM的起始地址 */

static uint8_t g_buffer[BUFFER_SIZE] __attribute__((at(EX_SRAM_BEGIN_ADDR)));方法二:

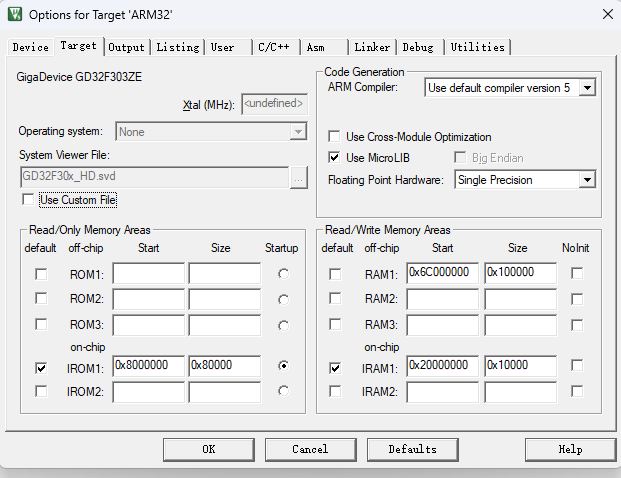

我们打开魔术棒在RAM里面添加

不要勾选,要是勾选,编译器会认为RAM1是主内存,不是单片机内部的内存,栈的地址也会变成0x6c000000开始,也就是分配到了外部的SRAM芯片上了,勾选会影响sct文件(分散加载文件)

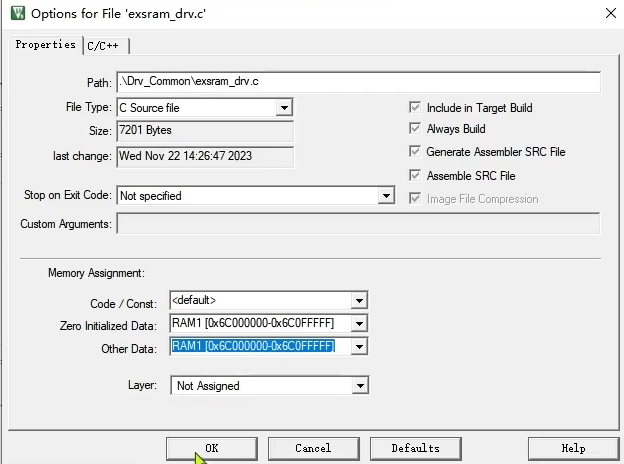

我们对exsram_drv.c右键选择第一个

选择我们刚添加的地址

这时候我们在exsram_drv.c里创建的g_buffer[BUFFER_SIZE]的地址就会变成0x6C000000(所有静态全局变量)

我们可不可以直接给数值赋值呢?像这样

static uint8_t g_buffer[BUFFER_SIZE] = {0, 1, 2, 3, 4, 5,};

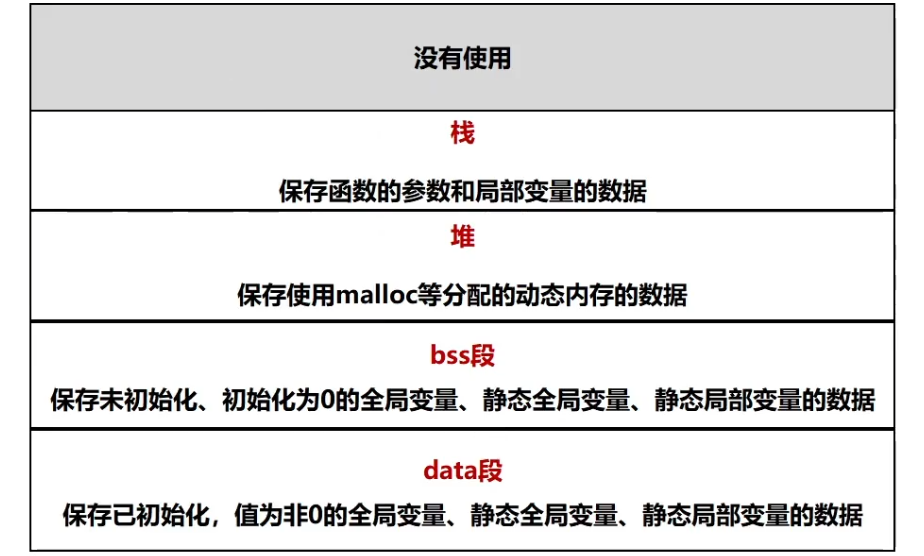

答案是可以,但是有问题,虽然说我们exram这个文件的静态全局变量的地址从0x6C000000开始,但是我们的全局变量已经初始化了(赋值),所以会放到RW区(flash)

在__main函数会把全局变量(已赋值)的数据拷贝到内存当中,再去执行我们写的main函数,

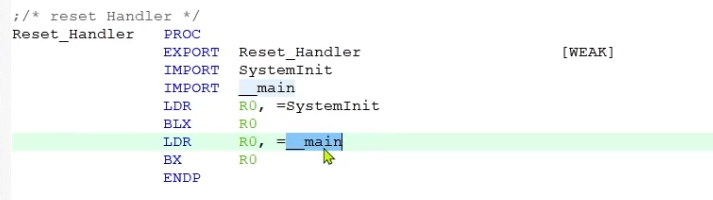

所以我们要在__main函数之前初始化exsram

我们发现SystmeInit在__main之前,那我们就在SystmeInit初始化exsram

打开![]() 然后添加

然后添加

/*!\file system_gd32f30x.c\brief CMSIS Cortex-M4 Device Peripheral Access Layer Source File forGD32F30x Device Series

*//* Copyright (c) 2012 ARM LIMITEDAll rights reserved.Redistribution and use in source and binary forms, with or withoutmodification, are permitted provided that the following conditions are met:- Redistributions of source code must retain the above copyrightnotice, this list of conditions and the following disclaimer.- Redistributions in binary form must reproduce the above copyrightnotice, this list of conditions and the following disclaimer in thedocumentation and/or other materials provided with the distribution.- Neither the name of ARM nor the names of its contributors may be usedto endorse or promote products derived from this software withoutspecific prior written permission.*THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THEIMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSEARE DISCLAIMED. IN NO EVENT SHALL COPYRIGHT HOLDERS AND CONTRIBUTORS BELIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, ORCONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OFSUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESSINTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER INCONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE)ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THEPOSSIBILITY OF SUCH DAMAGE.---------------------------------------------------------------------------*/

/* This file refers the CMSIS standard, some adjustments are made according to GigaDevice chips */#include "gd32f30x.h"

#include "exsram_drv.h"

/* system frequency define */

#define __IRC8M (IRC8M_VALUE) /* internal 8 MHz RC oscillator frequency */

#define __HXTAL (HXTAL_VALUE) /* high speed crystal oscillator frequency */

#define __SYS_OSC_CLK (__IRC8M) /* main oscillator frequency *//* select a system clock by uncommenting the following line */

/* use IRC8M */

//#define __SYSTEM_CLOCK_IRC8M (uint32_t)(__IRC8M)

//#define __SYSTEM_CLOCK_48M_PLL_IRC8M (uint32_t)(48000000)

//#define __SYSTEM_CLOCK_72M_PLL_IRC8M (uint32_t)(72000000)

//#define __SYSTEM_CLOCK_108M_PLL_IRC8M (uint32_t)(108000000)

//#define __SYSTEM_CLOCK_120M_PLL_IRC8M (uint32_t)(120000000)/* use HXTAL(XD series CK_HXTAL = 8M, CL series CK_HXTAL = 25M) */

//#define __SYSTEM_CLOCK_HXTAL (uint32_t)(__HXTAL)

//#define __SYSTEM_CLOCK_48M_PLL_HXTAL (uint32_t)(48000000)

//#define __SYSTEM_CLOCK_72M_PLL_HXTAL (uint32_t)(72000000)

//#define __SYSTEM_CLOCK_108M_PLL_HXTAL (uint32_t)(108000000)

#define __SYSTEM_CLOCK_120M_PLL_HXTAL (uint32_t)(120000000)#define RCU_MODIFY(__delay) do{ \volatile uint32_t i; \if(0 != __delay){ \RCU_CFG0 |= RCU_AHB_CKSYS_DIV2; \for(i=0; i<__delay; i++){ \} \RCU_CFG0 |= RCU_AHB_CKSYS_DIV4; \for(i=0; i<__delay; i++){ \} \} \}while(0)#define SEL_IRC8M 0x00U

#define SEL_HXTAL 0x01U

#define SEL_PLL 0x02U/* set the system clock frequency and declare the system clock configuration function */

#ifdef __SYSTEM_CLOCK_IRC8M

uint32_t SystemCoreClock = __SYSTEM_CLOCK_IRC8M;

static void system_clock_8m_irc8m(void);

#elif defined (__SYSTEM_CLOCK_48M_PLL_IRC8M)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_48M_PLL_IRC8M;

static void system_clock_48m_irc8m(void);

#elif defined (__SYSTEM_CLOCK_72M_PLL_IRC8M)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_72M_PLL_IRC8M;

static void system_clock_72m_irc8m(void);

#elif defined (__SYSTEM_CLOCK_108M_PLL_IRC8M)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_108M_PLL_IRC8M;

static void system_clock_108m_irc8m(void);

#elif defined (__SYSTEM_CLOCK_120M_PLL_IRC8M)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_120M_PLL_IRC8M;

static void system_clock_120m_irc8m(void);#elif defined (__SYSTEM_CLOCK_HXTAL)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_HXTAL;

static void system_clock_hxtal(void);

#elif defined (__SYSTEM_CLOCK_48M_PLL_HXTAL)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_48M_PLL_HXTAL;

static void system_clock_48m_hxtal(void);

#elif defined (__SYSTEM_CLOCK_72M_PLL_HXTAL)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_72M_PLL_HXTAL;

static void system_clock_72m_hxtal(void);

#elif defined (__SYSTEM_CLOCK_108M_PLL_HXTAL)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_108M_PLL_HXTAL;

static void system_clock_108m_hxtal(void);

#elif defined (__SYSTEM_CLOCK_120M_PLL_HXTAL)

uint32_t SystemCoreClock = __SYSTEM_CLOCK_120M_PLL_HXTAL;

static void system_clock_120m_hxtal(void);

#endif /* __SYSTEM_CLOCK_IRC8M *//* configure the system clock */

static void system_clock_config(void);/*!\brief setup the microcontroller system, initialize the system\param[in] none\param[out] none\retval none

*/

void SystemInit (void)

{/* FPU settings */

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)SCB->CPACR |= ((3UL << 10*2)|(3UL << 11*2)); /* set CP10 and CP11 Full Access */

#endif/* reset the RCU clock configuration to the default reset state *//* Set IRC8MEN bit */RCU_CTL |= RCU_CTL_IRC8MEN;while(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){}RCU_MODIFY(0x50);RCU_CFG0 &= ~RCU_CFG0_SCS;#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))/* reset HXTALEN, CKMEN and PLLEN bits */RCU_CTL &= ~(RCU_CTL_PLLEN | RCU_CTL_CKMEN | RCU_CTL_HXTALEN);/* disable all interrupts */RCU_INT = 0x009f0000U;

#elif defined(GD32F30X_CL)/* Reset HXTALEN, CKMEN, PLLEN, PLL1EN and PLL2EN bits */RCU_CTL &= ~(RCU_CTL_PLLEN |RCU_CTL_PLL1EN | RCU_CTL_PLL2EN | RCU_CTL_CKMEN | RCU_CTL_HXTALEN);/* disable all interrupts */RCU_INT = 0x00ff0000U;

#endif/* reset HXTALBPS bit */RCU_CTL &= ~(RCU_CTL_HXTALBPS);/* Reset CFG0 and CFG1 registers */RCU_CFG0 = 0x00000000U;RCU_CFG1 = 0x00000000U;/* configure the system clock source, PLL Multiplier, AHB/APBx prescalers and Flash settings */system_clock_config();ExSramDrvInit();

}

/*!\brief configure the system clock\param[in] none\param[out] none\retval none

*/

static void system_clock_config(void)

{

#ifdef __SYSTEM_CLOCK_IRC8Msystem_clock_8m_irc8m();

#elif defined (__SYSTEM_CLOCK_48M_PLL_IRC8M)system_clock_48m_irc8m();

#elif defined (__SYSTEM_CLOCK_72M_PLL_IRC8M)system_clock_72m_irc8m();

#elif defined (__SYSTEM_CLOCK_108M_PLL_IRC8M)system_clock_108m_irc8m();

#elif defined (__SYSTEM_CLOCK_120M_PLL_IRC8M)system_clock_120m_irc8m();#elif defined (__SYSTEM_CLOCK_HXTAL)system_clock_hxtal();

#elif defined (__SYSTEM_CLOCK_48M_PLL_HXTAL)system_clock_48m_hxtal();

#elif defined (__SYSTEM_CLOCK_72M_PLL_HXTAL)system_clock_72m_hxtal();

#elif defined (__SYSTEM_CLOCK_108M_PLL_HXTAL)system_clock_108m_hxtal();

#elif defined (__SYSTEM_CLOCK_120M_PLL_HXTAL)system_clock_120m_hxtal();

#endif /* __SYSTEM_CLOCK_IRC8M */

}#ifdef __SYSTEM_CLOCK_IRC8M

/*!\brief configure the system clock to 8M by IRC8M\param[in] none\param[out] none\retval none

*/

static void system_clock_8m_irc8m(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable IRC8M */RCU_CTL |= RCU_CTL_IRC8MEN;/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_IRC8MSTB);}while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){while(1){}}/* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* select IRC8M as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_IRC8M;/* wait until IRC8M is selected as system clock */while(0U != (RCU_CFG0 & RCU_SCSS_IRC8M)){}

}#elif defined (__SYSTEM_CLOCK_48M_PLL_IRC8M)

/*!\brief configure the system clock to 48M by PLL which selects IRC8M as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_48m_irc8m(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable IRC8M */RCU_CTL |= RCU_CTL_IRC8MEN;/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_IRC8MSTB);}while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){while(1){}}/* LDO output voltage high mode */RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* IRC8M is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* CK_PLL = (CK_IRC8M/2) * 12 = 48 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL12;/* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){} /* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_72M_PLL_IRC8M)

/*!\brief configure the system clock to 72M by PLL which selects IRC8M as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_72m_irc8m(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable IRC8M */RCU_CTL |= RCU_CTL_IRC8MEN;/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_IRC8MSTB);}while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){while(1){}}/* LDO output voltage high mode */RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* IRC8M is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* CK_PLL = (CK_IRC8M/2) * 18 = 72 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL18;/* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_108M_PLL_IRC8M)

/*!\brief configure the system clock to 108M by PLL which selects IRC8M as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_108m_irc8m(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable IRC8M */RCU_CTL |= RCU_CTL_IRC8MEN;/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_IRC8MSTB);}while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){while(1){}}/* LDO output voltage high mode */RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* IRC8M is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* CK_PLL = (CK_IRC8M/2) * 27 = 108 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL27;/* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_120M_PLL_IRC8M)

/*!\brief configure the system clock to 120M by PLL which selects IRC8M as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_120m_irc8m(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable IRC8M */RCU_CTL |= RCU_CTL_IRC8MEN;/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_IRC8MSTB);}while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_IRC8MSTB)){while(1){}}/* LDO output voltage high mode */RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* IRC8M is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* CK_PLL = (CK_IRC8M/2) * 30 = 120 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL30;/* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_HXTAL)

/*!\brief configure the system clock to HXTAL\param[in] none\param[out] none\retval none

*/

static void system_clock_hxtal(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable HXTAL */RCU_CTL |= RCU_CTL_HXTALEN;/* wait until HXTAL is stable or the startup time is longer than HXTAL_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_HXTALSTB);}while((0U == stab_flag) && (HXTAL_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_HXTALSTB)){while(1){}}/* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;/* select HXTAL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_HXTAL;/* wait until HXTAL is selected as system clock */while(0 == (RCU_CFG0 & RCU_SCSS_HXTAL)){}

}#elif defined (__SYSTEM_CLOCK_48M_PLL_HXTAL)

/*!\brief configure the system clock to 48M by PLL which selects HXTAL(8M) as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_48m_hxtal(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable HXTAL */RCU_CTL |= RCU_CTL_HXTALEN;/* wait until HXTAL is stable or the startup time is longer than HXTAL_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_HXTALSTB);}while((0U == stab_flag) && (HXTAL_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_HXTALSTB)){while(1){}}RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* HXTAL is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))/* select HXTAL/2 as clock source */RCU_CFG0 &= ~(RCU_CFG0_PLLSEL | RCU_CFG0_PREDV0);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_CFG0_PREDV0);/* CK_PLL = (CK_HXTAL/2) * 12 = 48 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL12;#elif defined(GD32F30X_CL)/* CK_PLL = (CK_PREDIV0) * 12 = 48 MHz */ RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_PLL_MUL12);/* CK_PREDIV0 = (CK_HXTAL)/5 *8 /10 = 4 MHz */ RCU_CFG1 &= ~(RCU_CFG1_PLLPRESEL | RCU_CFG1_PREDV0SEL | RCU_CFG1_PLL1MF | RCU_CFG1_PREDV1 | RCU_CFG1_PREDV0);RCU_CFG1 |= (RCU_PLLPRESRC_HXTAL | RCU_PREDV0SRC_CKPLL1 | RCU_PLL1_MUL8 | RCU_PREDV1_DIV5 | RCU_PREDV0_DIV10);/* enable PLL1 */RCU_CTL |= RCU_CTL_PLL1EN;/* wait till PLL1 is ready */while((RCU_CTL & RCU_CTL_PLL1STB) == 0){}

#endif /* GD32F30X_HD and GD32F30X_XD *//* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}

#elif defined (__SYSTEM_CLOCK_72M_PLL_HXTAL)

/*!\brief configure the system clock to 72M by PLL which selects HXTAL(8M) as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_72m_hxtal(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable HXTAL */RCU_CTL |= RCU_CTL_HXTALEN;/* wait until HXTAL is stable or the startup time is longer than HXTAL_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_HXTALSTB);}while((0U == stab_flag) && (HXTAL_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_HXTALSTB)){while(1){}}RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* HXTAL is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))/* select HXTAL/2 as clock source */RCU_CFG0 &= ~(RCU_CFG0_PLLSEL | RCU_CFG0_PREDV0);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_CFG0_PREDV0);/* CK_PLL = (CK_HXTAL/2) * 18 = 72 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL18;#elif defined(GD32F30X_CL)/* CK_PLL = (CK_PREDIV0) * 18 = 72 MHz */ RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_PLL_MUL18);/* CK_PREDIV0 = (CK_HXTAL)/5 *8 /10 = 4 MHz */ RCU_CFG1 &= ~(RCU_CFG1_PLLPRESEL | RCU_CFG1_PREDV0SEL | RCU_CFG1_PLL1MF | RCU_CFG1_PREDV1 | RCU_CFG1_PREDV0);RCU_CFG1 |= (RCU_PLLPRESRC_HXTAL | RCU_PREDV0SRC_CKPLL1 | RCU_PLL1_MUL8 | RCU_PREDV1_DIV5 | RCU_PREDV0_DIV10);/* enable PLL1 */RCU_CTL |= RCU_CTL_PLL1EN;/* wait till PLL1 is ready */while((RCU_CTL & RCU_CTL_PLL1STB) == 0){}

#endif /* GD32F30X_HD and GD32F30X_XD *//* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_108M_PLL_HXTAL)

/*!\brief configure the system clock to 108M by PLL which selects HXTAL(8M) as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_108m_hxtal(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable HXTAL */RCU_CTL |= RCU_CTL_HXTALEN;/* wait until HXTAL is stable or the startup time is longer than HXTAL_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_HXTALSTB);}while((0U == stab_flag) && (HXTAL_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_HXTALSTB)){while(1){}}RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* HXTAL is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))/* select HXTAL/2 as clock source */RCU_CFG0 &= ~(RCU_CFG0_PLLSEL | RCU_CFG0_PREDV0);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_CFG0_PREDV0);/* CK_PLL = (CK_HXTAL/2) * 27 = 108 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL27;#elif defined(GD32F30X_CL)/* CK_PLL = (CK_PREDIV0) * 27 = 108 MHz */ RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_PLL_MUL27);/* CK_PREDIV0 = (CK_HXTAL)/5 *8 /10 = 4 MHz */ RCU_CFG1 &= ~(RCU_CFG1_PLLPRESEL | RCU_CFG1_PREDV0SEL | RCU_CFG1_PLL1MF | RCU_CFG1_PREDV1 | RCU_CFG1_PREDV0);RCU_CFG1 |= (RCU_PLLPRESRC_HXTAL | RCU_PREDV0SRC_CKPLL1 | RCU_PLL1_MUL8 | RCU_PREDV1_DIV5 | RCU_PREDV0_DIV10);/* enable PLL1 */RCU_CTL |= RCU_CTL_PLL1EN;/* wait till PLL1 is ready */while((RCU_CTL & RCU_CTL_PLL1STB) == 0){}

#endif /* GD32F30X_HD and GD32F30X_XD *//* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}#elif defined (__SYSTEM_CLOCK_120M_PLL_HXTAL)

/*!\brief configure the system clock to 120M by PLL which selects HXTAL(8M) as its clock source\param[in] none\param[out] none\retval none

*/

static void system_clock_120m_hxtal(void)

{uint32_t timeout = 0U;uint32_t stab_flag = 0U;/* enable HXTAL */RCU_CTL |= RCU_CTL_HXTALEN;/* wait until HXTAL is stable or the startup time is longer than HXTAL_STARTUP_TIMEOUT */do{timeout++;stab_flag = (RCU_CTL & RCU_CTL_HXTALSTB);}while((0U == stab_flag) && (HXTAL_STARTUP_TIMEOUT != timeout));/* if fail */if(0U == (RCU_CTL & RCU_CTL_HXTALSTB)){while(1){}}RCU_APB1EN |= RCU_APB1EN_PMUEN;PMU_CTL |= PMU_CTL_LDOVS;/* HXTAL is stable *//* AHB = SYSCLK */RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;/* APB2 = AHB/1 */RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;/* APB1 = AHB/2 */RCU_CFG0 |= RCU_APB1_CKAHB_DIV2;#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))/* select HXTAL/2 as clock source */RCU_CFG0 &= ~(RCU_CFG0_PLLSEL | RCU_CFG0_PREDV0);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_CFG0_PREDV0);/* CK_PLL = (CK_HXTAL/2) * 30 = 120 MHz */RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= RCU_PLL_MUL30;#elif defined(GD32F30X_CL)/* CK_PLL = (CK_PREDIV0) * 30 = 120 MHz */ RCU_CFG0 &= ~(RCU_CFG0_PLLMF | RCU_CFG0_PLLMF_4 | RCU_CFG0_PLLMF_5);RCU_CFG0 |= (RCU_PLLSRC_HXTAL_IRC48M | RCU_PLL_MUL30);/* CK_PREDIV0 = (CK_HXTAL)/5 *8 /10 = 4 MHz */ RCU_CFG1 &= ~(RCU_CFG1_PLLPRESEL | RCU_CFG1_PREDV0SEL | RCU_CFG1_PLL1MF | RCU_CFG1_PREDV1 | RCU_CFG1_PREDV0);RCU_CFG1 |= (RCU_PLLPRESRC_HXTAL | RCU_PREDV0SRC_CKPLL1 | RCU_PLL1_MUL8 | RCU_PREDV1_DIV5 | RCU_PREDV0_DIV10);/* enable PLL1 */RCU_CTL |= RCU_CTL_PLL1EN;/* wait till PLL1 is ready */while((RCU_CTL & RCU_CTL_PLL1STB) == 0U){}

#endif /* GD32F30X_HD and GD32F30X_XD *//* enable PLL */RCU_CTL |= RCU_CTL_PLLEN;/* wait until PLL is stable */while(0U == (RCU_CTL & RCU_CTL_PLLSTB)){}/* enable the high-drive to extend the clock frequency to 120 MHz */PMU_CTL |= PMU_CTL_HDEN;while(0U == (PMU_CS & PMU_CS_HDRF)){}/* select the high-drive mode */PMU_CTL |= PMU_CTL_HDS;while(0U == (PMU_CS & PMU_CS_HDSRF)){}/* select PLL as system clock */RCU_CFG0 &= ~RCU_CFG0_SCS;RCU_CFG0 |= RCU_CKSYSSRC_PLL;/* wait until PLL is selected as system clock */while(0U == (RCU_CFG0 & RCU_SCSS_PLL)){}

}

#endif /* __SYSTEM_CLOCK_IRC8M *//*!\brief update the SystemCoreClock with current core clock retrieved from cpu registers\param[in] none\param[out] none\retval none

*/

void SystemCoreClockUpdate(void)

{uint32_t sws;uint32_t pllsel, pllpresel, predv0sel, pllmf, ck_src, idx, clk_exp;/* exponent of AHB, APB1 and APB2 clock divider */const uint8_t ahb_exp[16] = {0, 0, 0, 0, 0, 0, 0, 0, 1, 2, 3, 4, 6, 7, 8, 9};

#ifdef GD32F30X_CLuint32_t predv0, predv1, pll1mf;

#endif /* GD32F30X_CL */sws = GET_BITS(RCU_CFG0, 2, 3);switch(sws){/* IRC8M is selected as CK_SYS */case SEL_IRC8M:SystemCoreClock = IRC8M_VALUE;break;/* HXTAL is selected as CK_SYS */case SEL_HXTAL:SystemCoreClock = HXTAL_VALUE;break;/* PLL is selected as CK_SYS */case SEL_PLL:/* PLL clock source selection, HXTAL, IRC48M or IRC8M/2 */pllsel = (RCU_CFG0 & RCU_CFG0_PLLSEL);if(RCU_PLLSRC_HXTAL_IRC48M == pllsel){/* PLL clock source is HXTAL or IRC48M */pllpresel = (RCU_CFG1 & RCU_CFG1_PLLPRESEL);if(RCU_PLLPRESRC_HXTAL == pllpresel){/* PLL clock source is HXTAL */ck_src = HXTAL_VALUE;}else{/* PLL clock source is IRC48 */ck_src = IRC48M_VALUE;}#if (defined(GD32F30X_HD) || defined(GD32F30X_XD))predv0sel = (RCU_CFG0 & RCU_CFG0_PREDV0);/* PREDV0 input source clock divided by 2 */if(RCU_CFG0_PREDV0 == predv0sel){ck_src /= 2U;}

#elif defined(GD32F30X_CL)predv0sel = (RCU_CFG1 & RCU_CFG1_PREDV0SEL);/* source clock use PLL1 */if(RCU_PREDV0SRC_CKPLL1 == predv0sel){predv1 = ((RCU_CFG1 & RCU_CFG1_PREDV1) >> 4) + 1U;pll1mf = ((RCU_CFG1 & RCU_CFG1_PLL1MF) >> 8) + 2U;if(17U == pll1mf){pll1mf = 20U;}ck_src = (ck_src / predv1) * pll1mf;}predv0 = (RCU_CFG1 & RCU_CFG1_PREDV0) + 1U;ck_src /= predv0;

#endif /* GD32F30X_HD and GD32F30X_XD */}else{/* PLL clock source is IRC8M/2 */ck_src = IRC8M_VALUE / 2U;}/* PLL multiplication factor */pllmf = GET_BITS(RCU_CFG0, 18, 21);if((RCU_CFG0 & RCU_CFG0_PLLMF_4)){pllmf |= 0x10U;}if((RCU_CFG0 & RCU_CFG0_PLLMF_5)){pllmf |= 0x20U;}if( pllmf >= 15U){pllmf += 1U;}else{pllmf += 2U;}if(pllmf > 61U){pllmf = 63U;}SystemCoreClock = ck_src * pllmf;#ifdef GD32F30X_CLif(15U == pllmf){SystemCoreClock = (ck_src * 6U) + (ck_src / 2U);}#endif /* GD32F30X_CL */break;/* IRC8M is selected as CK_SYS */default:SystemCoreClock = IRC8M_VALUE;break;}/* calculate AHB clock frequency */idx = GET_BITS(RCU_CFG0, 4, 7);clk_exp = ahb_exp[idx];SystemCoreClock = SystemCoreClock >> clk_exp;

}

设置好后的sct文件