The Xilinx 7 series FPGAs 设计PCB 该选择绑定哪个bank引脚,约束引脚时如何定义引脚电平标准?

写作目的:由于项目需求,需要将原有的16位AD转换芯片替换为24位的AD转换芯片。除了涉及驱动代码的修改外,本次工程还包括了原理图的更新以及引脚电平标准的选择。本篇文章主要记录了这一学习过程,并详细阐述了相关的技术细节与设计思路。

1.原理图更新

1.1 The Xilinx 7 series FPGAs 芯片类型

在此之前,还没有去了解过FPGA芯片的组成结构,所以这几天在了解。

Xilinx 7 系列 FPGA 是基于 28nm 工艺技术的 FPGA 产品系列, 分为四个子系列。每个子系列在性能、功耗、尺寸和设计难度等方面各具特点,适用于不同的应用场景。下面是四个子系列的介绍:

Spartan-7 系列:作为 7 系列中最基础的型号,Spartan-7 提供了最低的价格、最低的功耗、最小的尺寸以及最简单的设计难度,非常适合低端应用。其优异的性价比使其在入门级市场中非常受欢迎,特别适用于需要基本逻辑处理、低功耗和紧凑尺寸的嵌入式系统。

Artix-7 系列:相较于 Spartan-7 系列,Artix-7 在功能上有所提升,增加了串行收发器和 DSP 功能,且提供了更大的逻辑容量。它适用于需要一定处理能力和数据传输速率的中端应用,如通信、图像处理和高性能嵌入式系统。

Kintex-7 系列:Kintex-7 是 7 系列中性价比最佳的型号。无论是硬核数量、逻辑容量,还是数据处理能力,都能很好地满足中低端及部分高端应用的需求。其优秀的平衡性能使其在很多中等到较复杂的应用中成为理想选择,如视频处理、数字信号处理和高性能计算等。

Virtex-7 系列:作为 7 系列中的旗舰产品,Virtex-7 适用于高端应用,提供了最强大的性能和最大容量。在中低端应用中,使用 Virtex-7 就像是“大材小用”,因此其主要应用于需要极高计算能力和资源的领域,如数据中心、5G 通信、航空航天和高端图像处理等。

每个子系列的 FPGA 都包含多个不同的 Bank,每个 Bank 都可以配置为不同的电压、I/O 标准和输入输出功能。通过合理地配置不同 Bank 的引脚,可以在电路设计中灵活地实现各种接口和信号处理需求。在电路设计过程中,我们只需要根据实际需求,利用不同 Bank 中的引脚来实现对应的功能即可。所以要想会设计FPGA板子,我们要先了解这块板子有哪些bank,每块bank的作用是什么(一般不同类型的芯片同一bank的作用是相同的,比如说bank0都是用作配置,引脚是相同的)。

1.2 Bank

为了适应不同的电气标准并便于管理,FPGA 的 I/O 部分被划分成多个 Bank。每个 Bank 包含一组具有相似电气特性和物理位置的 I/O 引脚,其接口标准由该 Bank 的 VCCIO 电压确定。每个 Bank 内部的所有引脚都共享同一个 VCCIO 电压,但不同 Bank 之间的 VCCIO 电压可以不同。为了保证接口标准的一致性,同一 Bank 中的引脚必须使用相同的电压标准。因此,通过为不同的 Bank 设置不同的电压基准,可以实现支持多种电平标准的输入输出。一般来说,FPGA 的封装越大,支持的 Bank 数量也越多,从而能够支持更多的电压标准。在 7 系列 FPGA 中,主要划分了 HP Bank 和 HR Bank,而在更高端的 UltraScale FPGA 中,除了 HP 和 HR Bank 之外,还引入了 HD Bank。需要注意的是,并不是所有 FPGA 都会同时包含这三种 Bank 类型。以下是这几种bank的说明:

| Bank 类型 | VCCIO 电压范围 | 特性描述 | 应用场景 | 常见的 FPGA 系列 |

|---|---|---|---|---|

| HP Bank | 最大为1.8V | 高性能 Bank,支持高速信号传输、低延迟,适合处理高带宽的数据。支持高速 I/O 标准如 LVDS、HSTL、SSTL 等。因为传输速率比较高,Bank电压最高也只能到1.8V。 | 主要用于高速数据接口,如 DDR 内存接口、SerDes、LVDS 信号等。 | 7 系列、UltraScale、UltraScale+ 系列 |

| HR Bank | 最大为3.3V | 提供更广泛的电压兼容性,支持更高电压的 I/O 接口,适用于兼容多种电平标准的应用。 | 用于连接不同电压标准的外设,如传感器、外部总线等,适合多电压环境下的接口设计。 | 7 系列、UltraScale、UltraScale+ 系列 |

| HD Bank | 最大为3.3V | 应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V。 | 适用于高功率要求的应用,如高电压电流输出、外设接口需要更大驱动能力时。 | UltraScale、UltraScale+ 系列 |

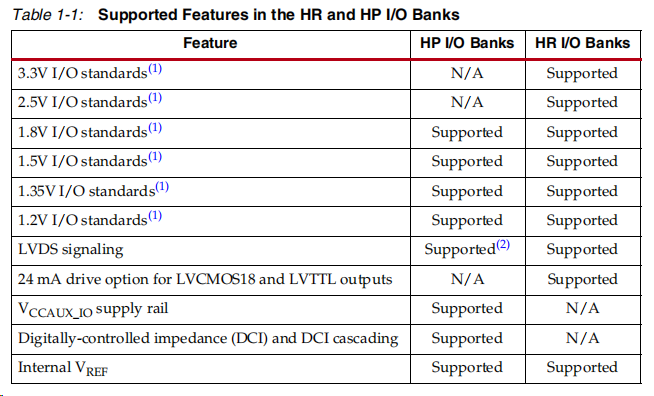

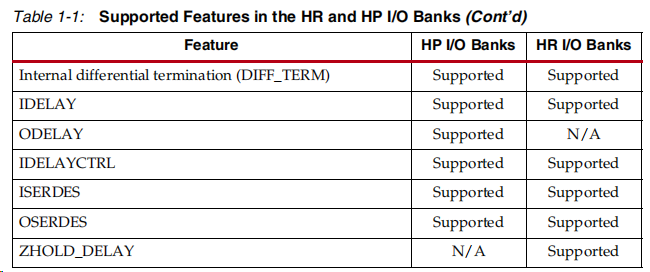

表 1-1 列出了 HP 和 HR I/O Bank 支持的特性(ug471_ Select IO Resources.pdf)。

根据表1数据,HP bank支持1.2V、1.35V和1.8V三种电压配置,而HR bank则兼容1.2V、1.35V、1.8V、2.5V和3.3V五种电压规格。设计时需特别注意I/O端口的工作电压范围,避免因电压选择不当导致FPGA功能异常。

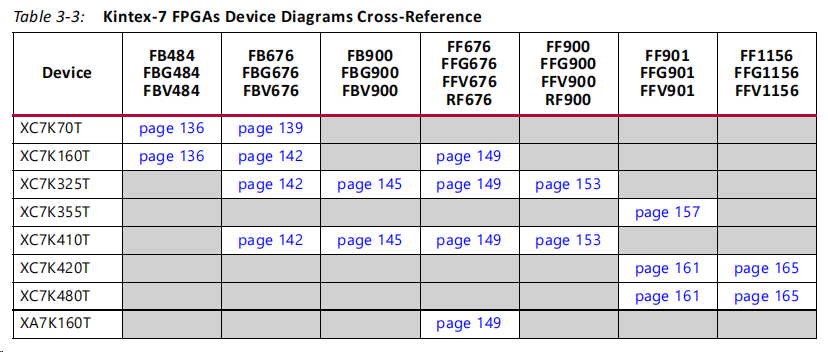

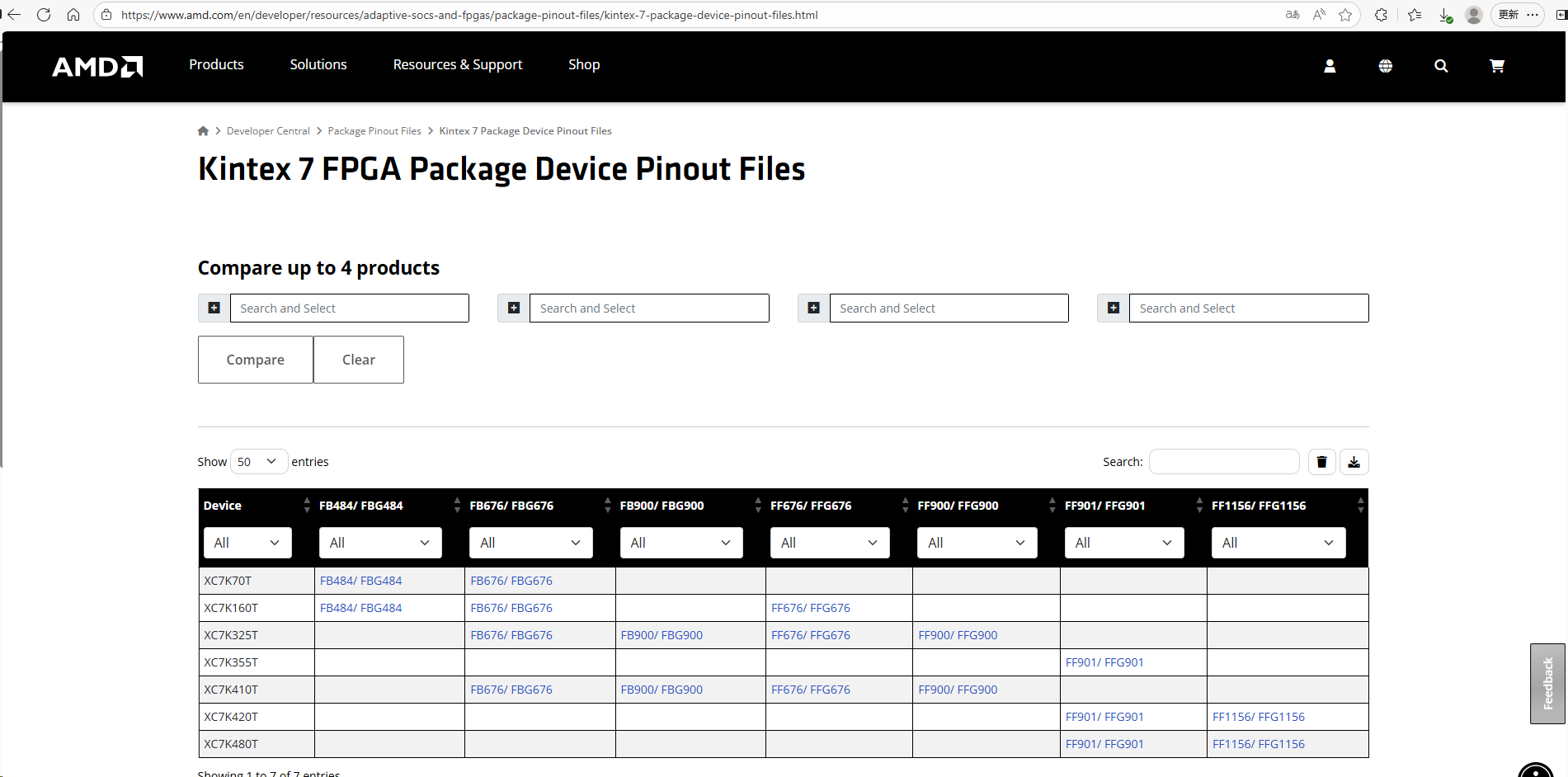

不同FPGA 芯片具有不同的bank数量,而Xilinx 7 系列的芯片的bank数量和类型可以在ug475_Packaging and Pinout.pdf中找到。以Kintex‐7系列为例子。K7系列有以下芯片:

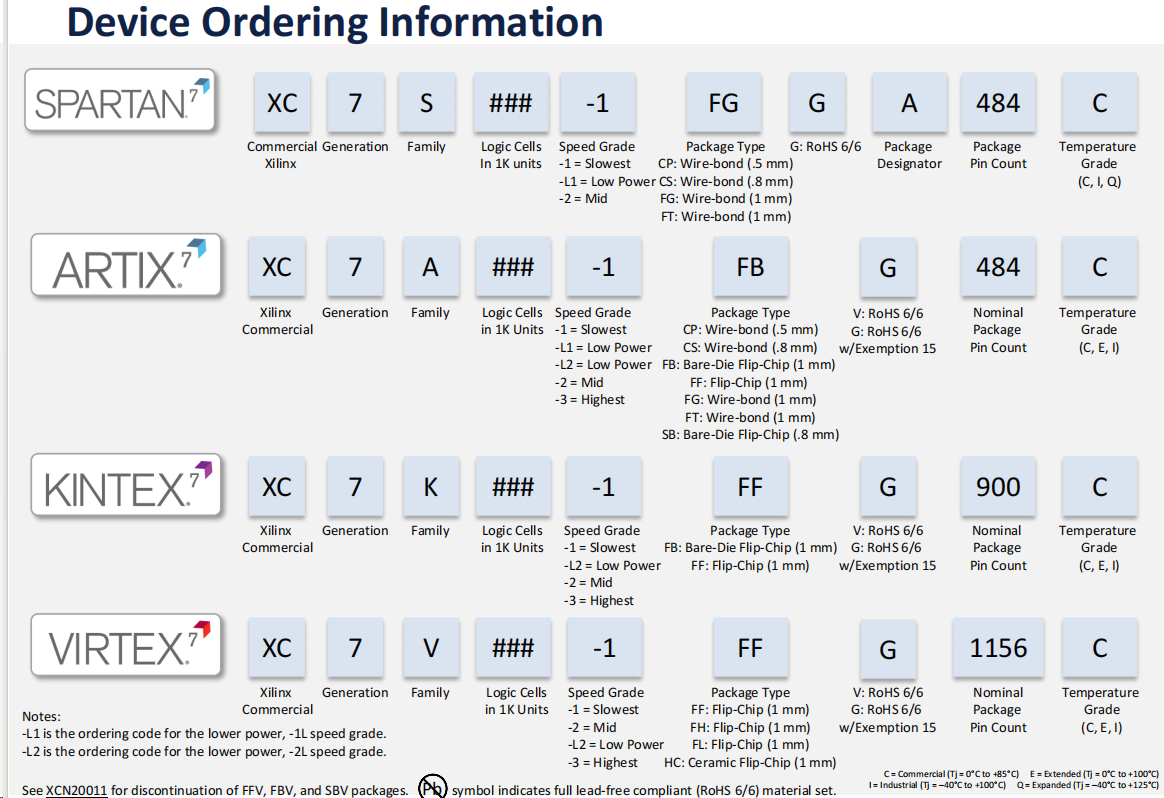

这里简单说明一下,器件的命名方式(7-series-product-selection-guide.pdf),如下图所示:

以XC7K325T-1FFG900C为例:

XC:xilinx CommercialXilinx(赛灵思商业级器件)

7:7系列

K:Kintex系列,A:ARTIX 系列,K:KINTEX系列,V:VIRTEX 系列,Z:ZYNQ7OOO系列

160:逻辑资源(logic cells)数目这个数字乘以1000就是该器件大致的资源数量,只是大致,并不准确.

1:速度等级(数字越大速度等级越高)3最高,1最低,带L的表示该器件是低功耗器件(低功耗器件的供电电压比普通器件更低)

FF:封装方式

G:无铅

900:引脚数

C/E//Q:温度等级

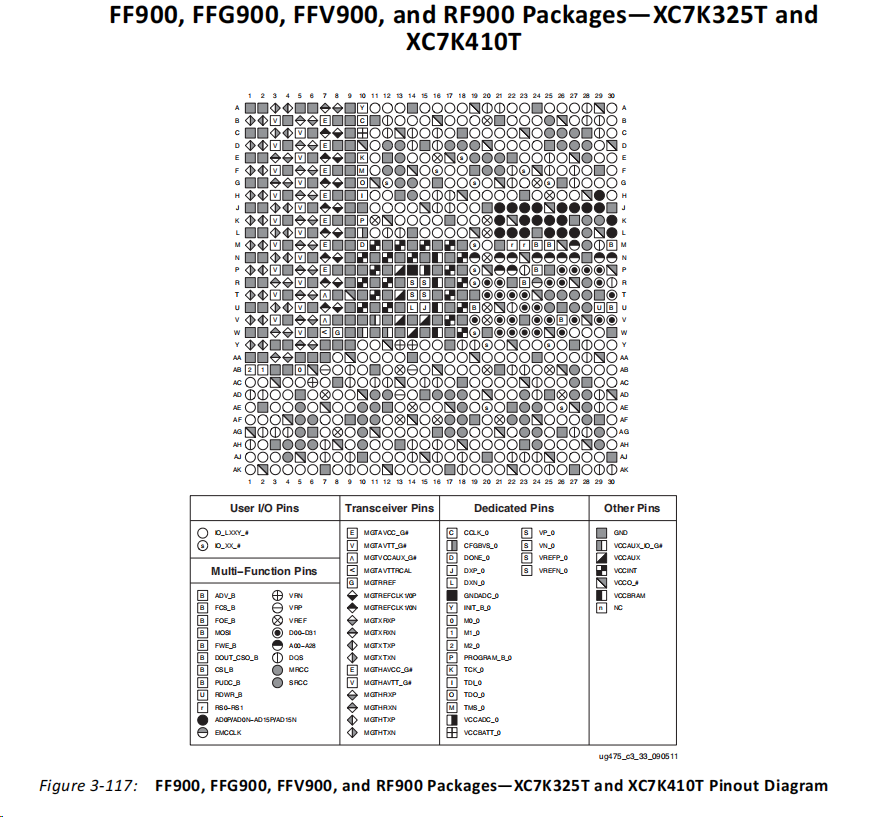

点击对应的page,就能看到该芯片的引脚分配图,bank分配图。图2展示的是引脚分配图。

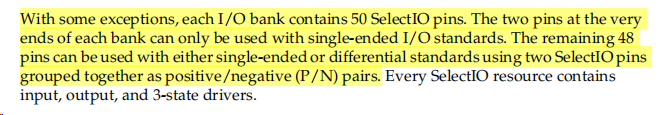

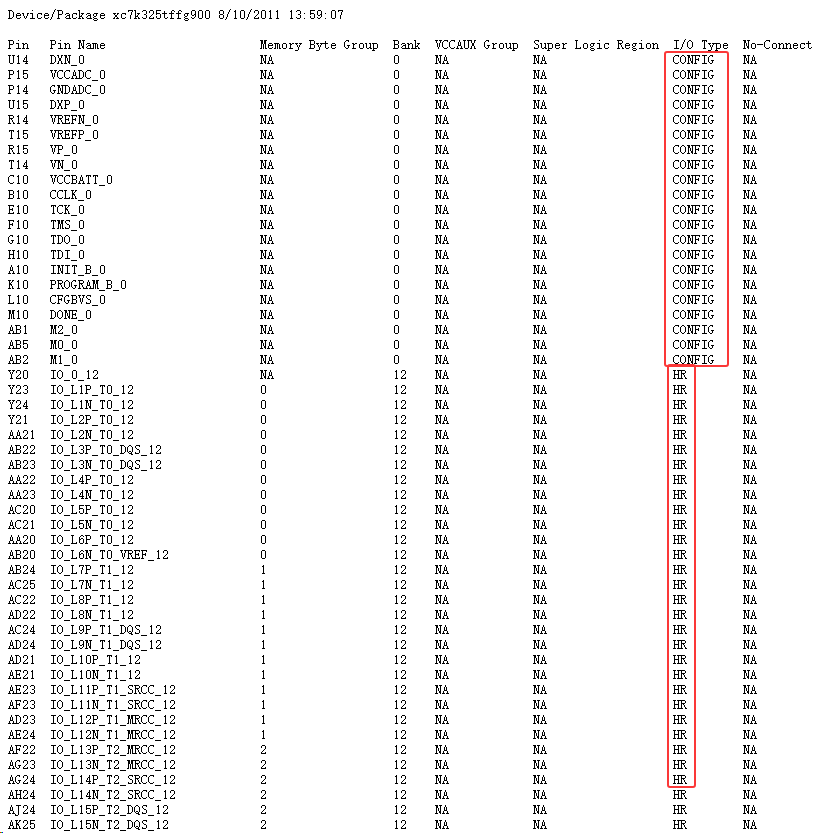

根据图3,芯片的引脚类型大致可分为五种:User I/O Pins、Multi-Function Pins、Transceiver Pins、Dedicated Pins 和 Other Pins。在编写代码时,通常约束的是 User I/O Pins(用户引脚)。下面用户引脚的详细说明(其他引脚的说明后面会写一篇笔记):

| IO_LXXY_#/IO_XX_# | 仅用于普通数字 I/O,不具备其他复用功能。在每个 BANK 的最上面和最下面的引脚为单端引脚,其余48个IV/O 则可配置成 24对差分I/O,也可以当成单端引脚使用,但是差分信号只能用对应的差分I/O,这样才能在代码里面用原语。其中 IO 代表输入/输出,L 代表差分信号,XX 表示数字信号,并标明差分信号对的编号,从上往下排列,从1开始。# 表示该引脚所在的 BANK 编号。 |

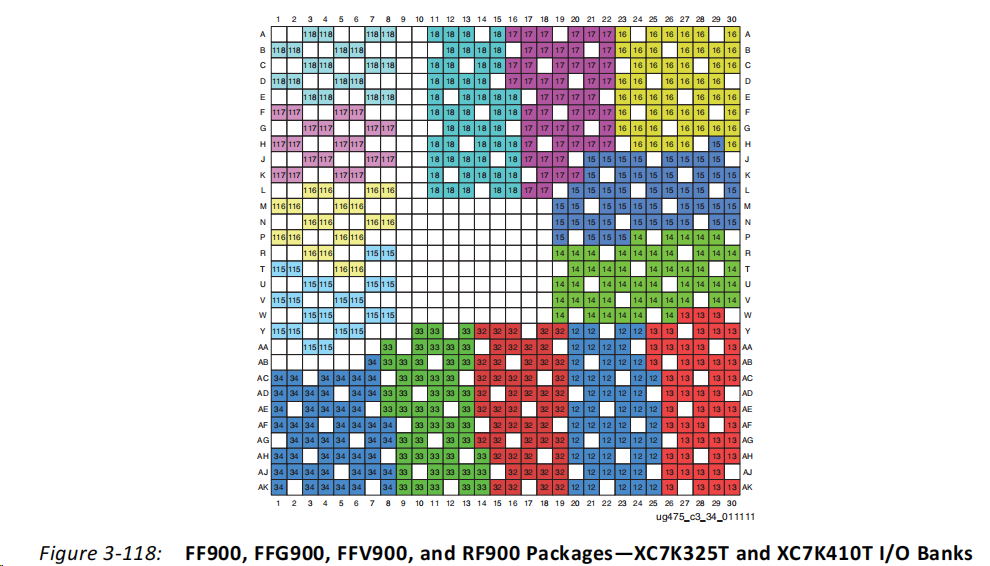

ug471_ Select IO Resources.pdf原文如下:

在器件封装中的形式如下:

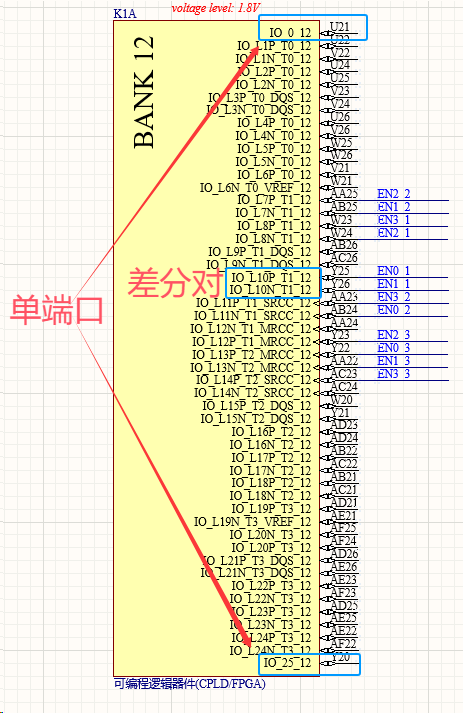

图5展示了IO Bank图。

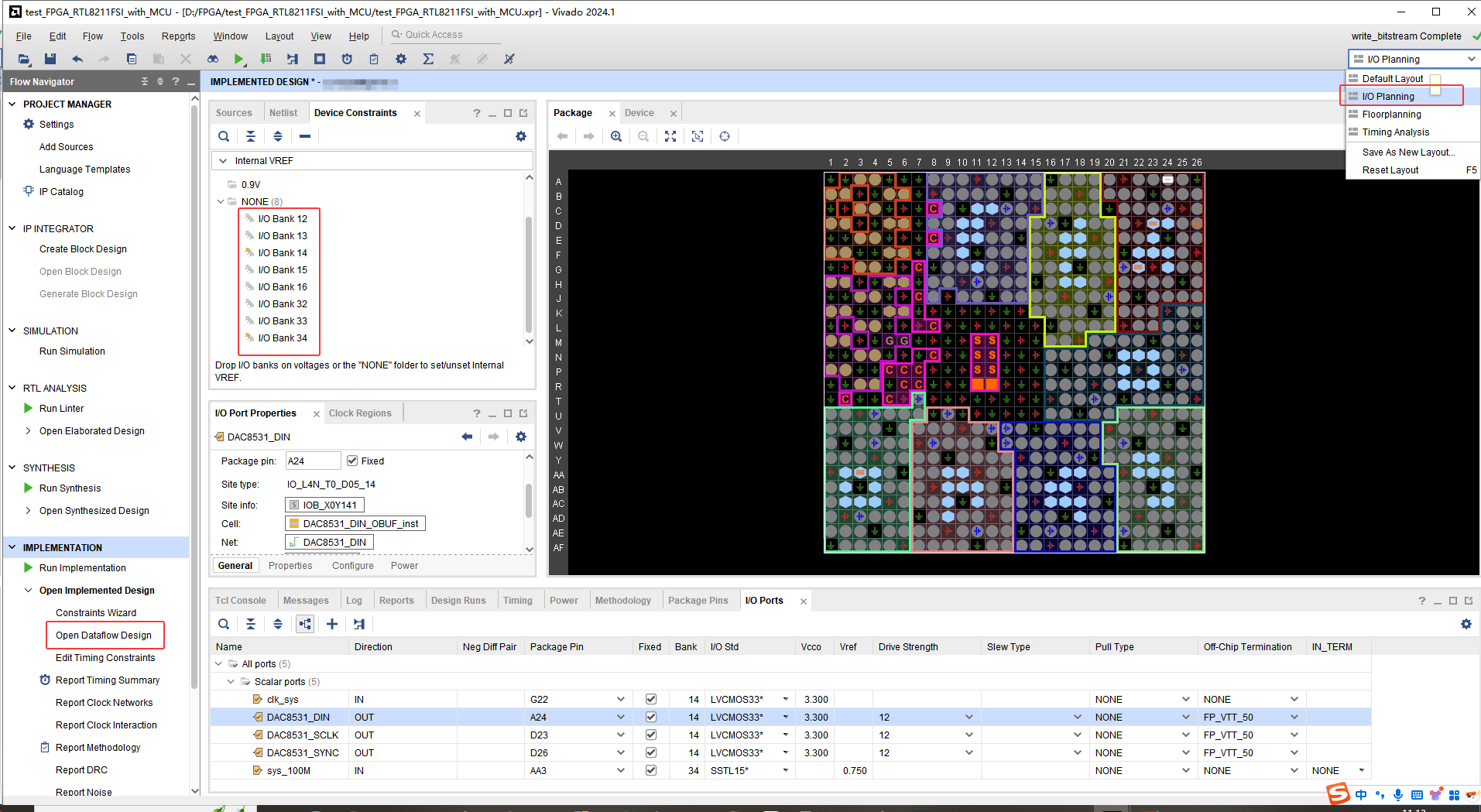

在IO Bank图中,我们可以知道该芯片有几个bank,以及bank引脚的分布。至于我为什么要了解这个,是因为我一开始在想,原理图里面的bank封装是怎么来的,我在设计的时候我怎么知道有多少个bank,然后就去查资料找这些东西。其实除了手册里面的这个bank图可以了解到芯片有哪些bank,还可以通过vivado工具去了解,打开vivado工具,在左上角选择I/O Planning(如果找不到可以先综合,布局布线,在IMPLEMENTED DESIGN选择Open Dataflow Design,然后在打开的界面中再在左上角选择I/O Planning):

在这个界面中也可以了解有哪些bank。但是仅仅有哪些bank,对于画原理图还是不够。后面查资料的时候,发现官网有芯片的引脚信息,可以用来生成原理图和画芯片的封装。链接如下:

以XC7K325T为例,下载.csv之后打开如下:

该文件可查看芯片包含的引脚信息,包括:各引脚所属的Bank、引脚类型(如配置引脚CONFIG、HR/HP/GTX等)。将这些数据导入AD软件后,即可绘制原理图和器件封装,最终完成PCB设计。(后续会写一篇相关的笔记)

1.3 电平标准

常用的电压标准如下:

| 电平标准 (IO Standard) | Bank 电压 (VCCO) | 高电平 (V) | 低电平 (V) | 特点 / 用途 |

|---|---|---|---|---|

| LVCMOS33 | 3.3V | 2.0–3.3 | 0–0.8 | 低功耗 CMOS,FPGA 通用 I/O (最常用的电平标准,基本的非高速接口都是用这种电平) |

| LVCMOS25 | 2.5V | 1.7–2.5 | 0–0.7 | 低电压 CMOS,适合 2.5V 系统 |

| LVCMOS18 | 1.8V | 1.2–1.8 | 0–0.45 | 低电压 CMOS,用于高速接口或低功耗板 |

| LVTTL | 3.3V | ≥2.0 | ≤0.8 | 兼容 TTL 电平,常用于 FPGA I/O |

| HSTL_I / HSTL_II | 1.5V / 1.8V | 0.7 × VDDIO | 0–0.3 × VDDIO | 高速信号,板间接口,高速存储器接口 |

| SSTL18 / SSTL15 | 1.8V / 1.5V | 0.7 × VDDIO | 0–0.3 × VDDIO | 高速存储器接口,如 DDR / DDR2 / DDR3;高速时钟也有可能用这个。 |

| LVDS | 1.2–3.3V 差分 | ±0.35 | ±0.35 | 低电压差分信号,适合高速串行通信 |

| TMDS | 3.3V 差分 | ±0.35 | ±0.35 | 视频接口,如 HDMI、DisplayPort |

| HCSL | 1.0–1.2V | ±0.2 | ±0.2 | 高速差分逻辑,常用于 SerDes 接口 |

| PCI / PCIe 差分 | 1.5V / 3.3V | ±0.2 | ±0.2 | 高速差分总线接口 |

需要说明一下几点:

VCCO / Bank 电压:每个 FPGA Bank 的 I/O 电压通常由 VCCO 引脚提供,决定该 Bank 引脚可使用的电平标准。同一 Bank 内所有 I/O 通常要求使用同一 VCCO,否则可能无法正确工作。差分信号(LVDS / TMDS / HCSL)通常不依赖 VCCO 精确电压,但 Bank 电压仍需满足 FPGA 器件要求。

VREF:对于某些标准(如 SSTL/HSTL),需要一个参考电压 VREF,通常是 VCCO 的一半,用于输入比较器判断逻辑电平。LVCMOS / LVTTL 属于 单端信号,只有一根信号线对地。而LVDS / TMDS / HCSL / SSTL / HSTL 属于 高速差分信号,通过两根线传输信号(正负线)。

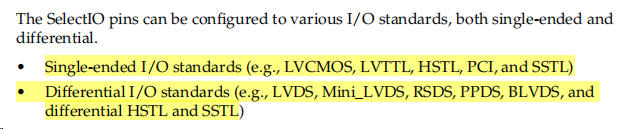

在xilinx 7系列中单端IO口支持以下电平: LVCMOS, LVTTL, HSTL, PCI, and SSTL

差分端口支持以下电平: LVDS, Mini_LVDS, RSDS, PPDS, BLVDS, and differential HSTL and SSTL。ug471_ Select IO Resources.pdf原文如下:

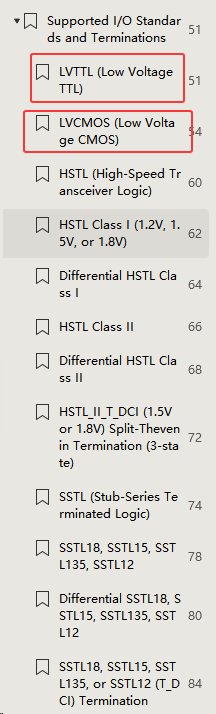

每种电平标准的用法基本都可以在ug471_ Select IO Resources.pdf中找到。目录如下图所示:

以LVDS为例,在Xilinx 7系列FPGA中提供LVDS和LVDS_25两种电平标准。其中:

- LVDS标准仅适用于HP I/O Bank,且对应的Bank电压必须为1.8V

- LVDS_25标准则只能在Bank电压为2.5V的HR I/O Bank中使用

ug471_ Select IO Resources.pdf 原文如下:

选择这个例子是因为AD芯片涉及LVDS差分信号设计,需要特别注意要根据AD芯片的工作电压将AD芯片的差分引脚分配到合适的bank,否则可能出现电平不兼容的问题。

留一个问题:

怎么判断AD芯片差分引脚的电压是1.8V还是2.5V?

2.参考资料:

ug470_Config.pdf:有电源引脚的分类,bank0,bank15,bank15的引脚的说明书,有多重启动的原理

ug471_ Select IO Resources.pdf:有引脚支持的电平标准说明,bank的分类,还有bank的结构图;

ug475_Packaging and Pinout.pdf:有每种芯片的引脚分配,以及有哪几个bank,内存分组;

7-series-product-selection-guide.pdf:有7系列的命名图。

你也想学会搭建FPGA芯片电路图?_fpga电路设计-CSDN博客

以上就是本次学习的记录。欢迎加我为好友(QQ:235840795),一起交流与学习!上面的参考资料也上传到资源中了,可以直接下载。