【STM32外设】DAC

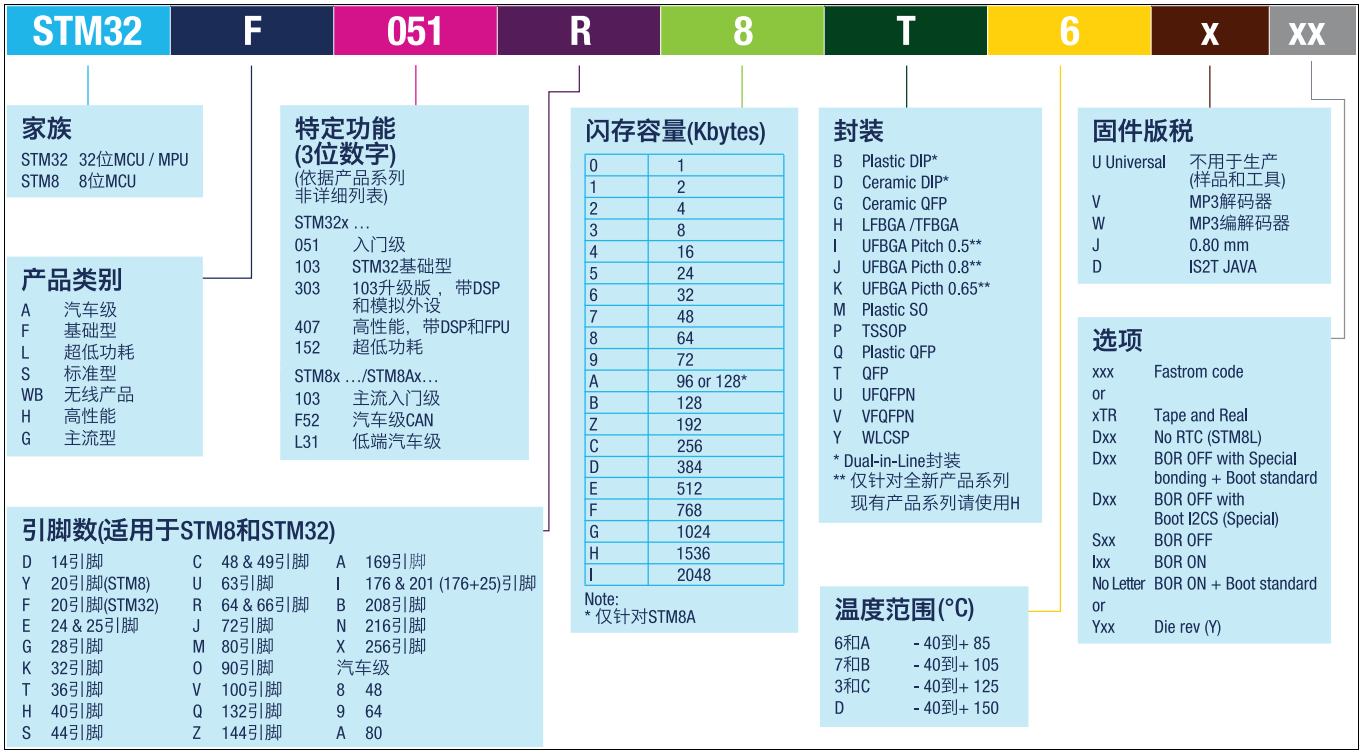

声明:上图是STM32产品型号各字段含义,本文基于STM32F103

1、DAC的一些概念

首先应了解,STM32中ADC的通道是共享的,但DAC的通道不共享,DAC1只能从PA4管脚输出,名曰DAC_OUT1;DAC2只能从PA5管脚输出,名曰DAC_OUT2。

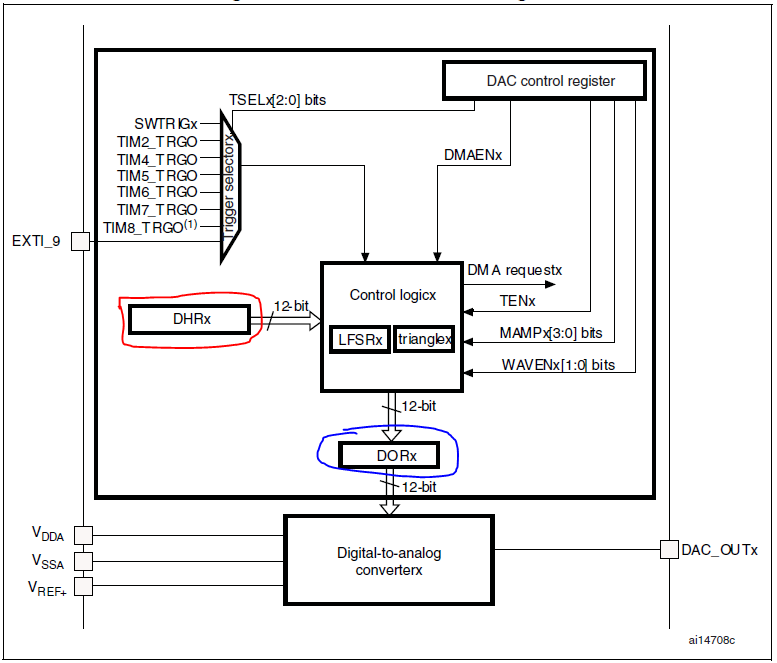

用户向DHRxxx(Data Holding Register)中写值,写入的值由DAC控制逻辑自动写入到DOR(Data Output Register)寄存器,DAC转换器将DOR中的数字量转换为模拟量输出。注意用户不能直接写DOR寄存器。如下图所示,

2、DAC寄存器

DAC总共13个32位寄存器,但实际能用到的就3个:DAC->CR、DAC->SWTRIGR、DAC->DHR12R2。

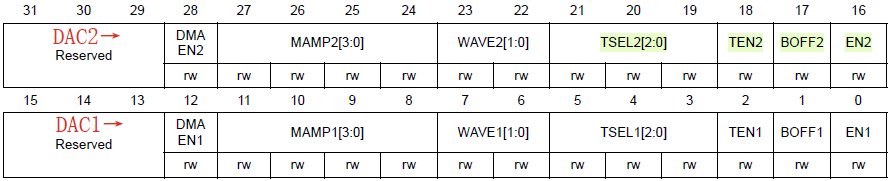

DAC->CR:Control register of DAC,开发DAC必用寄存器。

Address offset: 0x00 Reset value: 0x0000 0000

- Bits21:19 TSEL2[2:0]: DAC channel2 trigger selection,DAC触发方式选择,由软件设置。

000: Timer 6 TRGO event

001: Timer 3 TRGO event in connectivity line devices, Timer 8 TRGO in high-density and XL-density devices

010: Timer 7 TRGO event

011: Timer 5 TRGO event

100: Timer 2 TRGO event

101: Timer 4 TRGO event

110: External line9

111: Software trigger- Bit18 TEN2: DAC channel2 trigger enable,由软件设置。

0:自动转换,写进DAC_DHRxxx的数据在1个APB1时钟后传到DAC_DOR2。

1:触发转换使能,软件触发需1个APB1时钟周期,其他触发方式需3个APB1时钟周期。- Bit 17 BOFF2: Buffer OFF,DAC channel2 output buffer disable。由软件设置。

0: DAC channel2 output buffer enabled

1: DAC channel2 output buffer disabled- Bit16 EN2: DAC channel2 enable,由软件设置。

0: DAC channel2 disabled

1: DAC channel2 enabled

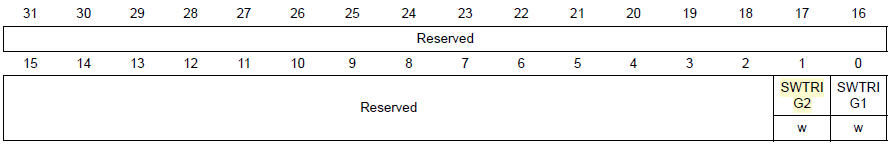

DAC->SWTRIGR:Software trigger register of DAC,开发DAC必用寄存器。

Address offset: 0x04 Reset value: 0x0000 0000

- Bit1 SWTRIG2: Software Trigger,DAC channel2 软件触发位,由软件置位,一旦DAC_DHR2中的值加载到DAC_DOR2中,硬件自动清零该位。

0: Software Not trigger

1: Software trigger

DAC->DHR12R1:DAC channel1 12-bit right-aligned data holding register,通道1右对齐12bit寄存器。

Address offset: 0x08 Reset value: 0x0000 0000

DAC->DHR12L1:DAC channel1 12-bit left aligned data holding register,通道1左对齐12bit寄存器。

Address offset: 0x0C Reset value: 0x0000 0000

DAC->DHR8R1:DAC channel1 8-bit right aligned data holding register,通道1右对齐8bit寄存器。

Address offset: 0x10 Reset value: 0x0000 0000

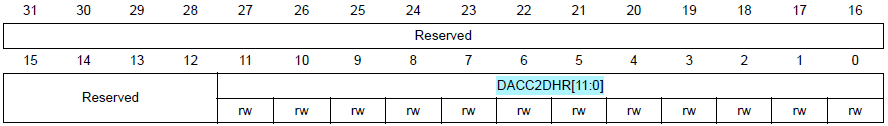

DAC->DHR12R2:Data holding register with 12-bit right-aligned of DAC channel2,通道2右对齐12bit寄存器。

Address offset: 0x14 Reset value: 0x0000 0000

DAC->DHR12L2:DAC channel2 12-bit left aligned data holding register,通道2左对齐12bit寄存器。

Address offset: 0x18 Reset value: 0x0000 0000

DAC->DHR8R2:DAC channel2 8-bit right aligned data holding register,通道2右对齐8bit寄存器。

Address offset: 0x1C Reset value: 0x0000 0000

DAC->DHR12RD:Dual DAC 12-bit right-aligned data holding register,双DAC右对齐12bit寄存器。

Address offset: 0x20 Reset value: 0x0000 0000

DAC->DHR12LD:Dual DAC 12-bit left-aligned data holding register,双DAC左对齐12bit寄存器。

Address offset: 0x24 Reset value: 0x0000 0000

DAC->DHR8RD:DUAL DAC 8-bit right aligned data holding register,双DAC右对齐8bit寄存器。

Address offset: 0x28 Reset value: 0x0000 0000

DAC->DOR1:Data output register of DAC channel1,只读,因此一般用不到。

Address offset: 0x2C Reset value: 0x0000 0000

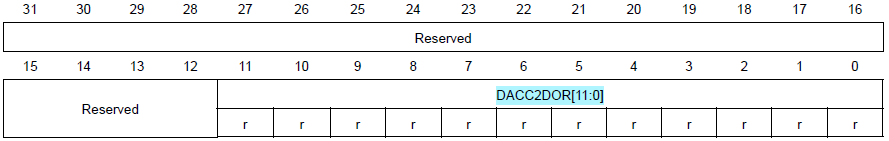

DAC->DOR2:Data output register of DAC channel2,只读,因此一般用不到。

Address offset: 0x30 Reset value: 0x0000 0000

3、DAC软件触发配置

- 设置DAC2->CR寄存器的TSEL2[2:0]为111,以选择触发方式为软件触发;

设置DAC2->CR寄存器的TEN2为1,以使能触发;

设置DAC2->CR寄存器的BOFF2为1,以使能输出缓冲区,提高输出能力;(不开启时4096输出达不到3.3V,开启了就能达到3.3V,但零漂会变大,都是折中,很难两全)

设置DAC2->CR寄存器的EN2为1,使能DAC2; - 设置DAC->DHR12R2寄存器的DACC2DHR[11:0],写入0 ~ 4095的数值,对应PA5脚输出0V ~ VDDA;(VDDA一般接稳定的3.3V)

- 设置DAC->SWTRIGR寄存器的SWTRIG2为1,触发DAC2转换,该位由硬件自动清零;

- 重复步骤2、步骤3。