LVDS系列27:Xilinx 7系 OSERDESE2原语(三)

该讲进行仿真验证;

SDR 8:1 数据路径仿真:

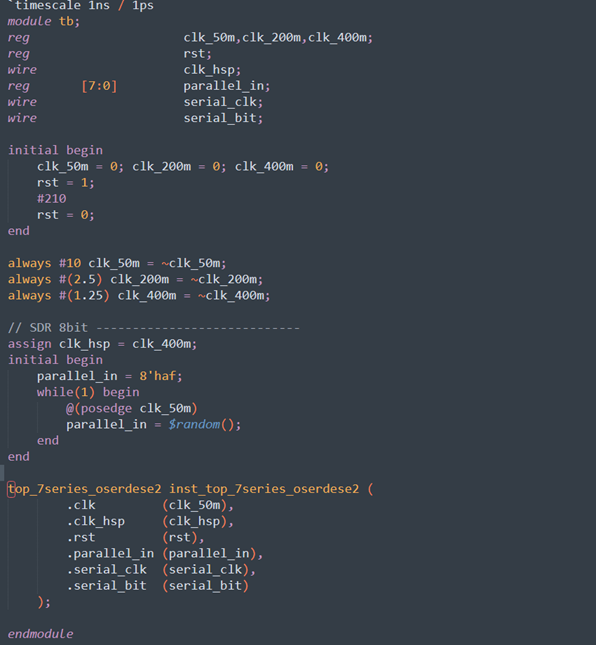

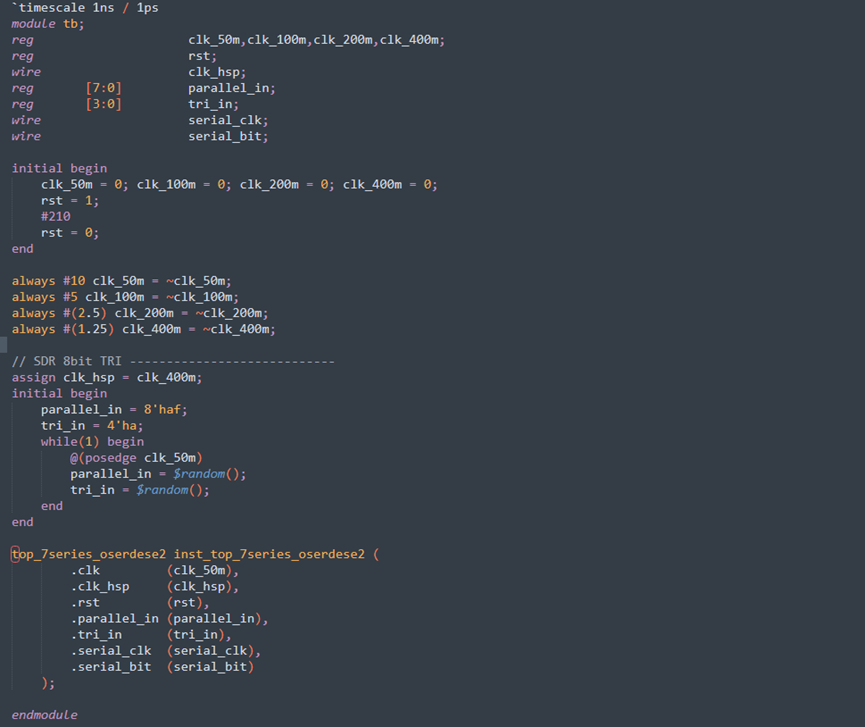

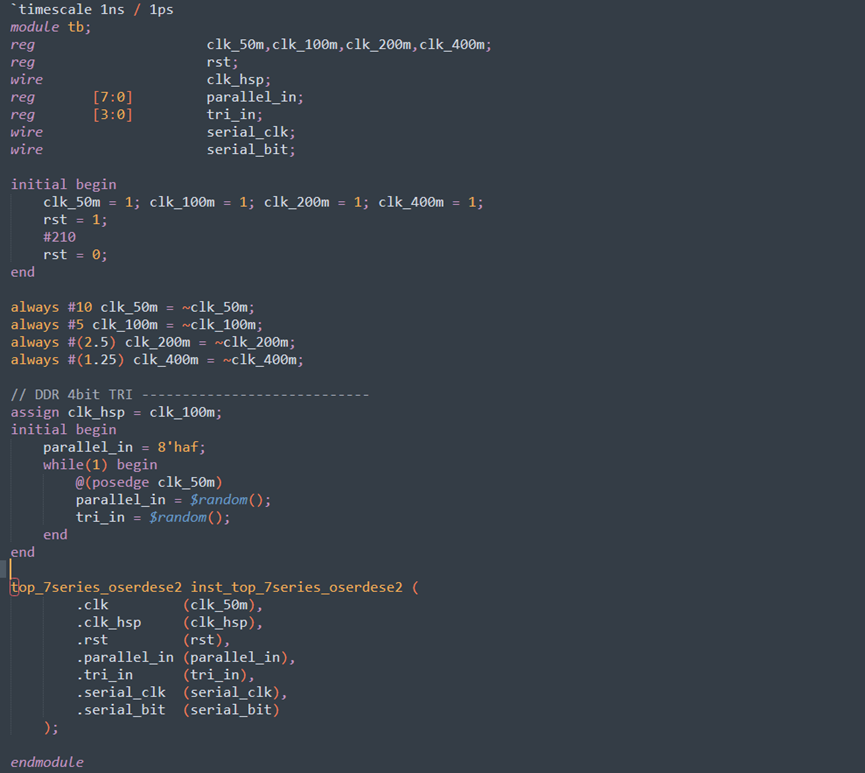

testbench:

产生随机数,分频时钟50MHz,高速时钟200MHz,产生随机8bit输入输入仿真;

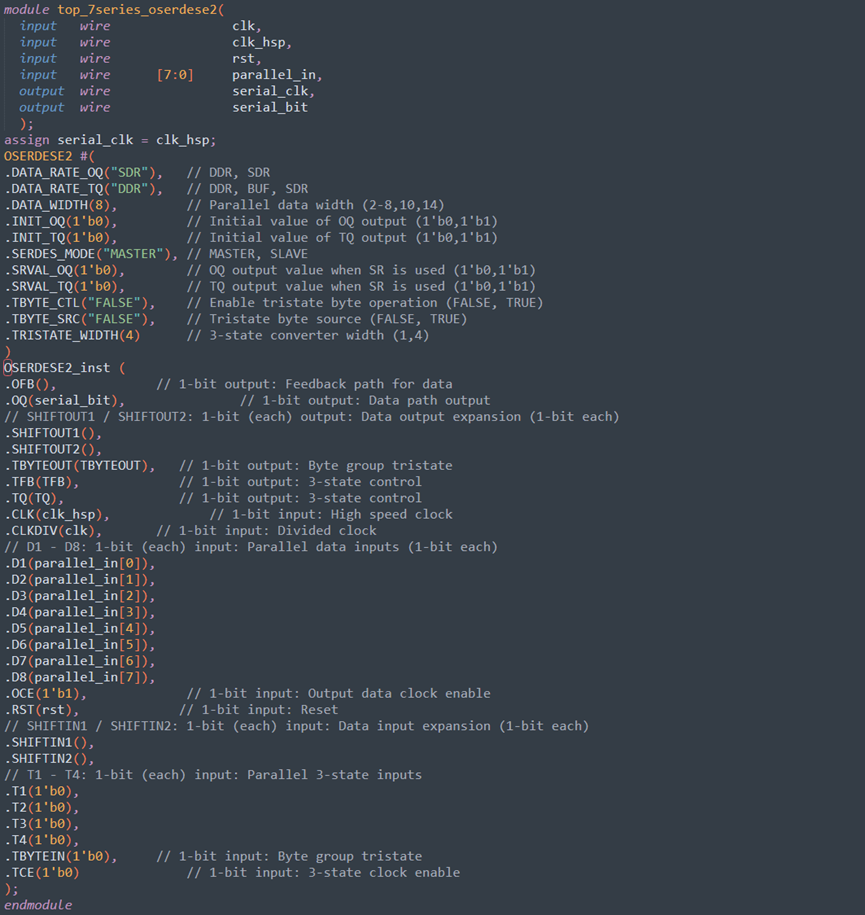

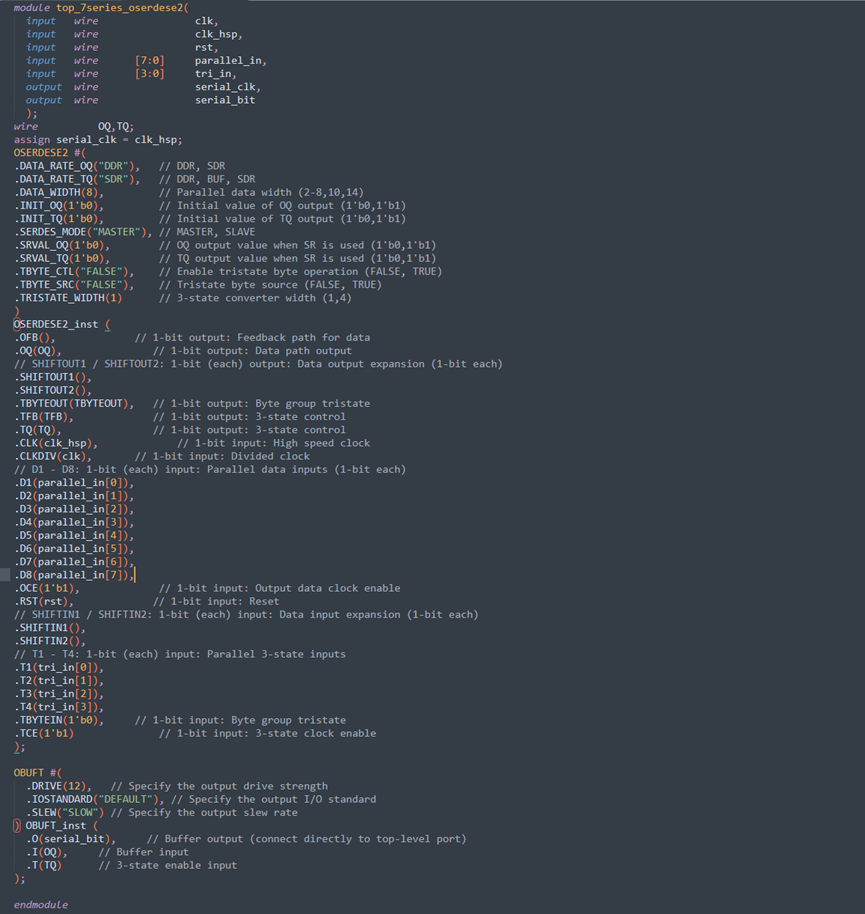

被测模块:

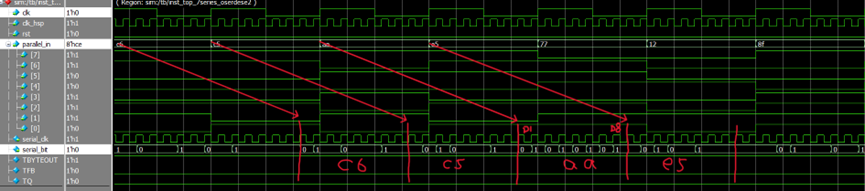

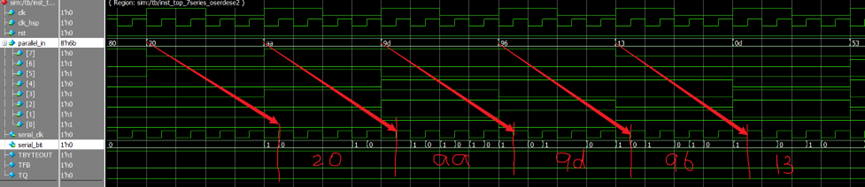

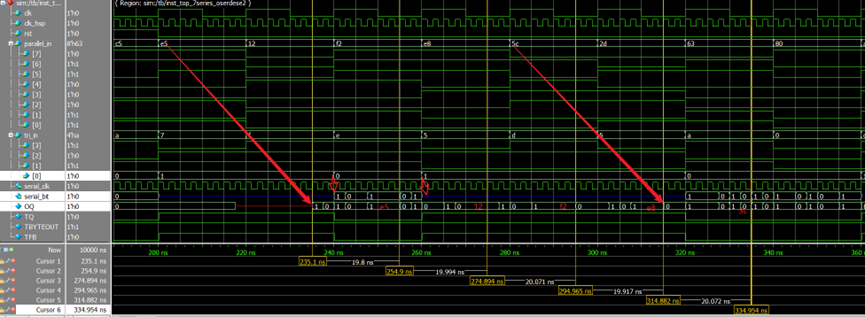

仿真结果:

50M的分频时钟,400M的高速时钟,SDR 8:1模式,可以看到,并行数据输入后,经过一两个分频时钟周期后串行输出;

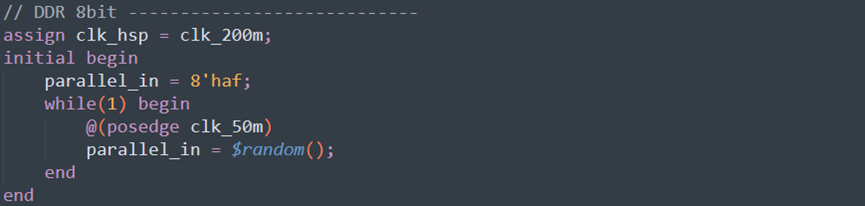

DDR 8:1 数据路径仿真:

Testbench修改数据产生逻辑:

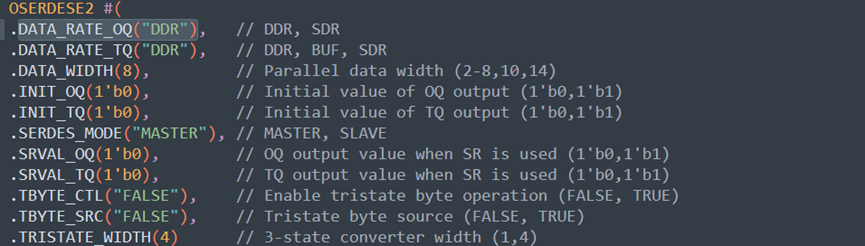

被测模块修改DDR模式:

仿真结果:

DDR 8:1模式,8bit并行输出正常串行输出;

三态路径仿真:

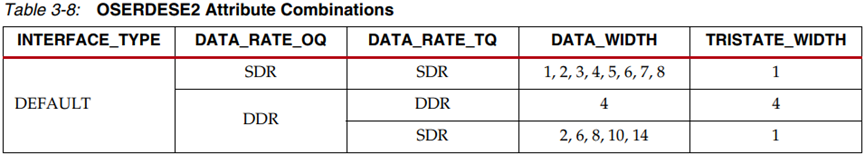

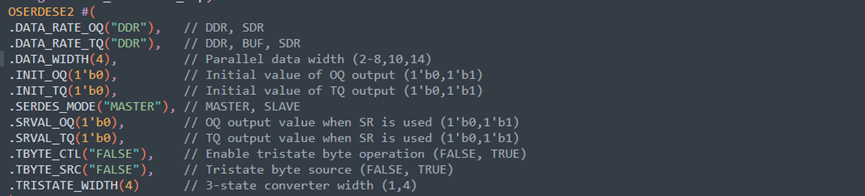

使用下表中的参数搭配,仿真验证SDR 8:1和DDR 4:1的三态控制实现:

SDR 8:1三态控制仿真:

按照上方表格,

数据路径SDR 8:1,三态控制的DATA_RATE_TQ需设置为SDR,TRISTATE_WIDTH需设置为1;

Testbench:

被测模块:

添加OBUFT用于三态控制的实现,

修改数据路径SDR 8:1,三态控制为SDR 位宽1,

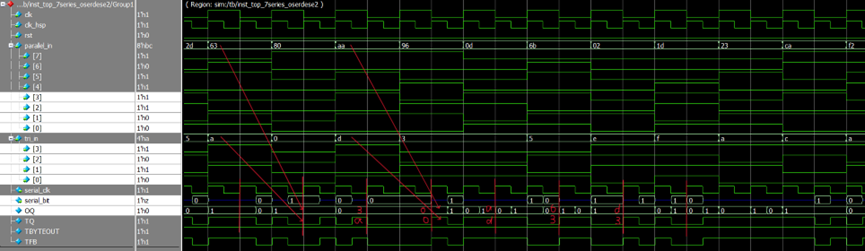

仿真结果:

数据路径使用SDR 8:1,三态控制按照上面表格,只能设置为位宽1,

此时可以看到仿真结果里,SDR数据路径转换是正常进行,但是三态控制路径,从tri[0]这个三态控制位使能到其作用到输出线上的时间非常短,其没有与数据路径同步,所以这里仿真中,与我们想要的结果相比,OQ和TQ出现了2bit的错位,该配置方式暂时不要使用;

DDR 4:1三态控制仿真:

数据路径DDR 4:1, DATA_RATE_TQ需设置为DDR,TRISTATE_WIDTH需设置为4;

Testbench修改为:

被测模块修改:

修改数据路径DDR 4:1,三态控制也为DDR4:1,

仿真结果:

从仿真结果可以看到,数据路径DDR 4:1,并行输入的4bit数据和4bit三态控制位,当输出为串行数据时,且高速时钟和分频时钟相位对齐,数据路径的OQ和三态控制的TQ能够位同步输出,没有像上面SDR 8:1一样出现错位的情况;

与上面的SDR 8:1模式相比,DDR4:1模式的三态控制就能实现我们想要的时序功能;

本文章由威三学社出品

对课程感兴趣可以私信联系