【PZ-AU15P】璞致fpga开发板 Aritx UltraScalePlus PZ-AU15P 核心板与开发板用户手册

第一章: Artix UltraScale+系列介绍

Artix™ UltraScale+™ 器件是成本优化的 FPGA,基于经过生产验证的先进 16nm 架构,具有卓越的性能功耗比。设备通过封装创新得到增强, 实现超紧凑的外形尺寸 和计算密度。

Artix UltraScale+ FPGA 具有适用于高级协议的高达 16Gb/s 的收发器以及与 竞争性 FPGA 产品相比最高的 FPGA DSP 性能,可将 I/O 带宽与计算相匹配,帮助 最大限度地提高机器视觉、网络等成本敏感型和低功耗应用的系统性能、4K 广播以 及一系列工业物联网和边缘市场。

Artix UltraScale+器件价值与优势如下:

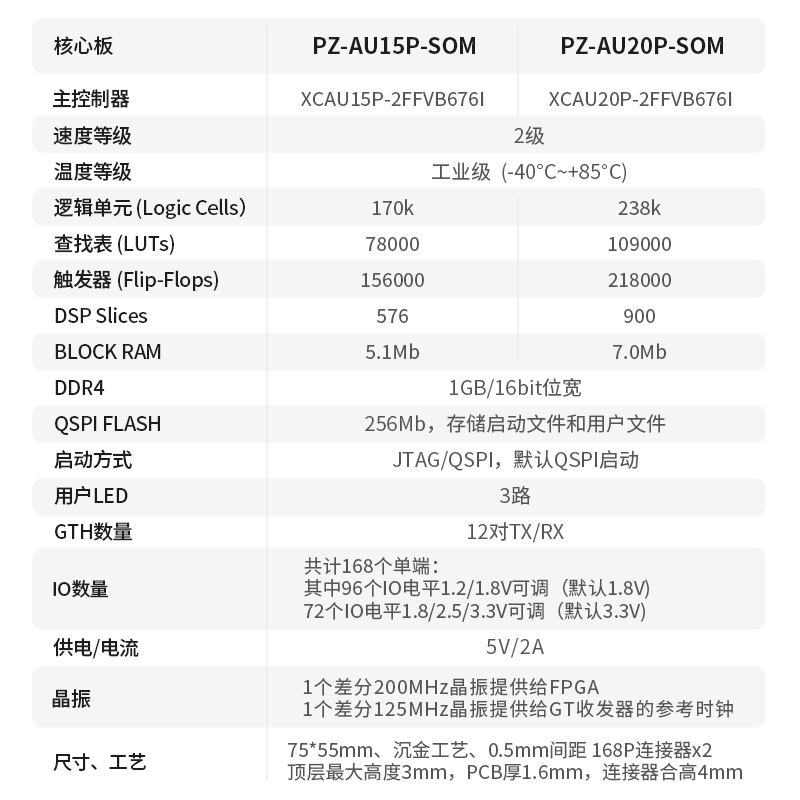

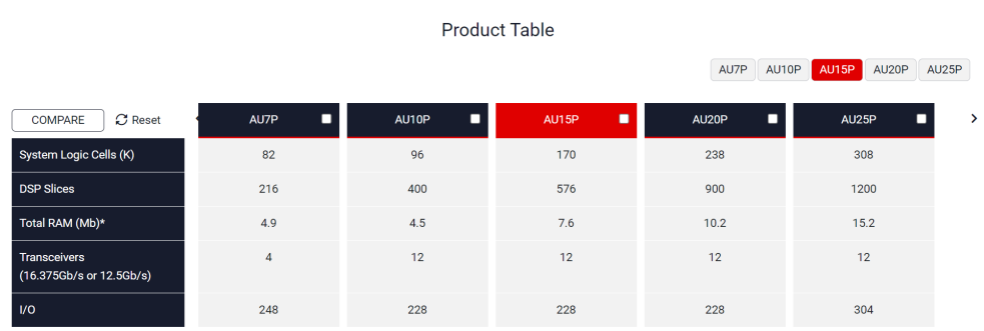

Artix UltraScale+器件资源如下表列出,我们选用 AU15P 做为核心板的主控芯 片:

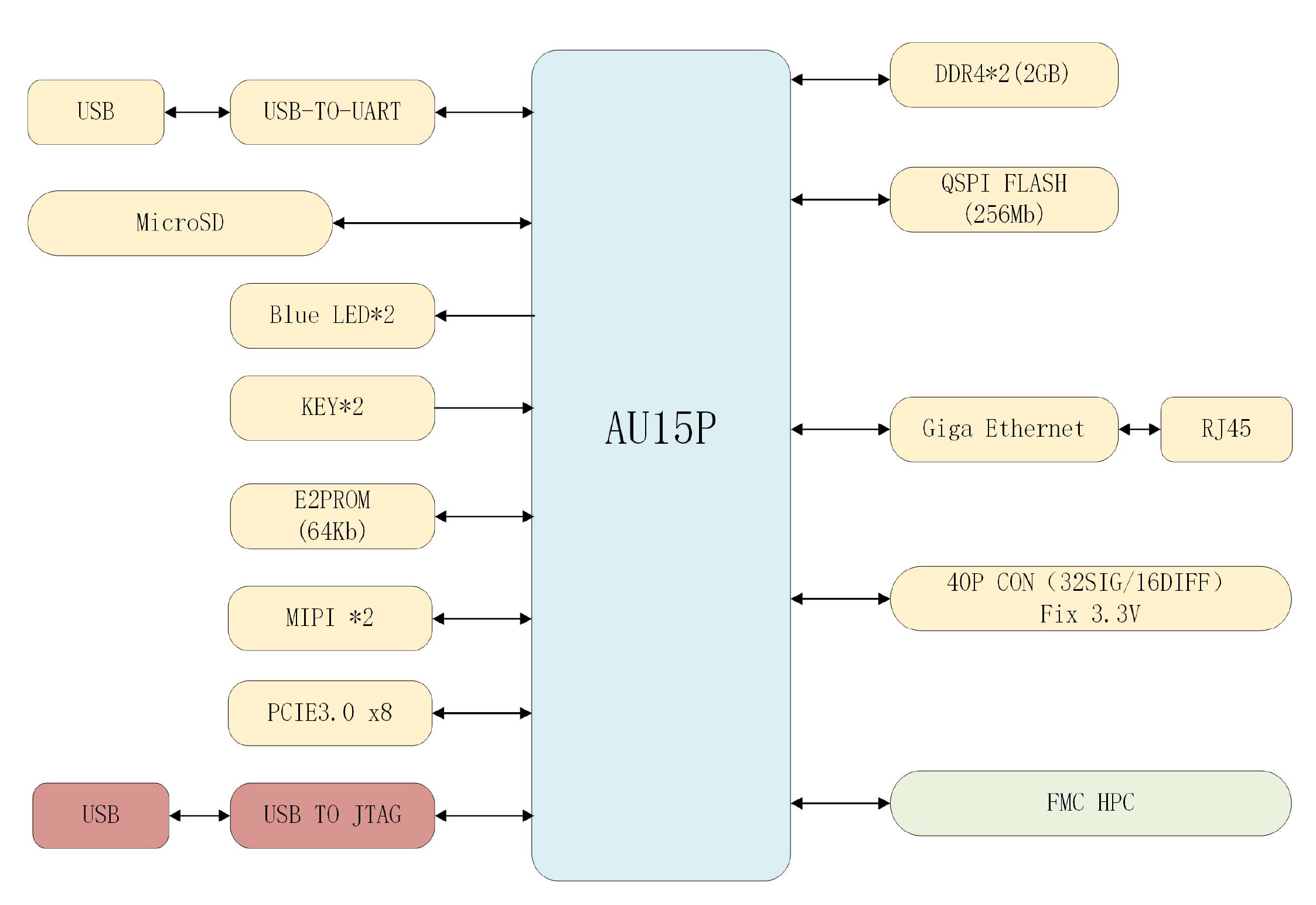

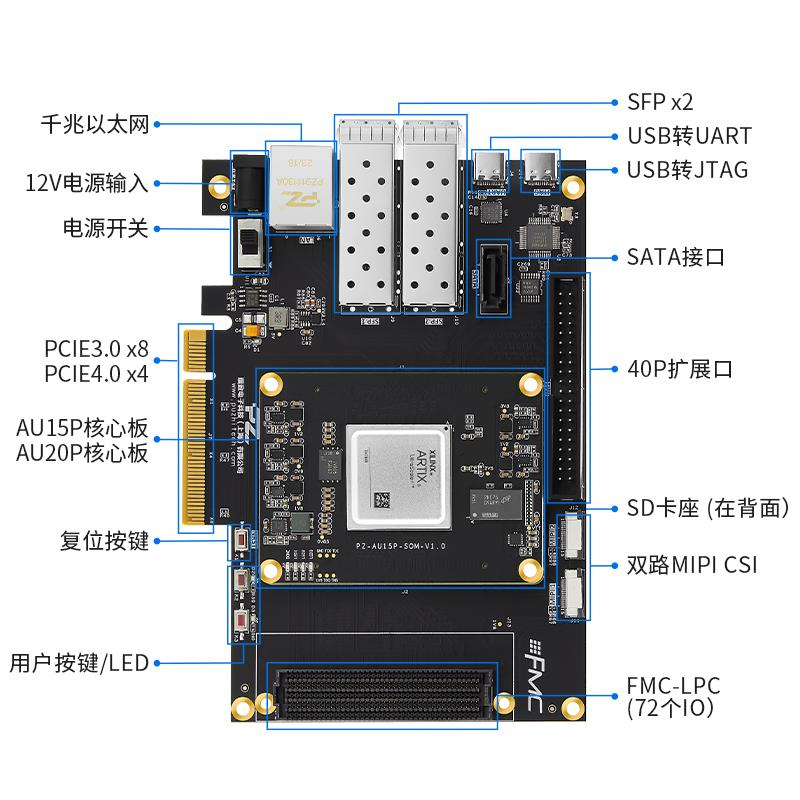

第二章: 璞致 Artix UltraScale+开发板概述

璞致电子科技 Artix UltraScale+系列开发板提供了AU15P 版本,使用 XILINX 公司的 XCAU15P-2FFVB676I 作为主控制器,考虑到同系列还有 AU20P/AU25P,璞致 板卡也做了兼容,但当前并没有生产,如用户需要,可以联系我们生产。

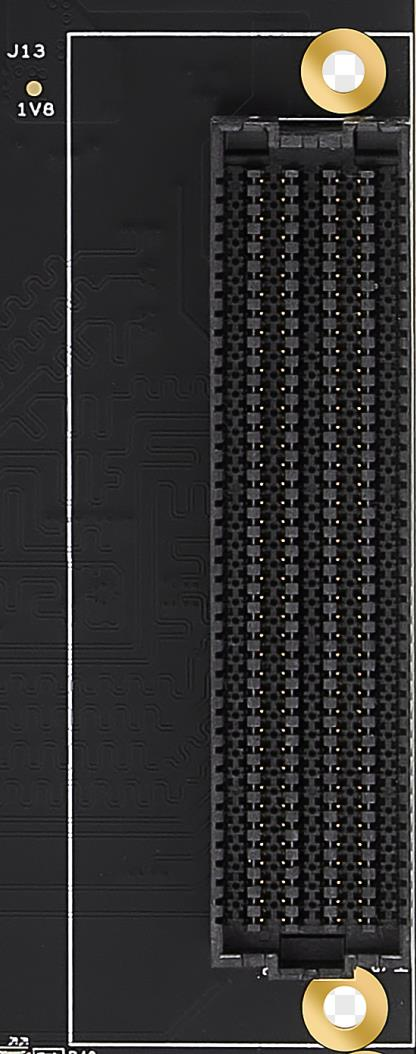

璞致电子科技 Artix UltraScale+系列开发板以核心板加底板方式提供。核 心板通过两个0.5mm 间距 168P 高速连接器扣接在底板上,使用上更加灵活。既可 以做学习使用,也可以使用核心板用于项目开发。

另外,开发板集成了丰富的外设资源,提供了详尽的开发例程,加速了用 户学习或者项目推进。除此之外,开发板还集成了 JTAG 调试器,做到了一根 USB 线和一根 12V 电源线就可以让开发板工作起来,使用更加便捷。

关于核心板和开发板的详细说明,可以查阅下文对应的核心板和底板章 节。

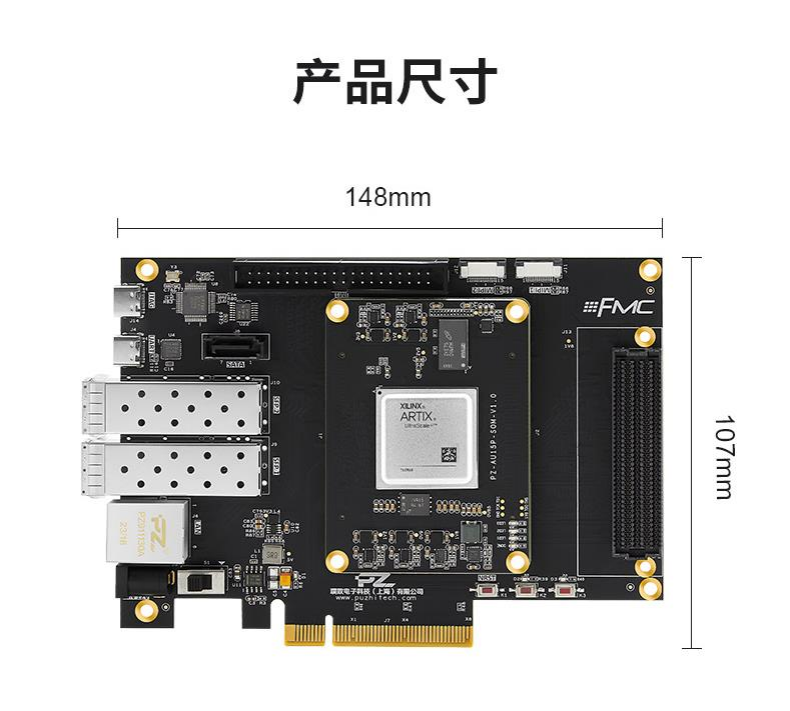

如下图标出开发板尺寸为 148x107mm,开发板的四个角各放置一个固定孔, 用于安装支撑柱或固定单板,孔径为 3.5mm。开发板配置了风扇、散热片以及亚 克力防护板,为方便展示,并没有安装到开发板上,下图列出了散热片和风扇以 及对应尺寸。

第三章: 璞致 Artix UltraScale+核心板

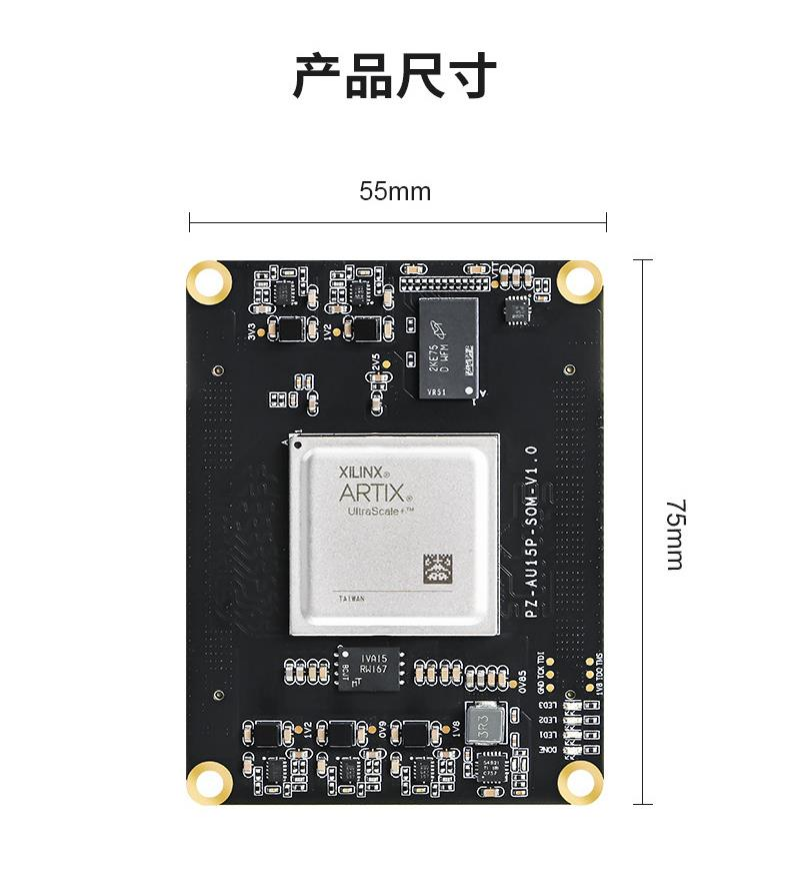

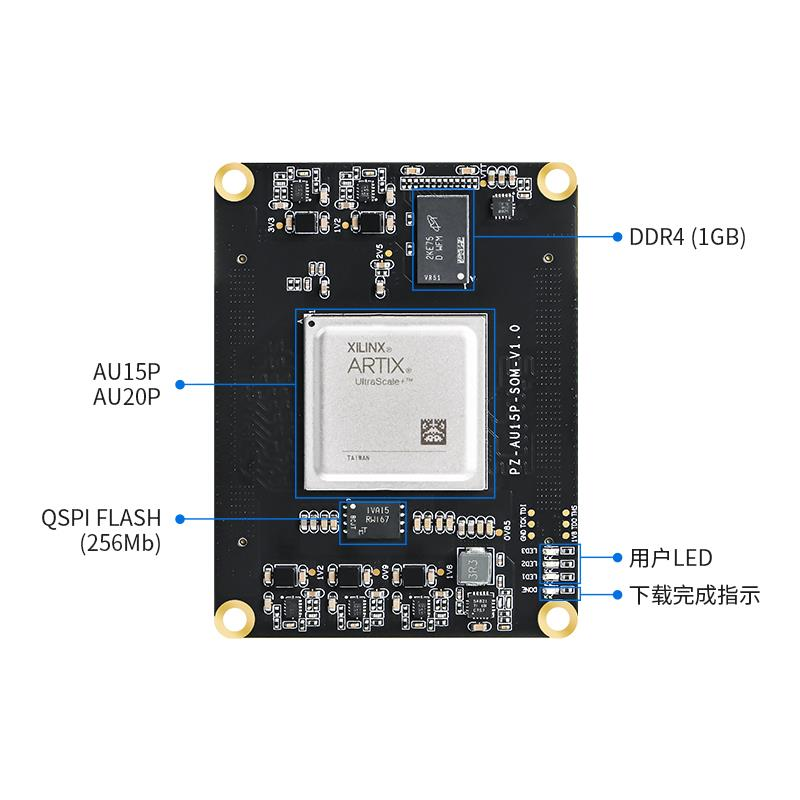

璞致 Artix UltraScale+系列核心板提供了AU15P 型号的板卡,同时兼容 AU20P/AU25P,接口做了兼容设计,如用户需求可以与我们联系。如下图详细标 注了核心板的功能模块。

核心板供电电压是 5V,在核心板的两个角都留有电源输入管脚,电源管脚 在模块内部已做了连通,此设计主要考虑用户电源接入方向,哪个方向方便接 哪个,只需要接一个角就可以。电源连接需用铜皮连接且打足够的过孔以保证 电源通流能力。核心板上的所有 GND 信号都需要连接到底板上,每个 GND 通过 两个过孔与底板连接。因核心板逻辑使用量不同,核心板供电极限电流在

5V/3A,所以外部供电需要考虑极限电流情况以保证核心板工作稳定。

给模组供电的电源输出电压需要稳定,且需要考虑电源浪涌,核心板电源 输入口需要加几颗大电容(220UF/10V),可以加一级 DC2DC 芯片,确保供电稳 定。

核心板提供了两路差分时钟,频率分别是 200M/125M,满足了各种应用需 求。另外,125M 时钟还加了时钟缓冲器,可以实现板载时钟和外部时钟输入切 换,当时钟选择信号不接地时钟来源为差分晶振,当时钟选择信号接地时时钟 来源为连接器外部输入,如下图详细列出了时钟连接的对应关系和管脚所在位 置,更详细说明可参考璞致提供的核心板原理图。

考虑到最大限度的保留 IO 口引出到底板上,核心板上并没有加复位按键,在开 发板上我们预留有复位按键,因为主控芯片是纯 FPGA,所以任何一个 IO 接口都可以 当做逻辑的复位接口,用户也可以自行定义复位接口。

主芯片的启动模式分别是 JTAG、QSPI Flash,默认配置为 QSPI Flash 启动,但 JTAG 模式优先级要高于 QSPI Flash,所以当用户连接了 JTAG 接口芯片优先从 JTAG 启动,不用做启动模式切换。核心板上 QSPI Flash 容量为 256Mb,更详细说明可参考 璞致提供的核心板原理图。

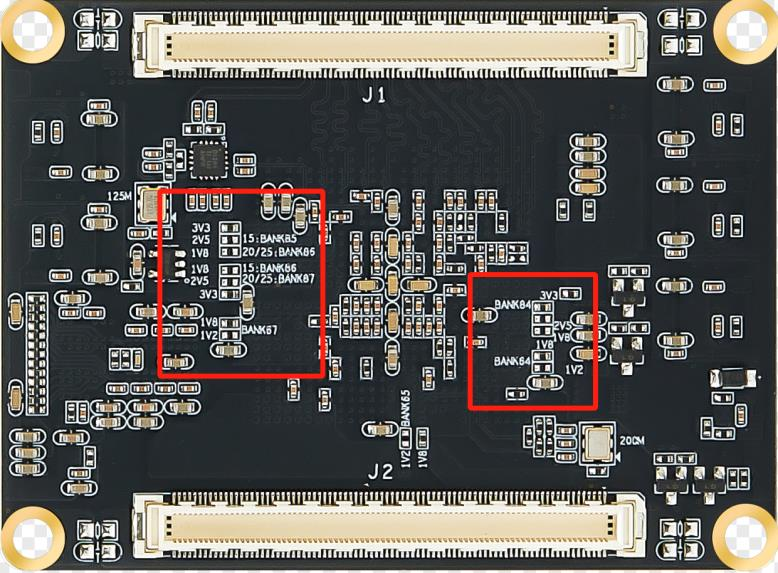

核心板上 BANK64/65/67 为 HP BANK,接口电平可以做 1.2/1.8V 调节,默认电平 为 1.8V。BANK84/85/86 为 HD BANK,接口电平可以做 1.8/2.5/3.3V 调节,默认电平 为 3.3V。核心板 BANK 电平的选择可以通过电阻位置选焊来调节,对应的电阻标注位 置如下图所示,精确位置参考核心板实物。另外,AU25 芯片比 AU15/AU20 多了 BANK67, 为 HP BANK,我们也做了预留设计,但AU15/20 芯片上并没有 BANK67。使用时需要特 别注意。

主芯片配置了一颗 DDR4,单颗容量 1GB,DDR4 管脚分配参见下表,更详细信息可 参考璞致提供的原理图或者例程。

DDR4 引脚 | 管脚名称 | 管脚位置 |

DDR4_DQ0 | IO_L23P_T3U_N8_66 | D26 |

DDR4_DQ1 | IO_L20P_T3L_N2_AD1P_66 | F23 |

DDR4_DQ2 | IO_L24P_T3U_N10_66 | B25 |

DDR4_DQ3 | IO_L21N_T3L_N5_AD8N_66 | D25 |

DDR4_DQ4 | IO_L23N_T3U_N9_66 | C26 |

DDR4_DQ5 | IO_L20N_T3L_N3_AD1N_66 | E23 |

DDR4_DQ6 | IO_L24N_T3U_N11_66 | B26 |

DDR4_DQ7 | IO_L21P_T3L_N4_AD8P_66 | D24 |

DDR4_DM0 | IO_L19P_T3L_N0_DBC_AD9P_66 | E25 |

DDR4_DQS_P0 | IO_L22P_T3U_N6_DBC_AD0P_66 | D23 |

DDR4_DQS_N0 | IO_L22N_T3U_N7_DBC_AD0N_66 | C24 |

DDR4_DQ8 | IO_L5P_T0U_N8_AD14P_66 | K21 |

DDR4_DQ9 | IO_L3P_T0L_N4_AD15P_66 | J19 |

DDR4_DQ10 | IO_L2N_T0L_N3_66 | M21 |

DDR4_DQ11 | IO_L3N_T0L_N5_AD15N_66 | J20 |

DDR4_DQ12 | IO_L2P_T0L_N2_66 | M20 |

DDR4_DQ13 | IO_L6N_T0U_N11_AD6N_66 | K20 |

DDR4_DQ14 | IO_L5N_T0U_N9_AD14N_66 | J21 |

DDR4_DQ15 | IO_L6P_T0U_N10_AD6P_66 | L20 |

DDR4_DM1 | IO_L1P_T0L_N0_DBC_66 | L18 |

DDR4_DQS_P1 | IO_L4P_T0U_N6_DBC_AD7P_66 | M19 |

DDR4_DQS_N1 | IO_L4N_T0U_N7_DBC_AD7N_66 | L19 |

DDR4_A0 | IO_L17P_T2U_N8_AD10P_66 | H26 |

DDR4_A1 | IO_L18N_T2U_N11_AD2N_66 | H22 |

DDR4_A2 | IO_L9N_T1L_N5_AD12N_66 | K26 |

DDR4_A3 | IO_L12P_T1U_N10_GC_66 | J23 |

DDR4_A4 | IO_L17N_T2U_N9_AD10N_66 | G26 |

DDR4_A5 | IO_L18P_T2U_N10_AD2P_66 | H21 |

DDR4_A6 | IO_L10N_T1U_N7_QBC_AD4N_66 | L25 |

DDR4_A7 | IO_L19N_T3L_N1_DBC_AD9N_66 | E26 |

DDR4_A8 | IO_L8P_T1L_N2_AD5P_66 | M25 |

DDR4_A9 | IO_L16P_T2U_N6_QBC_AD3P_66 | F24 |

DDR4_A10 | IO_L15P_T2L_N4_AD11P_66 | J25 |

DDR4_A11 | IO_L8N_T1L_N3_AD5N_66 | M26 |

DDR4_A12 | IO_L12N_T1U_N11_GC_66 | J24 |

DDR4_A13 | IO_L16N_T2U_N7_QBC_AD3N_66 | F25 |

DDR4_A14 | IO_L13N_T2L_N1_GC_QBC_66 | G25 |

DDR4_A15 | IO_L14N_T2L_N3_GC_66 | H24 |

DDR4_A16 | IO_T3U_N12_66 | F22 |

DDR4_BA0 | IO_L10P_T1U_N6_QBC_AD4P_66 | L24 |

DDR4_BA1 | IO_T2U_N12_66 | G22 |

DDR4_BG0 | IO_L15N_T2L_N5_AD11N_66 | J26 |

DDR4_nCS | IO_L13P_T2L_N0_GC_QBC_66 | G24 |

DDR4_ODT | IO_L7P_T1L_N0_QBC_AD13P_66 | L22 |

DDR4_nRESET | IO_T1U_N12_66 | M24 |

DDR4_CLK_P | IO_L11P_T1U_N8_GC_66 | K22 |

DDR4_CLK_N | IO_L11N_T1U_N9_GC_66 | K23 |

DDR4_CKE | IO_L14P_T2L_N2_GC_66 | H23 |

DDR4_nACT | IO_L7N_T1L_N1_QBC_AD13N_66 | L23 |

DDR4_PARITY | IO_L9P_T1L_N4_AD12P_66 | K25 |

核心板引出到连接器的信号都做了严格等长,可以参考璞致提供的信号等长表格, 里面详细列出了信号名称和信号走线长度,表格已存放在对应的文件夹下 。。

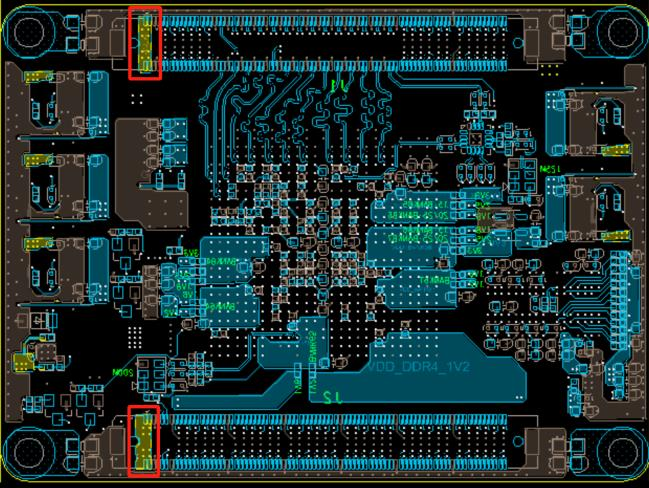

为方便用户快速使用核心板,我们提供了对应的封装库,连接器相对位置和核心 板外框丝印都已摆放好,直接调用即可。原理图封装提供 AD/ORCAD 两个版本,PCB 封 装提供 AD/Allegro 两个版本,均已存放在对应的文件夹下。另外,文件夹下提供了核 心板的 DXF 文件,方便用户对应结构。

核心板采用了两个高密连接器与底板连接,底板上使用的连接器对应型号是 FX10A-168S-SV,用户可以自行购买,也可以联系璞致客服购买。

第四章 璞致 Artix UltraScale+底板

前面章节我们详细介绍了核心板资源,本章节我们将详细介绍开发板对应底板所 搭载的资源。

开发板有两种供电方式,璞致提供的 12V/3A 的适配器供电或者通过 PCIE 供电, 两种供电方式可以通过 S1 开关来切换。电源接入后通过 DCDC 转换成 3.3V、1.8V 等 多路电压供板内器件使用。电源部分详细电路可参考开发板对应的原理图。

时钟电路主要集中在核心板上,可以参考核心板时钟部分说明。

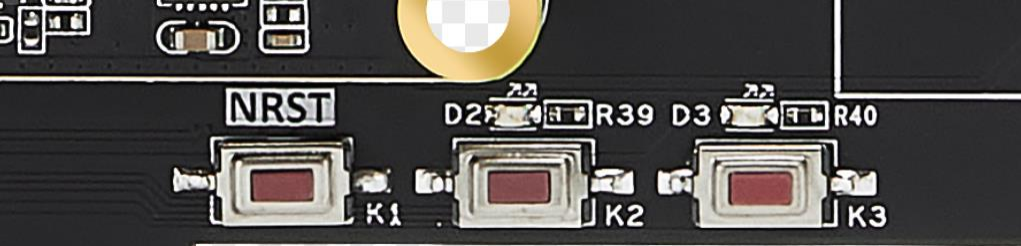

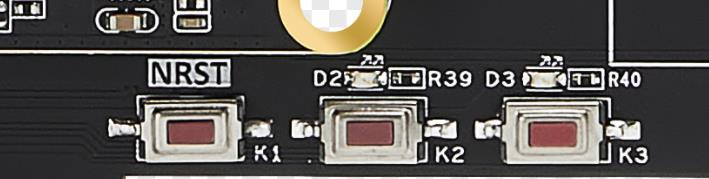

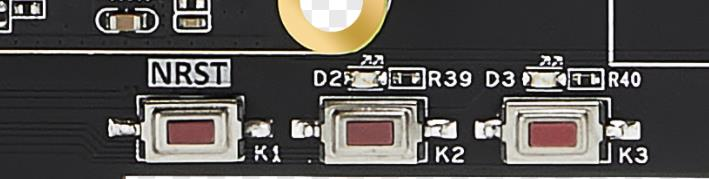

在开发板上预留了一个复位按键,按键默认高电平,按下后为低电平。

复位管脚连接到 BANK84 的 IO_3N_84(AE15)管脚,管脚电平为 3.3V。复位部分详 细电路可参考开发板原理图。

开发板使用 Silicon Labs CP2102GM 芯片实现 USB 转 UART, USB 接口采用 TypeC 接口,用户只要用一根 USB 线连接到 PC 上即可进行串口通信。

UART 的 TX/RX 信号与 FPGA 的 BANK85 相连,接口电平为 3.3V。 如下是信号对应 关系表和原理图。

UART 引脚 | 管脚名称 | 管脚位置 |

UART_TX | IO_2P_85 | J11 |

UART_RX | IO_2N_85 | J10 |

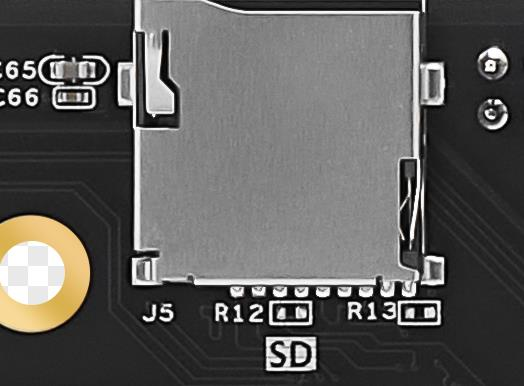

开发板上放置了一个 SD 卡座(开发板背面), SD 卡信号连接到 FPGA 的 BANK85 上,接口电平为 3.3V。如下是信号对应关系,详细电路可以参考开发板原理图。

SD 卡引脚 | 管脚名称 | 管脚位置 |

SD-CLK | IO_1N_85 | K9 |

SD-CMD | IO_1P_85 | K10 |

SD-DATA0 | IO_9P_85 | D9 |

SD-DATA1 | IO_9N_85 | C9 |

SD-DATA2 | IO_10P_85 | B9 |

SD-DATA3 | IO_10N_85 | A9 |

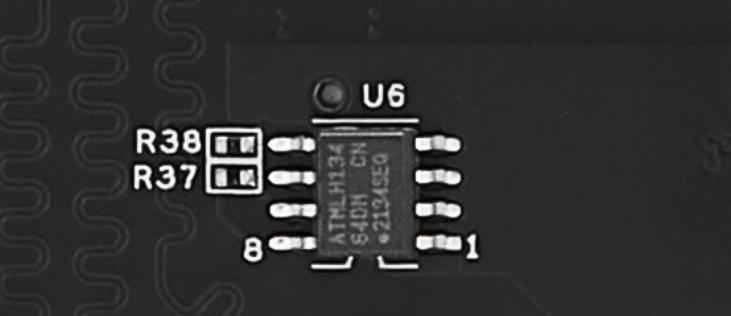

开发板上放置了一颗 64Kbit 的 EEPROM 芯片,型号为 AT24C64D-SSHM-T,E2PROM 通过 IIC 扩展芯片与 FPGA 的 BANK84 相连,接口电平为 3.3V。EEPROM 读地址是 0xA1, 写地址是 0xA0。操作代码可参考璞致提供的例程,详细电路可以参考开发板原理图。

E2PROM | 管脚名称 | 管脚位置 |

E2PROM_I2C_SCL | IO_6P_84 | AB15 |

E2PROM_I2C_SDA | IO_6N_84 | AB16 |

开发板上设计了一路千兆以太网,以太网芯片与 FPGA 之间通过 RGMII 接 口互联,连接 BANK65/84,接口电平是 1.8V,连接对应管脚见下表,网口地 址是 PHY_AD[2:0]=001,详细电路可以参考开发板原理图。

RMGII 信号 | 管脚名称 | 管脚位置 |

GTX_CLK | IO_18P_65 | R25 |

TX_EN | IO_18N_65 | R26 |

TXD0 | IO_17P_65 | P25 |

TXD1 | IO_17N_65 | P26 |

TXD2 | IO_15P_65 | N24 |

TXD3 | IO_15N_65 | P24 |

RX_CLK | IO_14P_GC_65 | T25 |

RX_DV | IO_14N_GC_65 | U25 |

RXD0 | IO_1P_65 | U19 |

RXD1 | IO_1N_65 | V19 |

RXD2 | IO_12P_65 | V24 |

RXD3 | IO_12N_65 | W24 |

MDC | IO_10P_84 | W14 |

MDIO | IO_10N_84 | W15 |

开发板上设计了两路 10G SFP 接口,接口信号与 FPGA 的 BANK226 相连,详细可 参考原理图。

如下是 SFP 的引脚分配, 详细电路可以参考开发板原理图。

SFP1 引脚 | 管脚名称 | 管脚位置 |

SFP-TX-P1 | MGT_TX_P0_226 | N5 |

SFP-TX-N1 | MGT_TX_N0_226 | N4 |

QSFP1-RX-P1 | MGT_RX_P0_226 | M2 |

QSFP1-RX-N1 | MGT_RX_N0_226 | M1 |

SFP2 引脚 | 管脚名称 | 管脚位置 |

SFP-TX-P1 | MGT_TX_P1_226 | L5 |

SFP-TX-N1 | MGT_TX_N1_226 | L4 |

QSFP1-RX-P1 | MGT_RX_P1_226 | K2 |

QSFP1-RX-N1 | MGT_RX_N1_226 | K1 |

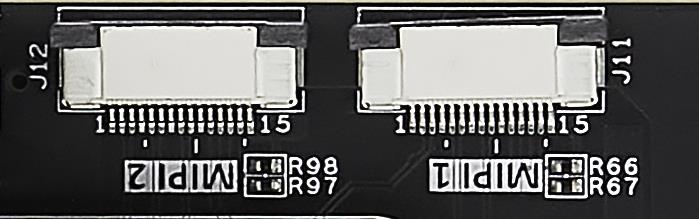

开发板设计了两路 MIPI 接口,管脚定义如下表,详细电路可以参考开发板原理 图。

MIPI1 信号 | 管脚名称 | 管脚位置 |

MIPI1_D_P0 | IO_20P_65 | P20 |

MIPI1_D_N0 | IO_20N_65 | P21 |

MIPI1_D_P1 | IO_21P_65 | R20 |

MIPI1_D_N1 | IO_21N_65 | R21 |

MIPI1_CLK_P | IO_19P_65 | R22 |

MIPI1_CLK_N | IO_19N_65 | R23 |

MIPI1_RST | IO_7N_85 | E10 |

MIPI1_CLK | IO_7P_85 | E11 |

MIPI1_IIC_SCL | IO_4P_85 | H11 |

MIPI1_IIC_SDA | IO_4N_85 | G11 |

MIPI2 信号 | 管脚名称 | 管脚位置 |

MIPI2_D_P0 | IO_6P_65 | W19 |

MIPI2_D_N0 | IO_6N_65 | W20 |

MIPI2_D_P1 | IO_4P_65 | V21 |

MIPI2_D_N1 | IO_4N_65 | V22 |

MIPI2_CLK_P | IO_10P_65 | W25 |

MIPI2_CLK_N | IO_10N_65 | W26 |

MIPI2_RST | IO_L7N_85 | D10 |

MIPI2_CLK | IO_L7P_85 | D11 |

MIPI2_IIC_SCL | IO_L3P_85 | J9 |

MIPI2_IIC_SDA | IO_L3N_85 | H9 |

开发板设计了两路 LED。LED 高电平亮,低电平灭。详细电路可参考开发板原理 图。

LED 位号 | 管脚名称 | 管脚位置 |

LED1 | IO-1P-84 | AF14 |

LED2 | IO-1N-84 | AF15 |

开发板设计了两路用户按键,一路复位按键。按键默认高电平,按下为低电平, 按键连到 PL 侧,管脚位置如下表。

按键位号 | 管脚名称 | 管脚位置 |

KEY1 | IO-2P-84 | AE13 |

KEY2 | IO-2N-84 | AF13 |

SYS_nRST | IO-3N-84 | AE15 |

开发板设计了一个 40P 2.54mm 间距的简易牛角座,用于扩展信号的连接,信号 与 FPGA 的 BANK85/86 连接,电平为 3.3V。如下表标出了信号所在的芯片位置,详细 连接关系参考原理图部分。

JM1 信号顺序 | 管脚名称 | 管脚位置 | JM1 信号顺序 | 管脚名称 | 管脚位置 |

5 | IO_L7P_HDGC_86 | E13 | 6 | IO_L6P_HDGC_86 | F10 |

7 | IO_L7N_HDGC _86 | E12 | 8 | IO_L6N_HDGC_86 | F9 |

9 | IO_L8P_HDGC _86 | D14 | 10 | IO_L5P_HDGC_86 | G10 |

11 | IO_L8N_HDGC _86 | D13 | 12 | IO_L5N_HDGC_86 | G9 |

13 | IO_L9P_86 | C14 | 14 | IO_L3P_86 | H14 |

15 | IO_L9N_86 | C13 | 16 | IO_L3N_86 | G14 |

17 | IO_L10P_86 | C12 | 18 | IO_L1P_86 | J12 |

19 | IO_L10N_86 | B12 | 20 | IO_L1N_86 | H12 |

21 | IO_L11P_86 | A13 | 22 | IO_L2P_86 | J13 |

23 | IO_L11N_86 | A12 | 24 | IO_L2N_86 | H13 |

25 | IO_L12P_86 | B14 | 26 | IO_L4P_86 | J15 |

27 | IO_L12N_86 | A14 | 28 | IO_L4N_86 | J14 |

29 | IO_L5P_85 | G10 | 30 | IO_L6P_85 | F10 |

31 | IO_L5N_85 | G9 | 32 | IO_L6N_85 | F9 |

37 | IO_L11P_85 | B10 | 38 | IO_L12P_85 | C11 |

39 | IO_L11N_85 | A10 | 40 | IO_L12N_85 | B11 |

开发板上设计了一路 FMC-PPC 连接器,但因芯片管脚数量有限,实际并没有全部 连接,只连接了 4 对 MGT 和 LA 信号,如下表列出了信号对应关系。详细连接关系参 考原理图部分。

序号 | FMC-LPC 管脚 | 管脚名称 | 管脚位置 |

C2 | DP0_C2M_P | MGT_TX_P3_226 | G5 |

C3 | DP0_C2M_N | MGT_TX_N3_226 | G4 |

C6 | DP0_M2C_P | MGT_RX_P3_226 | F2 |

C7 | DP0_M2C_N | MGT_RX_N3_226 | F1 |

C10 | LA06_P | IO_L3P_64 | AF24 |

C11 | LA06_N | IO_L3N_64 | AF25 |

C14 | LA10_P | IO_L5P_64 | AD24 |

C15 | LA10_N | IO_L5N_64 | AD25 |

C18 | LA14_P | IO_L9P_64 | AC22 |

C19 | LA14_N | IO_L9N_64 | AC23 |

C22 | LA18_P_CC | IO_L12P_MRCC_64 | AB21 |

19 / 23

C23 | LA18_N_CC | IO_L12N_MRCC_64 | AC21 |

C26 | LA27_P | IO_L7P_65 | Y22 |

C27 | LA27_N | IO_L7N_65 | Y23 |

C30 | SCL | IO_L8P_HDGC_84 | AA14 |

C31 | SDA | IO_L8N_HDGC_84 | AB14 |

D4 | GBTCLK0_M2C_P | MGT_CLK0_P_226 | P7 |

D5 | GBTCLK0_M2C_N | MGT_CLK0_N_226 | P6 |

D8 | LA01_P_CC | IO_L14P_SRCC_64 | AC19 |

D9 | LA01_N_CC | IO_L14N_SRCC_64 | AD19 |

D11 | LA05_P | IO_L1P_64 | AE25 |

D12 | LA05_N | IO_L1N_64 | AE26 |

D14 | LA09_P | IO_L4P_64 | AC26 |

D15 | LA09_N | IO_L4N_64 | AD26 |

D17 | LA13_P | IO_L6P_64 | AB24 |

D18 | LA13_N | IO_L6N_64 | AC24 |

D20 | LA17_P_CC | IO_L11P_SRCC_64 | AD21 |

D21 | LA17_N_CC | IO_L11N_SRCC_64 | AE21 |

D23 | LA23_P | IO_L19P_64 | Y20 |

D24 | LA23_N | IO_L19N_64 | Y21 |

D26 | LA26_P | IO_L10P_65 | N23 |

D27 | LA26_N | IO_L10N_65 | P23 |

G2 | CLK1_M2C_P | IO_L7P_HDGC_84 | Y15 |

G3 | CLK1_M2C_N | IO_L7N_HDGC_84 | AA15 |

G6 | LA00_P_CC | IO_L13P_MRCC_64 | AD20 |

G7 | LA00_N_CC | IO_L13N_MRCC_64 | AE20 |

G9 | LA03_P | IO_L17P_64 | AE17 |

G10 | LA03_N | IO_L17N_64 | AF17 |

G12 | LA08_P | IO_L16P_64 | AC18 |

G13 | LA08_N | IO_L16N_64 | AD18 |

G15 | LA12_P | IO_L8P_64 | AD23 |

G16 | LA12_N | IO_L8N_64 | AE23 |

G18 | LA16_P | IO_L22P_64 | AB17 |

G19 | LA16_N | IO_L22N_64 | AC17 |

G21 | LA20_P | IO_L10P_64 | AA22 |

G22 | LA20_N | IO_L10N_64 | AB22 |

G24 | LA22_P | IO_L24P_64 | Y18 |

G25 | LA22_N | IO_L24N_64 | AA18 |

G27 | LA25_P | IO_L6P_65 | N19 |

G28 | LA25_N | IO_L6N_65 | P19 |

G30 | LA29_P | IO_L2P_65 | U21 |

G31 | LA29_N | IO_L2N_65 | U22 |

G33 | LA31_P | IO_L3P_65 | T20 |

G34 | LA31_N | IO_L3N_65 | U20 |

G36 | LA33_P | IO_L5P_65 | T22 |

G37 | LA33_N | IO_L5N_65 | T23 |

H4 | CLK0_M2C_P | IO_L11P_SRCC_65 | V23 |

H5 | CLK0_M2C_N | IO_L11N_SRCC_65 | W23 |

H7 | LA02_P | IO_L18P_64 | AD16 |

20 / 23

H8 | LA02_N | IO_L18N_64 | AE16 |

H10 | LA04_P | IO_L15P_64 | AF18 |

H11 | LA04_N | IO_L15N_64 | AF19 |

H13 | LA07_P | IO_L7P_64 | AE22 |

H14 | LA07_N | IO_L7N_64 | AF22 |

H16 | LA11_P | IO_L2P_64 | AB25 |

H17 | LA11_N | IO_L2N_64 | AB26 |

H19 | LA15_P | IO_L20P_64 | AA19 |

H20 | LA15_N | IO_L20N_64 | AB19 |

H22 | LA19_P | IO_L21P_64 | AA20 |

H23 | LA19_N | IO_L21N_64 | AB20 |

H25 | LA21_P | IO_L23P_64 | Y17 |

H26 | LA21_N | IO_L23N_64 | AA17 |

H28 | LA24_P | IO_L4P_65 | N21 |

H29 | LA24_N | IO_L4N_65 | N22 |

H31 | LA28_P | IO_L9P_65 | AA24 |

H32 | LA28_N | IO_L9N_65 | AA25 |

H34 | LA30_P | IO_L8P_65 | Y25 |

H35 | LA30_N | IO_L8N_65 | Y26 |

H37 | LA32_P | IO_L16P_65 | U26 |

H38 | LA32_N | IO_L16N_65 | V26 |

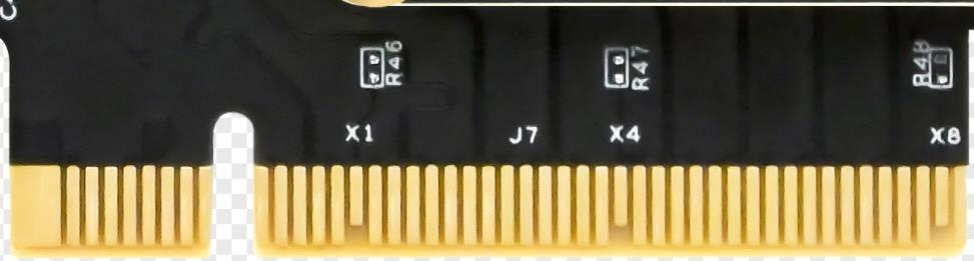

开发板板载了 PCIE3.0 接口,为 X8 接口,如下表列出了PCIE 接口对应关系。

PCIE3.0 | 管脚名称 | 管脚位置 |

PERST_N | IO_3P_84 | AD15 |

REF_CLK_P | MGT_CLK_P0_224 | AB7 |

REF_CLK_N | MGT_CLK_N0_224 | AB6 |

PER0_P | MGT_TX_P0_224 | AF7 |

PER0_N | MGT_TX_N0_224 | AF6 |

PER1_P | MGT_TX_P1_224 | AE9 |

PER1_N | MGT_TX_N1_224 | AE8 |

PER2_P | MGT_TX_P2_224 | AD7 |

PER2_N | MGT_TX_N2_224 | AD6 |

PER3_P | MGT_TX_P3_224 | AC5 |

PER3_N | MGT_TX_N3_224 | AC4 |

PER4_P | MGT_TX_P0_225 | AA5 |

PER4_N | MGT_TX_N0_225 | AA4 |

PER5_P | MGT_TX_P1_225 | W5 |

PER5_N | MGT_TX_N1_225 | W4 |

PER6_P | MGT_TX_P2_225 | U5 |

PER6_N | MGT_TX_N2_225 | U4 |

PER7_P | MGT_TX_P3_225 | R5 |

PER7_N | MGT_TX_N3_225 | R4 |

PET0_P | MGT_RX_P0_224 | AF2 |

PET0_N | MGT_RX_N0_224 | AF1 |

PET1_P | MGT_RX_P1_224 | AE4 |

PET1_N | MGT_RX_N1_224 | AE3 |

PET2_P | MGT_RX_P2_224 | AD2 |

PET2_N | MGT_RX_N2_224 | AD1 |

PET3_P | MGT_RX_P3_224 | AB2 |

PET3_N | MGT_RX_N3_224 | AB1 |

PET4_P | MGT_RX_P0_225 | Y2 |

PET4_N | MGT_RX_N0_225 | Y1 |

PET5_P | MGT_RX_P1_225 | V2 |

PET5_N | MGT_RX_N1_225 | V1 |

PET6_P | MGT_RX_P2_225 | T2 |

PET6_N | MGT_RX_N2_225 | T1 |

PET7_P | MGT_RX_P3_225 | P2 |

PET7_N | MGT_RX_N3_225 | P1 |

开发板板载了一个 USB 转 JTAG 下载器,安装好 Vivado 软件后使用USB 线连接好 JTAG 对应的 USB 口,即可实现调试下载,非常方便。如下是接口在开发板上的位置 图。