CPLD和FPGA的区别

某种专门用途而设计的集成电路称为专用集成电路,即所谓的 ASIC( Application Specific Integrated Circuit)。

ASIC 的使用在生产、生活中非常普遍,比如手机、平板电脑中的主控芯片都属于专用集成电路。

虽然 ASIC 有诸多优势,但是在用量不大的情况下,设计和制造这样的专用集成电路不仅成本很高,而且设计制造的周期也很长。可编程逻辑器件( Programmable Logic Device, PLD)的出现成功解决了这个矛盾。

可编程逻辑器件( Programmable Logic Device,PLD) 是作为一种通用器件被生产的,但它的逻辑功能是由用户通过对器件进行编程来设定的,而且有些 PLD 的集成度很高,足以满足一般数字系统设计的需要。这样就可以由设计人员自行编程, 从而将一个数字系统“ 集成” 在一片 PLD 上,做成“ 片上系统” ( System on Chip, SoC),而不必去请芯片制造厂商设计和制作专用集成电路芯片了。

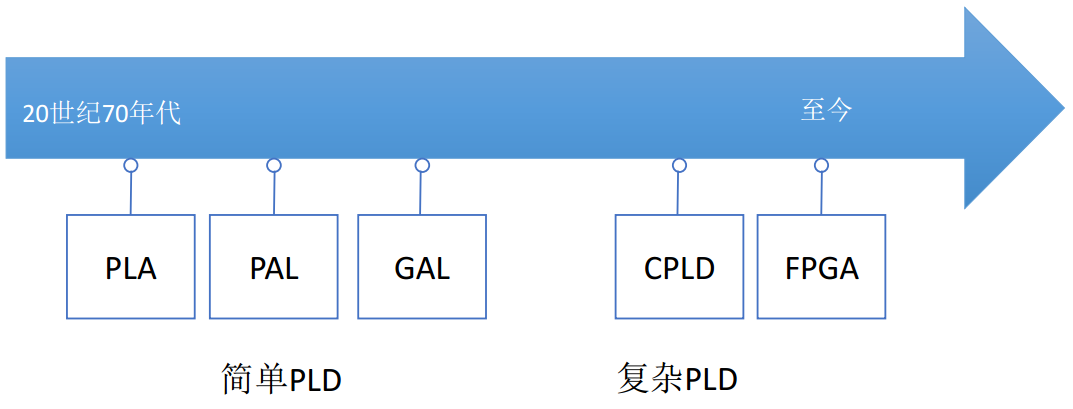

自 20 世纪 70 年代以来, PLD 的研制和应用得到了迅速的发展,相继开发出了多种类型和型号的产品。PLD 的发展历程如下图所示:

目前常见的 PLD 大体上可以分为 SPLD( simple PLD,简单 PLD)、 CPLD( complex PLD,复杂 PLD)和 FPGA( field-programmable gate array,现场可编程门阵列)。

SPLD 中又可分为 PLA、 PAL 和 GAL 几种类型。 FPGA 也是一种可编程逻辑器件,但由于在电路结构上与早期已经广为应用的 PLD 不同,所以采用FPGA 这个名称,以示区别。

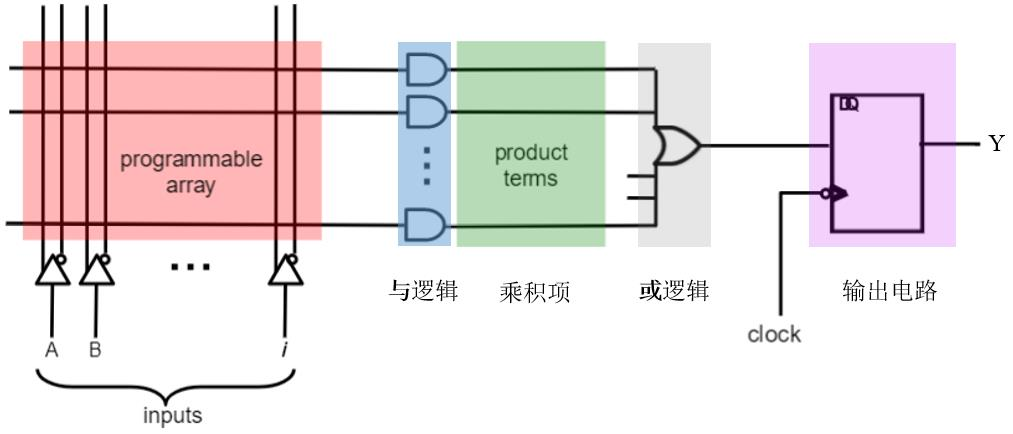

通过对数字电路的学习, 我们知道任何一个逻辑函数式都可以变换成与-或表达式,因而任何一个逻辑函数都能用一级与逻辑电路和一级或逻辑电路来实现。 PLD 最初的研制思想就来源于此。

上图是 SPLD 中 PAL(可编程阵列逻辑)的电路结构图。通过对输入端( input)到与门之间的可编程阵列( programmable array)进行编程,利用 PAL 可以获得不同形式的组合逻辑函数。 我们通过学习数字电路课程可知,任何逻辑函数式都可以转化为若干乘积项( product tems)之和的形式,亦称“ 积之和” 形式。

通过对可编程阵列进行编程, 与逻辑电路输出所需要的乘积项,再通过或逻辑电路将这些乘积项相加,就得到了最终的功能输出。然后该输出送给输出电路中的寄存器用于存储或者同步,当然也可以忽略寄存器直接输出。这就是 PAL 作为一种“ 可编程逻辑器件” 能够实现不同逻辑功能的原理。

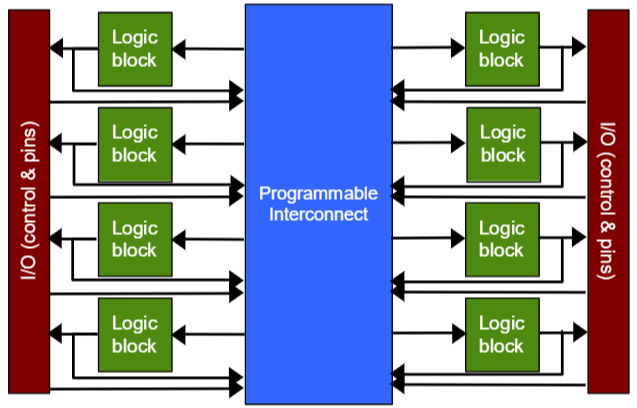

通过扩展 SPLD 的概念就可以得到 CPLD, CPLD 是复杂可编程逻辑器件,相当于将多个 PAL 用可编程互联阵列( Programmable Interconnect Array, PIA)连接起来,形成一个大的 PLD,如下图所示:

上图中的 Logic block(逻辑块)通常被称为逻辑阵列模块, 或者 LAB( Logic Array Block)。每个 LAB相当于一个 PAL 电路,不同型号的 CPLD 器件可以包含十几个甚至上百个 LAB。通过 PIA 将这些 LAB 连接起来,就可以构成规模更大的逻辑电路了。另外,在 PAL 中, I/O 管脚是直接连接到逻辑的。而在 CPLD中, I/O 管脚是通过 PIA 从器件的主要逻辑中分离出来的。 I/O 管脚有它自己的控制逻辑, I/O 控制单元可以根据需要将相应的引脚设置成输入、输出或双向工作模式。

CPLD 相对于 SPLD 最大的优势就是拥有更大的逻辑资源和布线的可能性。 CPLD 中 LAB 逻辑和 PIA是完全可编程的,使得它在单芯片中具有非凡的设计灵活性。 CPLD 的 I/O 特性和功能也远比 SPLD 中简单的 I/O 更有价值。

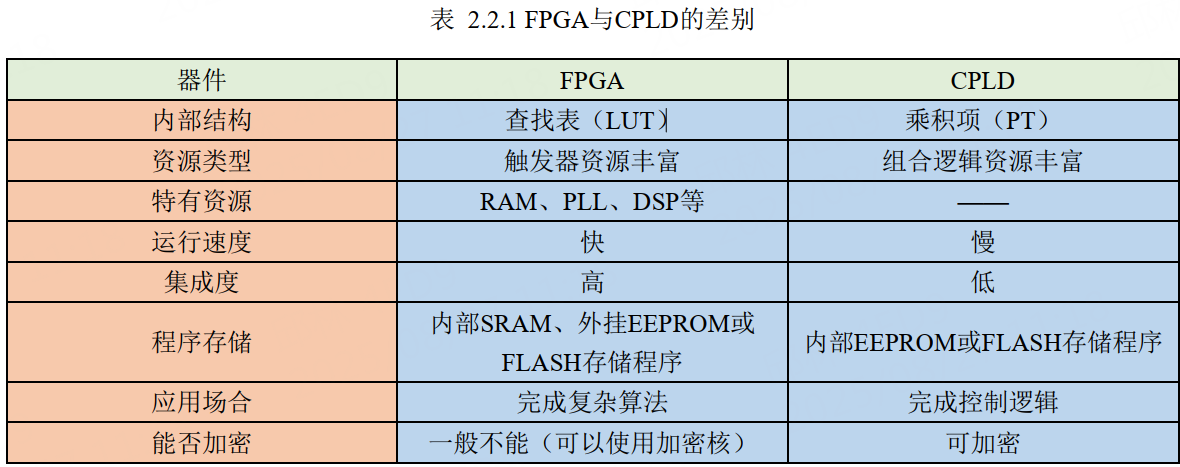

FPGA 是在 PAL、 GAL 和 CPLD 等可编程逻辑器件的基础上进一步发展的产物,但是 FPGA 和其前辈CPLD 有着非常大的差异。我们用一张表格来罗列他们之间的差别如下表所示:

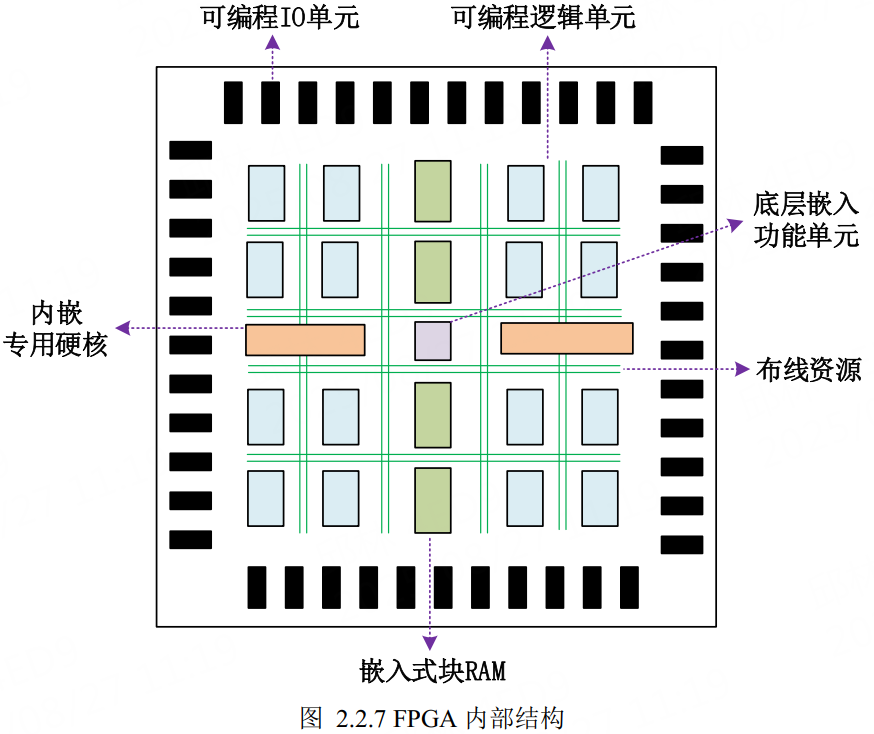

那为什么会产生这么大的差别呢,主要是由于 FPGA 的内部结构决定的,下面我们就来看看 FPGA 的内部结构,如下图所示:

FPGA 基本结构一般由六部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、 底层嵌入功能单元、 布线资源、 嵌入式块 RAM 和内嵌专用硬核。

在内部结构上相比CPLD已经发展很远了,导致他们针对的应用场景也相差很大。