通信算法之317:基于Xilinx FPGA平台的符号同步算法(接收序列与本地序列互相关-不共轭乘)

文章目录

- 一.峰值搜索方法

- 二.接收数据量化

- 三.互相关共轭乘

- 四.累加运算

一.峰值搜索方法

提示:

1.通常采用搜索最大值的方法,这对硬件的实现来说需要比较复杂的逻辑电路与控制电路。因此,从简化硬件设计的角度出发,采用制定门限值的方法来代替,当abs(C) 的值超过了预先设定的门限值,即认为找到了峰值。

二.接收数据量化

提示:

1.训练序列长度为1024个采样点,每个采样点都是复数类型,这样1024个复数乘法器所实现的匹配滤波,势必将占用FPGA上宝贵的乘法器资源,且对运算速度也是不利的。

2.采用持续累加重复训练符号的方法,来降低高斯白噪声的影响,并将接收到的信号量化为{1,-1},这样硬件电路实现时可以省去所有的乘法器

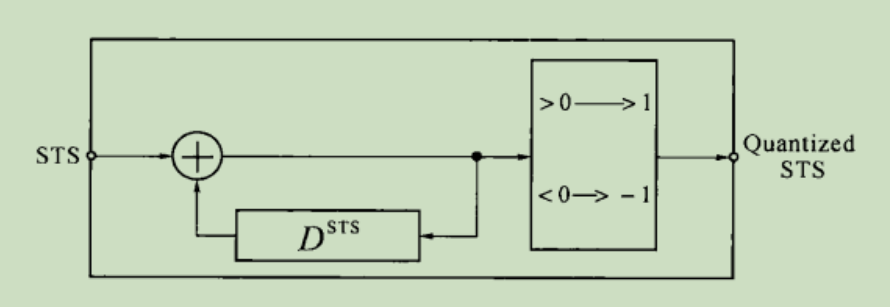

例如:因为复数乘法器需要占用较多的器件资源,为了简化硬件实现,将接收到的信号量化为{1,-1},即大于0的量化为1,而小于0的量化为-1。同时,为了降低高斯白噪声的影响,将重复序列对应位置的值,在量化前持续累加处理。

持续累加参考代码:

12位表示一个符号,16个符号等于192位。

/*持续累加用寄存器 *//////

reg [191:0] Continual_Accumulation_Real;

reg [191:0] Continual_Accumulation_Imag;/*持续累加移位寄存器左移一个单元*****/

Continual_Accumulation_Real[191:12] <= Continual_Accumulation_Real[179:0];

Continual_Accumulation_Imag[191:12] <= Continual_Accumulation_Imag[179:0];

/*最高一个单元与输入数据的12位扩展相加赋值给最低一个单元****/

Continual_Accumulation_Real[11:0] <= {{4{BufferDataR[7]}},BufferDataR} + Continual_Accumulation_Real[191:180];

Continual_Accumulation_Imag[11:0] <= {{4{BufferDataI[7]}},BufferDataI} + Continual_Accumulation_Imag[191:180];

量化参考代码:

移位缓存16个。最高位表示符号位。

/*量化结果移位******//////

Quantization_Result_Real[14:0] <= Quantization_Result_Real[15:1];

Quantization_Result_Imag[14:0] <= Quantization_Result_Imag[15:1];

/*最高位为0,表正,量化为+1, 在此用0代替,下面语句只是用于判断******//////

Quantization_Result_Real[15] <= Continual_Accumulation_Real[11];

/*最高位为1,表负,量化为-1,在此用1表示******//////

Quantization_Result_Imag[15] <= Continual_Accumulation_Imag[11];

三.互相关共轭乘

提示:

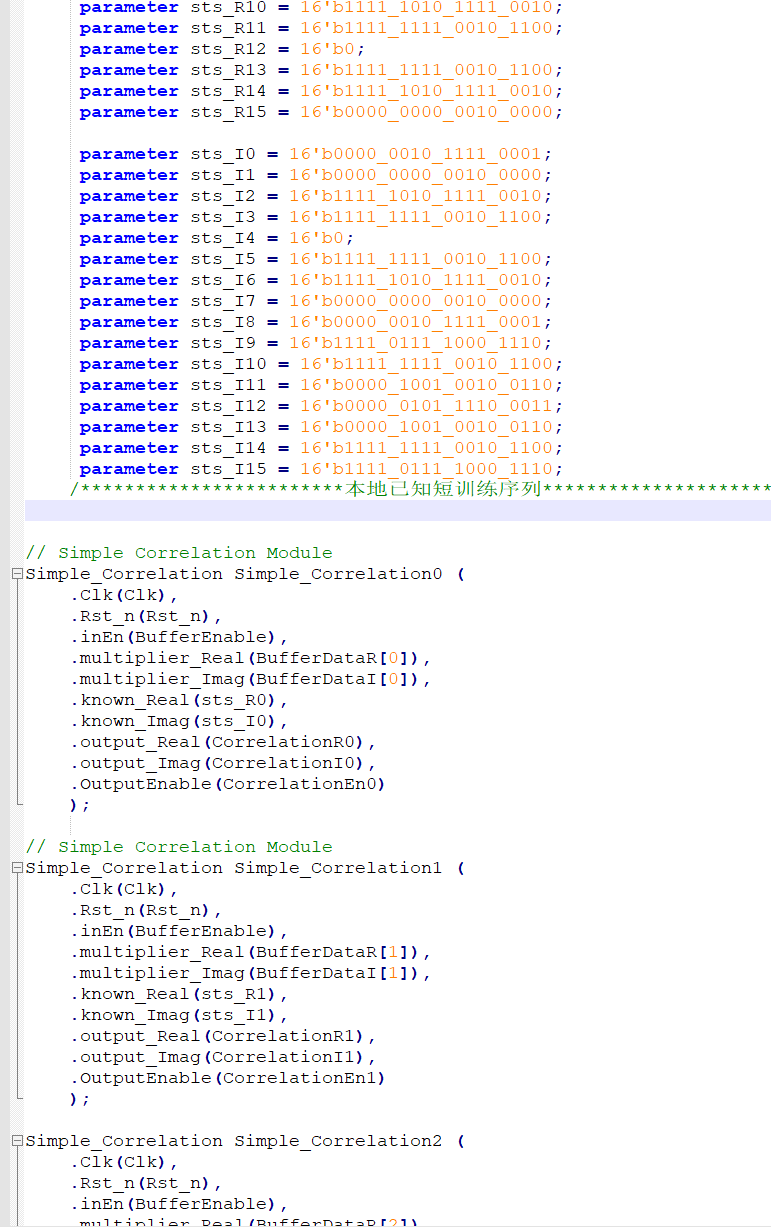

1.接收信号经过量化后,送入匹配滤波单元,首先与本地1024个训练符号取样进行相关计算,并将相关值累加,然后通过寻找其幅值的峰值来确定各个训练符号的位置

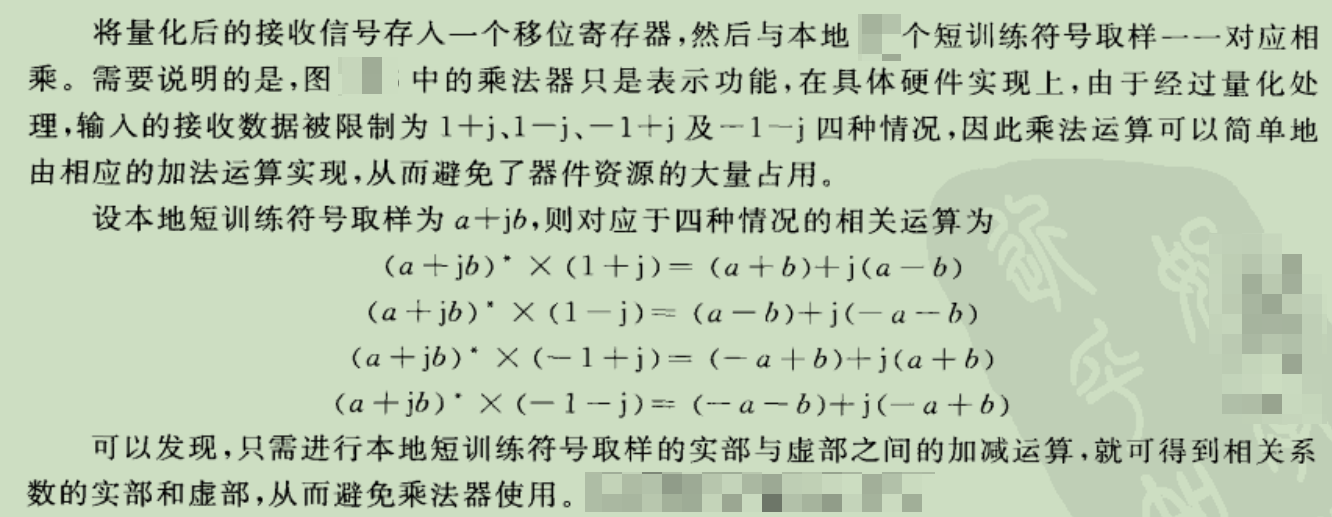

2.互相关运算,不采用乘法器。将乘法运算可以简单地由相应的加法运算实现,从而避免器件资源的大量占用。

例如:

共轭乘替代加减法 参考代码:

input multiplier_Real; /*移位寄存器实部******//////

input multiplier_Imag; /*移位寄存器虚部******//////

input [15:0] known_Real; /*本地已知短训练序列实部,二进制补码表示*******///////

input [15:0] known_Imag; /*短训练序列虚部*******///////

output [16:0] output_Real; /*输出实部,扩展为17位输出,输出为二进制补码表示*******///////

output [16:0] output_Imag; /*输出虚部*******////////*输入的multiplier等于0表示正数,等于1表示负数*****//////

if (multiplier_Real == 0 && multiplier_Imag == 0) beginoutput_Real <= {{1{known_Real[15]}},known_Real} + {{1{known_Imag[15]}},known_Imag};output_Imag <= {{1{known_Real[15]}},known_Real} - {{1{known_Imag[15]}},known_Imag};endelse if (multiplier_Real == 0 && multiplier_Imag == 1)beginoutput_Real <= {{1{known_Real[15]}},known_Real} - {{1{known_Imag[15]}},known_Imag};output_Imag <= - {{1{known_Real[15]}},known_Real} - {{1{known_Imag[15]}},known_Imag};endelse if (multiplier_Real == 1 && multiplier_Imag == 0)beginoutput_Real <= - {{1{known_Real[15]}},known_Real} + {{1{known_Imag[15]}},known_Imag};output_Imag <= {{1{known_Real[15]}},known_Real} + {{1{known_Imag[15]}},known_Imag};endelse //(buffer_multiplier_Real==1 && buffer_multiplier_Imag==1)beginoutput_Real <= - {{1{known_Real[15]}},known_Real} - {{1{known_Imag[15]}},known_Imag};output_Imag <= - {{1{known_Real[15]}},known_Real} + {{1{known_Imag[15]}},known_Imag};end

四.累加运算

提示:参考代码:

wire [16:0] CorrelationR0;

reg [20:0]CorrelationSumR;

/*赋值语句右边的操作数位宽已扩展为21位,跟左边的结果位宽一致,保证带符号位二进制加法运算的正确性*******//////CorrelationSumR <= ((({{4{CorrelationR0[16]}},CorrelationR0} + {{4{CorrelationR1[16]}},CorrelationR1}) + ({{4{CorrelationR2[16]}},CorrelationR2} + {{4{CorrelationR3[16]}},CorrelationR3})) + (({{4{CorrelationR4[16]}},CorrelationR4} + {{4{CorrelationR5[16]}},CorrelationR5})+ ({{4{CorrelationR6[16]}},CorrelationR6} + {{4{CorrelationR7[16]}},CorrelationR7}))) + ((({{4{CorrelationR8[16]}},CorrelationR8} + {{4{CorrelationR9[16]}},CorrelationR9})+ ({{4{CorrelationR10[16]}},CorrelationR10} + {{4{CorrelationR11[16]}},CorrelationR11})) + (({{4{CorrelationR12[16]}},CorrelationR12} + {{4{CorrelationR13[16]}},CorrelationR13})+ ({{4{CorrelationR14[16]}},CorrelationR14} + {{4{CorrelationR15[16]}},CorrelationR15})));