Diamond基础2:开发流程之LedDemo

文章目录

- 1.关联VS Code

- 2.Diamond工程目录

- 3.Led Demo开发流程

- 4.烧写bit文件

- 5.传送门

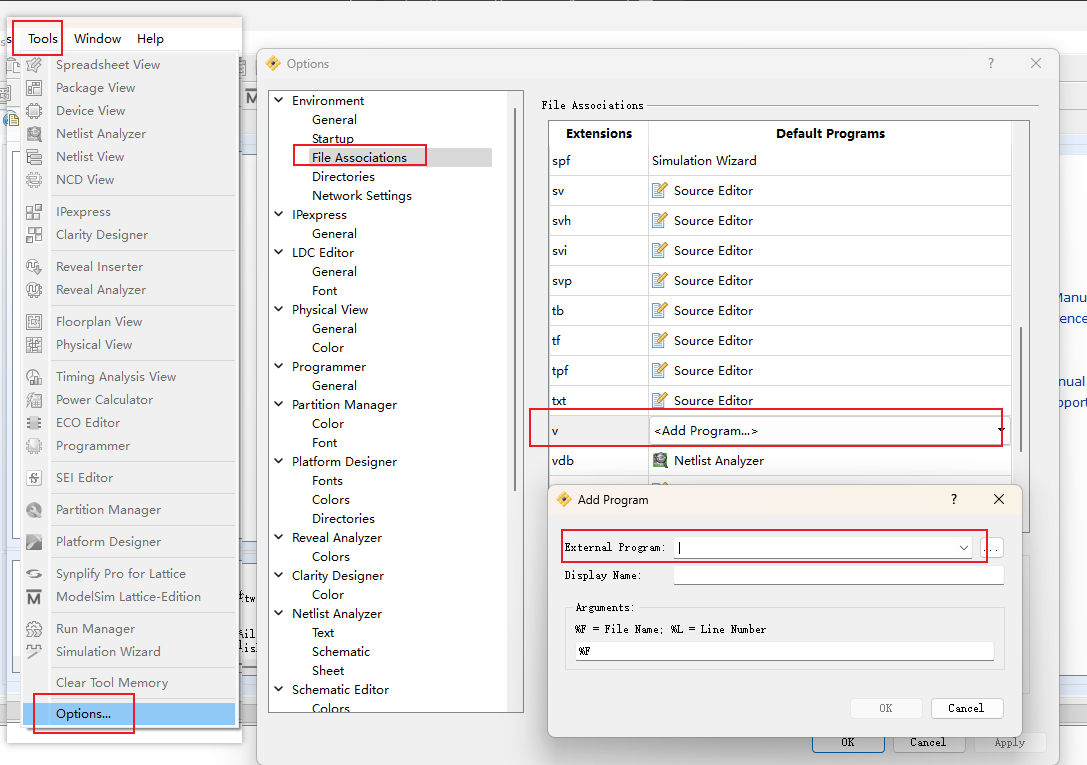

1.关联VS Code

和Vivado一样,Diamond也可以使用第三方的编辑器,VS Code编辑器因为可以安装各种插件,并且对verilog开发的支持也算完善,所以很受欢迎。关于VS Code具体插件和汉化包参考Vivado关联VS Code文本编辑器。具体操作如下,选择tools–>Options–>File Associations,然后选择v文件,点击打开将VS Code安装路径选上即可。

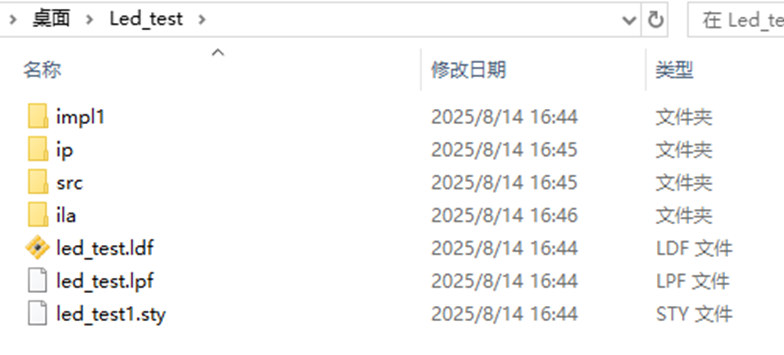

2.Diamond工程目录

如图所示,Diamond不会像Vivado一样有相对整洁的目录,所以通常会在工程目录下根据自己的习惯建立子文件夹以便于工程管理。我的习惯是src文件放源文件即.v文件,ip目录放工程中用到的IP核生成的文件,ila放Diamond的在线监测工具reveal的相关文件。

3.Led Demo开发流程

写一个两个led交替闪烁的程序熟悉Diamond的开发流程。具体操作如下:

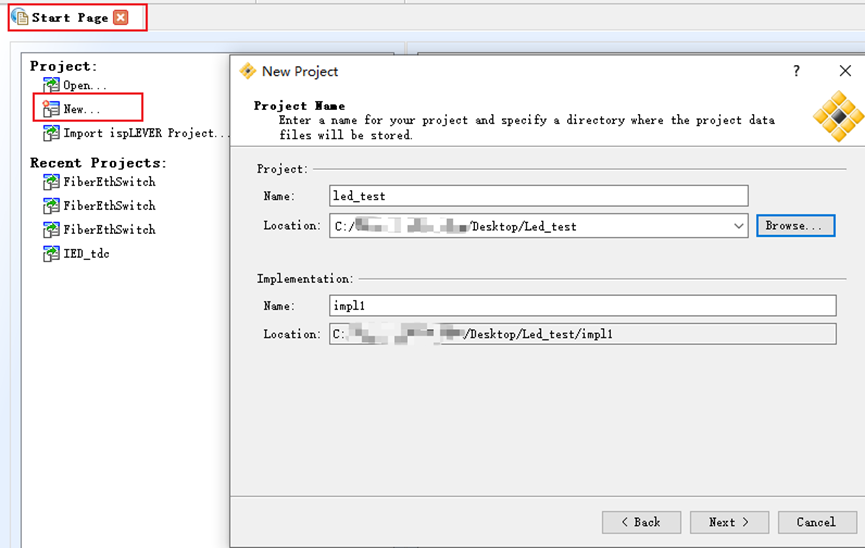

①在Start Page界面选择New,然后输入工程名字和保存路径,点击Next。

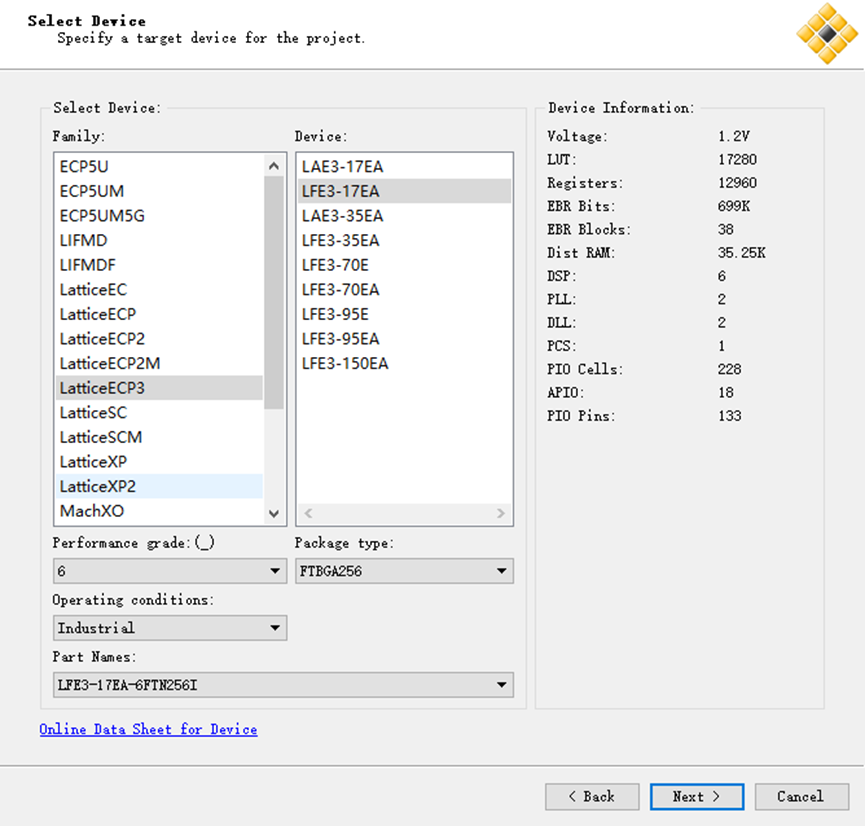

②选择相应的FPGA型号,点击Next

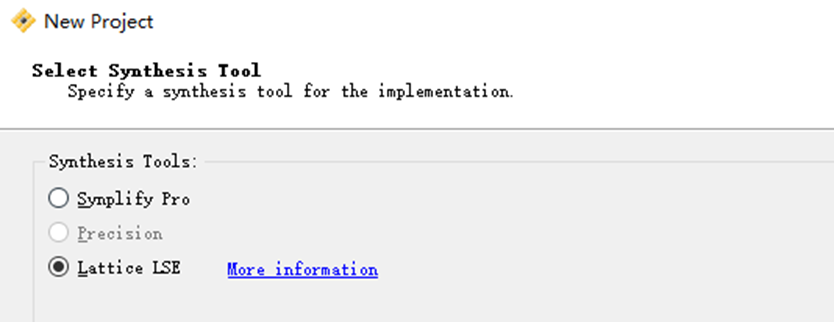

③任选一个综合工具,点击Next

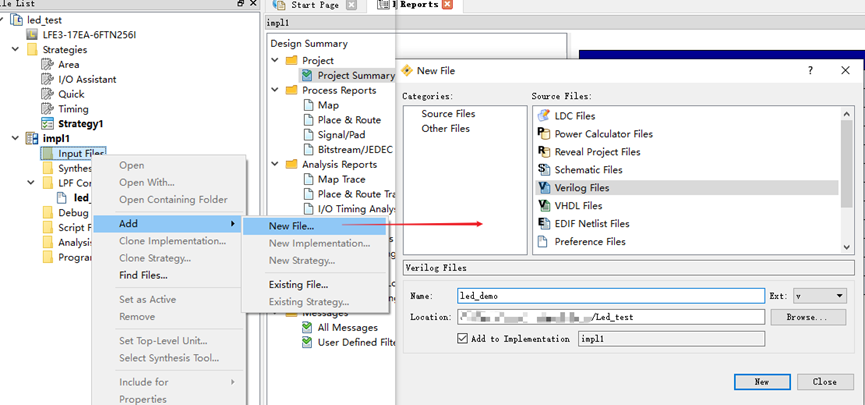

④随后邮件Input File,选择Add–>New File选择Verilog Files 输入名字和保存位置即可。

⑤双击源文件,打开vs code编辑器,输入以下代码,可以看到工程实现是led1和led2交替闪烁。

module LED_demo

(

input clk_i, //输入系统时钟

input rst_n, //输入复位信号

output led1, //输出led1

output led2 //输出led2,与led1取反

);

parameter CLK_DIV_PERIOD=125_000_000;

reg clk_div=0;

assign led1=clk_div;

assign led2=~clk_div;

reg[23:0] led_cnt=0; //分频用的计数器

always@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginled_cnt<=0;end else if(led_cnt==(CLK_DIV_PERIOD-1)) beginled_cnt<=0;end else beginled_cnt<=led_cnt+1'b1;end

endalways@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginclk_div<=0;end else if(led_cnt<(CLK_DIV_PERIOD>>1)) begin clk_div<=0;end else beginclk_div<=1;end

end

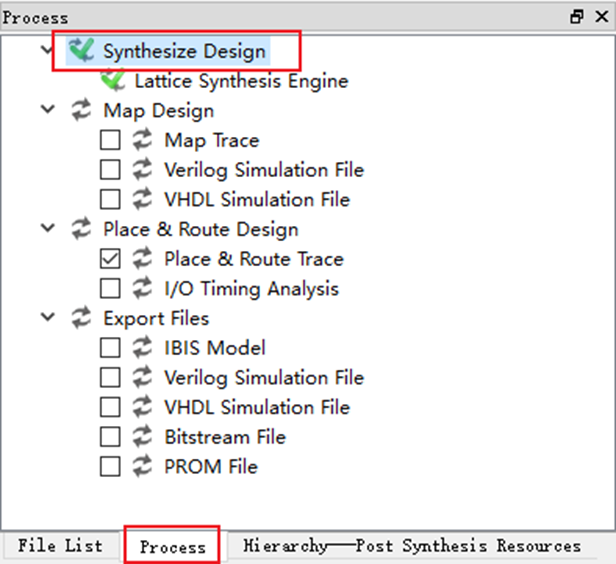

endmodule⑥随后点击Sythesis Design,知道出现绿色对勾显示综合通过

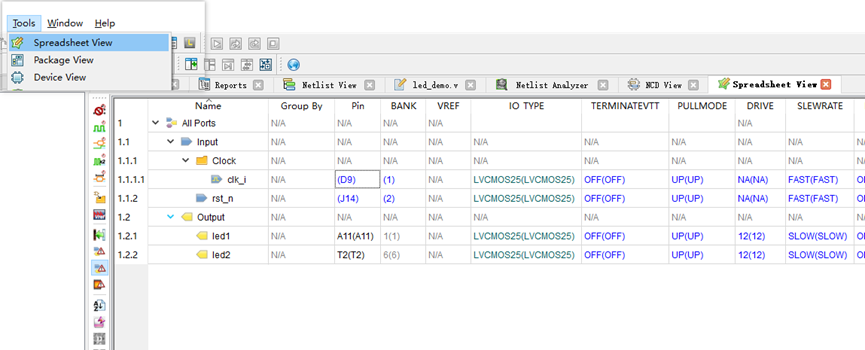

⑦点击Tools–>Spreadsheet View为工程添加引脚约束信息。

⑧在Process界面点击Bitstream File即可生成bit文件

4.烧写bit文件

连接Jtag,给板子上电

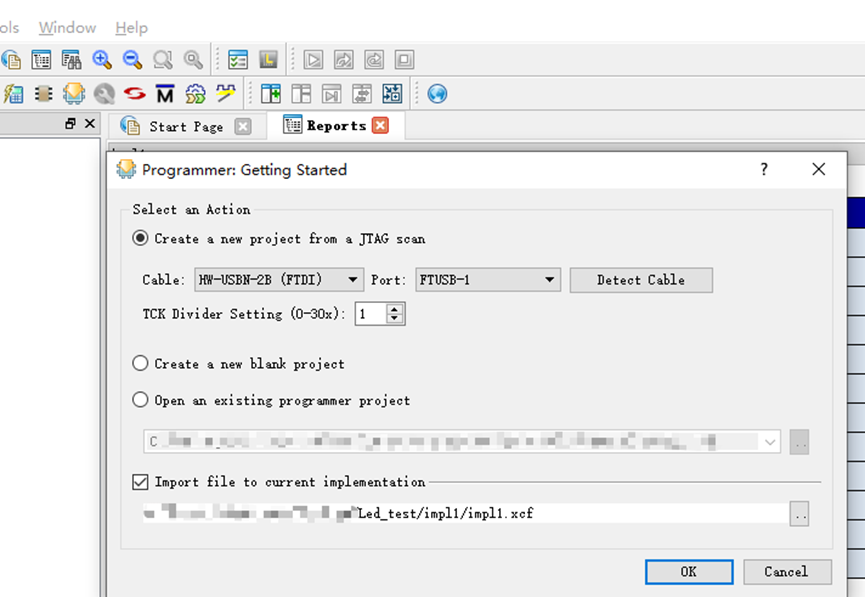

①选择下图中黄色箭头向下的图标,打开Programmer:Getting Started界面,选择Create a new project from a JTAG scan,如图中显示的Port:FTUSB-1,这是我故意连了两个JTAG,这里要对应好自己板子的port号,可单击Detect Cable之后选择对应Port。点击OK进入下一步。

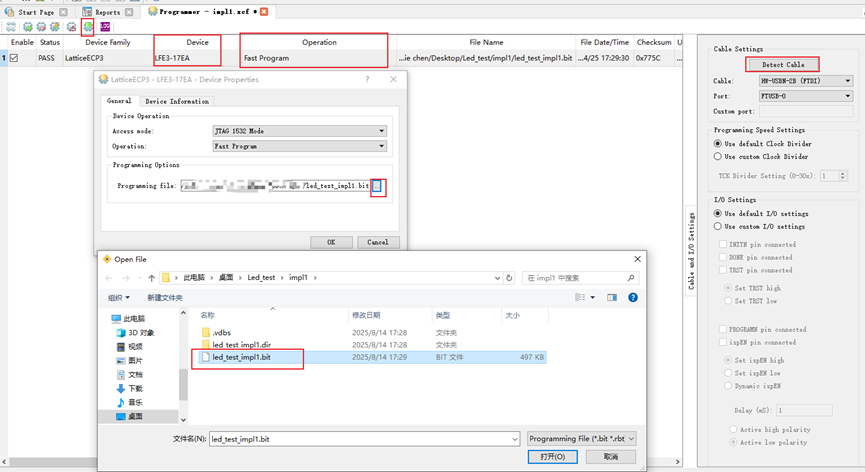

②点击Device处选择对应FPGA型号,单击Fast Program,出现图中界面选择烧写的bit文件,然后单击绿色图标下载程序。

5.传送门

- 我的主页

- Lattice进阶之路汇总导航

- 上一篇:认识Lattice器件

| END |

📡文章原创,首发于CSDN论坛。

📡欢迎点赞♥♥收藏⭐⭐打赏💵💵!

📡欢迎评论区或私信指出错误💉,提出宝贵意见或疑问😱。