友思特方案 | FPGA 加持,友思特图像采集卡高速预处理助力视觉系统运行提速增效

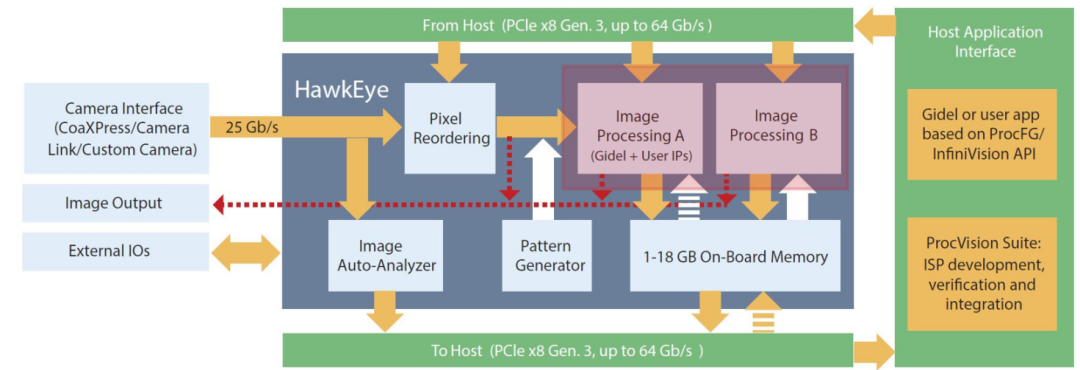

图像预处理是图像处理关键中间环节,通过优化传感器到主机的数据传输处理为后续减负。其算法依托硬件执行,搭载 FPGA 的友思特图像采集卡以高速运算和并行特性缩短处理时间、降低延迟并提升吞吐量,助力高速分拣等系统快速决策。针对高速接口及实时 / 大数据量场景,该采集卡是必备组件,可在 FPGA 上完成去拜耳化、HDR 等预处理,为视觉系统高效运行奠基。

前言

图像预处理是图像处理过程中的一个中心中间步骤,图像从传感器到图像采集卡中进行处理,再到在主机 PC 中输出结果。它确保图像数据针对相应的应用进行优化,安全地传输。图像预处理的目的是准备数据,以简化进一步的处理步骤并减轻主机PC处理的负担。

预处理中使用的图像处理算法取决于相机传感器的现有的图像质量。这些算法可以在图像采集卡的板载FPGA上执行,也可以在其他视觉硬件(如相机本身、后端PC等)上执行。

而FPGA的高速运算和并行特性可缩短图像处理时间,从而降低系统延迟和提高吞吐量。此外,FPGA图像处理可以允许高速分拣机、表面和幅材检测等系统的控制器更快速地基于所采集的图像作出决策

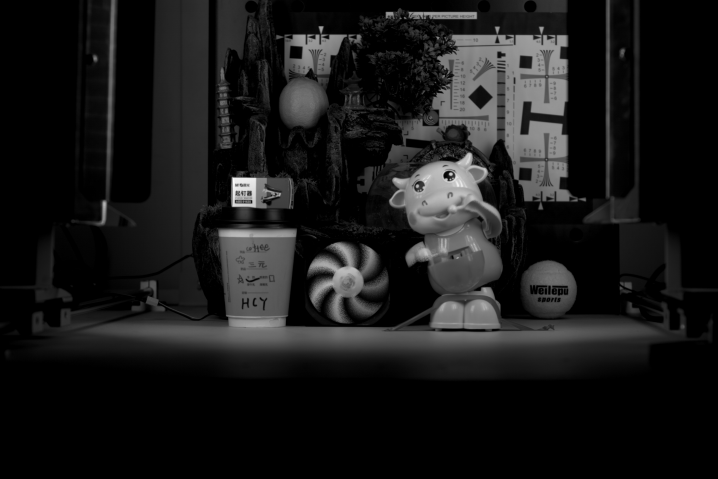

(友思特FPGA图像采集卡)

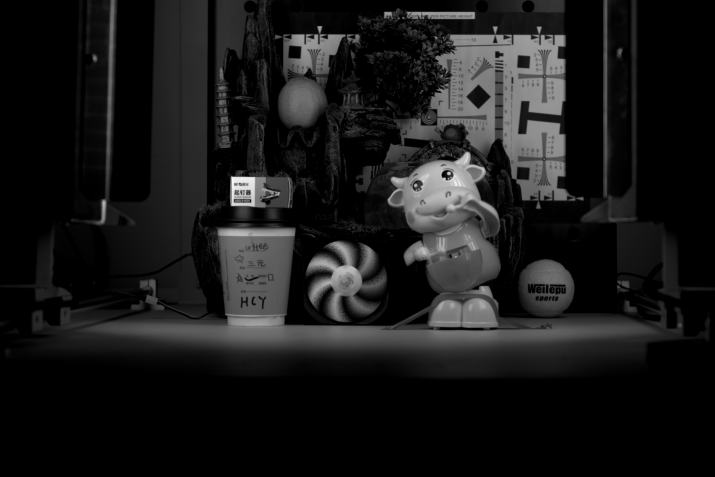

(FPGA vs PC预处理CPU使用对比)

对于高速接口(如 CoaXPress、Camera Link 和 Camera Link HS)而言,图像采集卡是整个系统搭建必要组件,并且对于实时要求较高或大数据量传输来说,图像采集卡是必不可少的。它可以直接在FPGA上进行更广泛的预处理。例如高质量的去拜耳化、图像有损/无损压缩、高动态范围(HDR)、Blob分析、白平衡等,具体取决于应用。

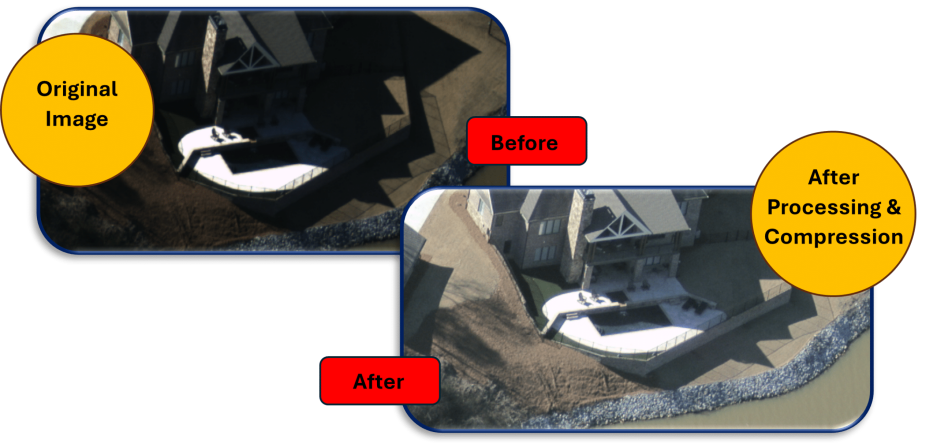

通过压缩减少数据量:JPEG压缩,Lossless压缩,Quality+压缩

方案一:Quality+压缩方案

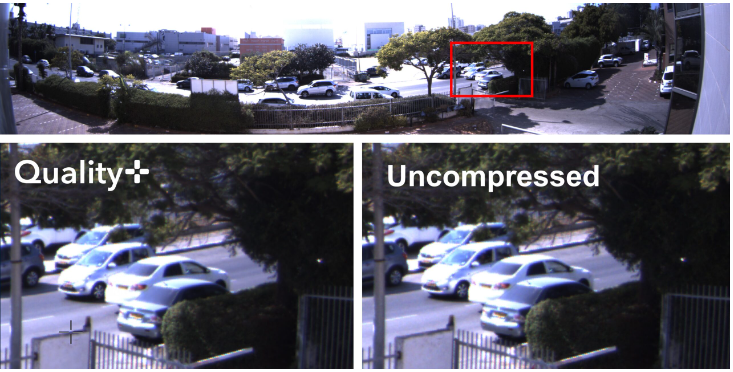

1:20+ 压缩比情况下保证更加优秀图像质量

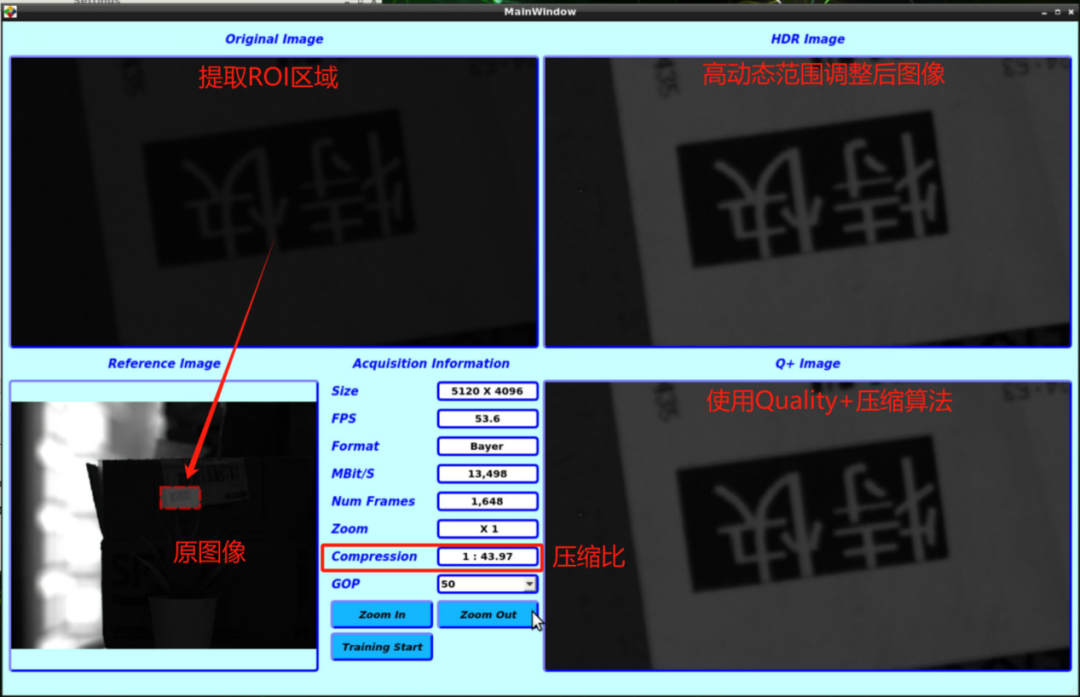

友思特合作伙伴Gidel的Quality+(Q+)压缩算法实时压缩彩色滤镜阵列(CFA - 例如,拜耳)、Mono、RGB图像和视频。

Q+算法彻底改变了传统图像压缩算法,在保持原始图像质量的同时,为高带宽图像流实现了高达 1:20+ 甚至更高的压缩比。

与会降低图像保真度的传统压缩方法不同,Quality+通过保持原始信噪比(SNR)来保持图像质量不降低,同时智能优化压缩,Quality+通过将图像中的无效噪声替换为压缩高效的噪声,从而在不牺牲关键细节的情况下提高压缩效率。

Quality+算法支持动态训练,允许系统根据特定视频流特征自适应优化压缩参数,确保针对不同应用场景(如半导体检测、高速运动捕捉)实现压缩效率最大化。Quality+运行于HawkEye系列FPGA图像采集卡,彻底释放 CPU/GPU负载算力压力,支持千兆像素/秒级吞吐量,实现无瓶颈压缩处理。

(通过调整GOP值,实现图像质量与压缩间平衡)

Quality+具有最小的延迟和帧延迟下的处理,可确保实时响应能力,使其成为录制和流媒体应用程序的理想解决方案。

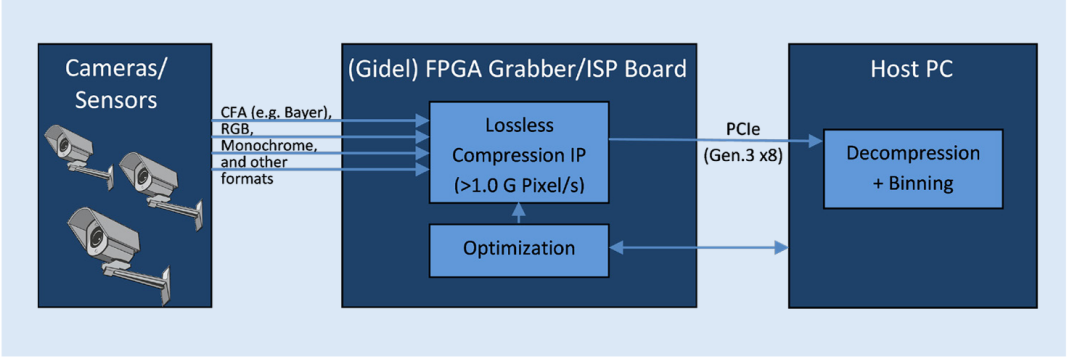

方案二:无损压缩方案

两种压缩模式,多种素材格式实时压缩

通过在FPGA上实现的无损压缩IP,可对彩色滤光片阵列(CFA – 例如拜耳)、Mono和RGB图像和视频执行实时压缩。在Airra 10 FPGA 资源上,在实际视频应用中实现了接近1:3的无损压缩比。

并且根据不同压缩方式,得到的压缩效果也有差异,主要有两种压缩模式:

√ 压缩单个图像帧

√ 使用I帧和P帧对整个视频实现更高压缩比

同时,压缩可以通过基于样本图像数据的预训练或基于实时数据的动态训练优化。

|

|

压缩前 2400*1600,10.9MB | 无损压缩后 2400*1600,3.66MB |

方案三:实时JPEG压缩方案

压缩程度可选,平衡存储大小和图像质量

实时JPEG图像压缩(编码器)IP可在FPGA上实现高性能JPEG压缩。压缩IP具有快速处理能力、低延迟和紧凑的芯片利用率。由于其紧凑性,该压缩IP可以在小型FPGA器件上实现,以实现高性能的相机图像流压缩,或者,该IP可以在单个较大的FPGA器件上多次部署。

JPEG压缩IP的输入流为YCbCr格式,带有RGB、Mono等可选的转换器。用户可以调整图像压缩程度,从而在存储大小和图像质量之间进行选择性权衡。

|

|

压缩前 2400*1600,10.9MB | JPEG压缩后 2400*1600,2.13MB |

(JPEG压缩IP支持压缩比例动态调整,存储大小和图像质量之间进行选择性权衡)

HDR扩大图像动态范围

主要特点

√ 高性能单次曝光实现高动态范围 (HDR)

传统 HDR 依赖于多次曝光,但这种方法对于涉及运动或高数据速率的应用程序来说通常是不切实际的。友思特HDR IP 通过创新的单次曝光算法克服了这些限制,使用基于FPGA的处理提供完美的HDR质量和性能。

√ 高图像质量和无限吞吐量

通过提供实时、高质量的 HDR,几乎零延迟的图像预处理IP。HDR IP不仅分析每个像素的亮度数据,还分析周围像素,动态调整 HDR 处理以考虑局部亮度变化,从而脱颖而出。这种环境敏感的方法可以增强细微的细节,即使在具有挑战性的照明下也是如此,从而提供具有出色保真度的图像。Gidel专有的HDR 算法与FPGA架构相结合,能够同时处理无限的多个像素,从而在超宽像场中实现高速、高效的 HDR 性能。

√ 集成到 ISP 管道

同时HDR CPU卸载可以轻松集成到HawkEye图像采集卡和 FPGA 模块中。它可以与用户IP和/或其他实时、零延迟图像增强模块结合使用,例如Gamma 校正、白平衡、去拜耳化和压缩等。这种模块化方法允许完全优化的端到端解决方案,以满足任何成像应用的特定需求。

|

|

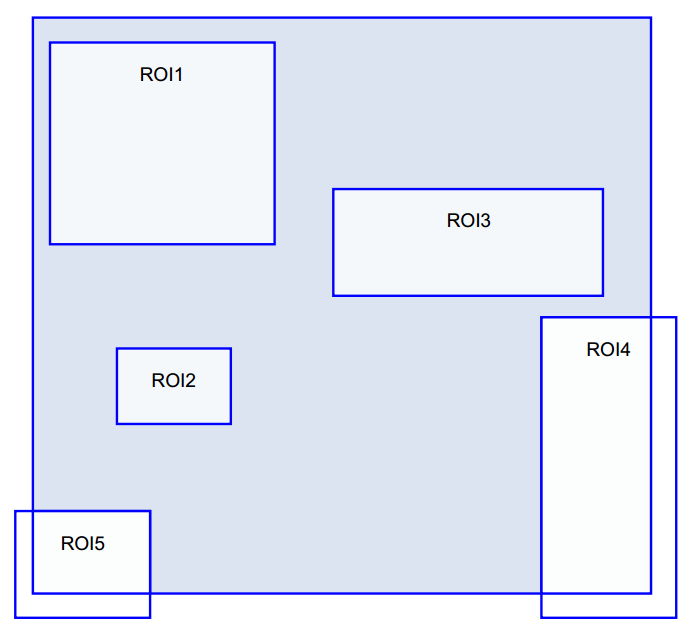

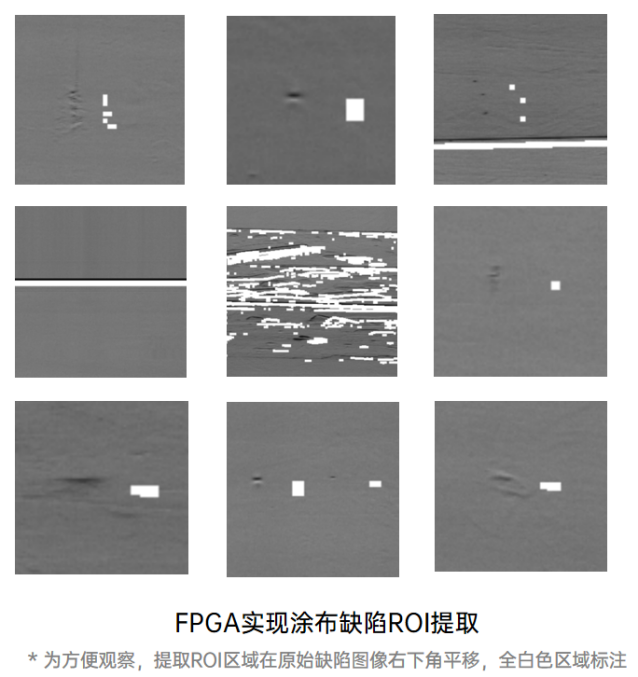

ROI提高传输速率,专注感兴趣区域处理

友思特HawkEye采集卡的优势在于,能够在板载FPGA上实时处理识别图像中的感兴趣区域(ROIs),并能智能、动态地调整ROI区域和参数并优化传输效率。FPGA通过硬件并行性(如流水线处理和定制IP核)实现微秒级ROI提取。同时板载图像处理可实现仅传输ROI数据(而非全帧),降低传输负载,实现高效数据传输。

|

|

友思特图像预处理解决方案

PCIE图像采集卡

提供GigE Vison、Cameralink、Coaxpress等多种接口的图像采集卡,兼容性极强,采用强大的Arria 10 FPGA,具备大容量内存、高带宽数据传输通道和丰富的I/O接口,保证100%的帧捕获,广泛用于实时、高带宽视觉和图像处理等应用。

FantoVision嵌入式边缘计算机

基于FPGA和GPU实现20Gb/s & 40Gb/s高带宽图像采集、记录与处理的嵌入式边缘计算机,FantoVision的架构使用NVIDIA Jetson嵌入式计算机与高端图像采集的实时图像处理结合起来,具有高性能的FPGA处理能力,开放式架构,可自定义图像处理,为各类应用场景带来更高的处理速度和更高带宽选择。