LVDS系列23:Xilinx Ultrascale系ISERDESE3原语(一)

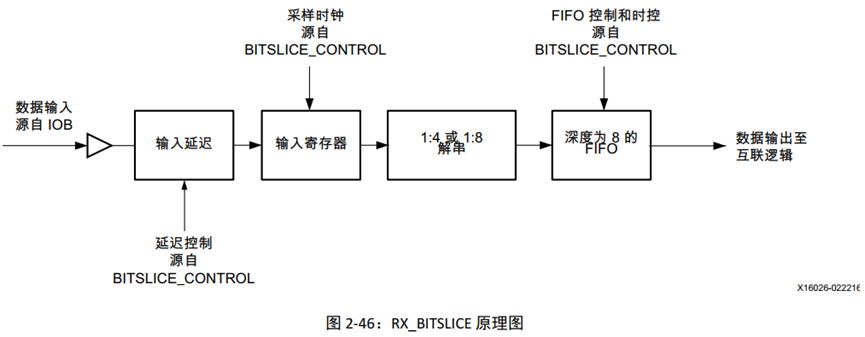

Ultrascale系列的输入的解串器处于如下位置,

ISERDESE3与ISERDESE2存在一些不同:

ISERDESE3没有bitslip比特滑动操作,如果用户需要比特滑动逻辑需要自己编写;

没有CE时钟输入控制,没有OFB直接连接OSERDES的端口,

没有级联的SHIFTIN和SHIFTOUT端口,

ISERDESE3也不带有BITSLIP位滑动功能了,如此位滑动的逻辑也需要额外编写逻辑实现;

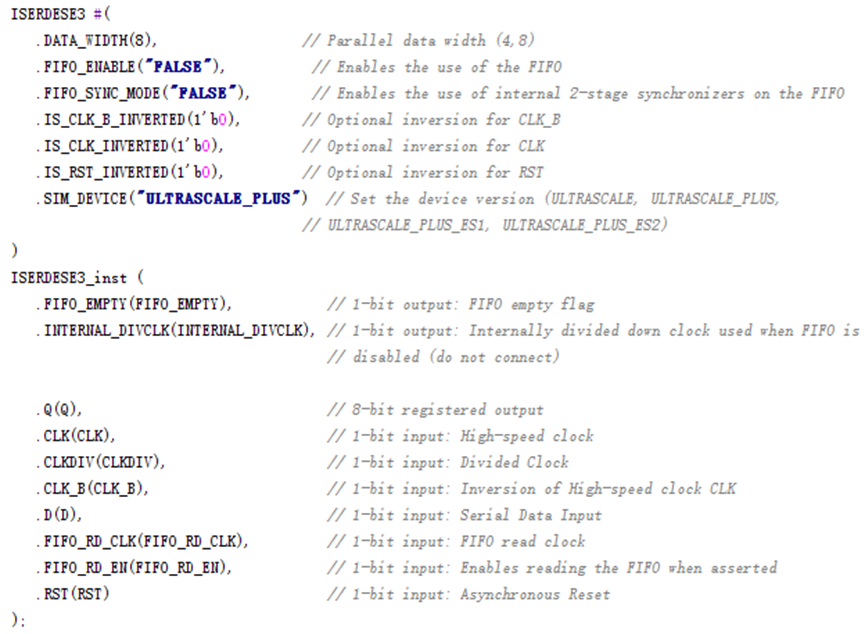

例化模板:

例化端口:

其中CLK是随高速输入数据D输入的高速串行时钟,CLK_B或为其方向版本;

CLK_DIV是低速分频时钟,与输出数据Q端口同步;

当选择启用FIFO时,解串的数据可以从FIFO读出;

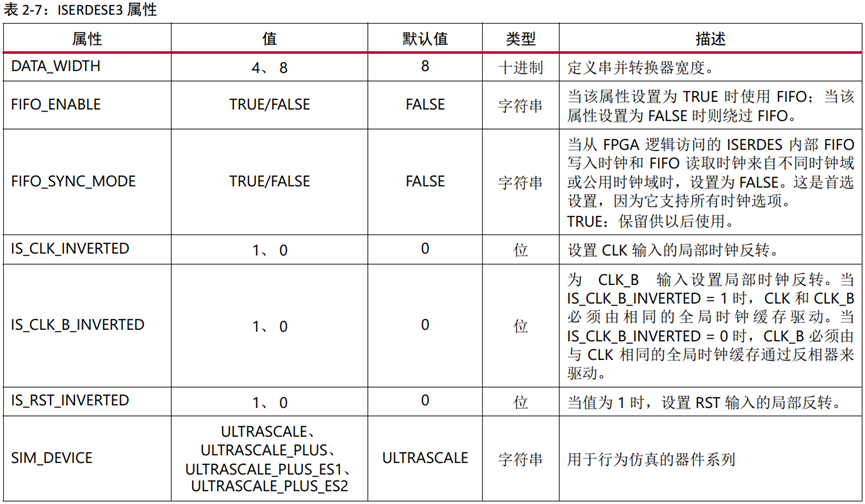

例化参数:

DATA_WIDTH解串宽度支持4和8两个值,

FIFO_ENABLE设置为TRUE,那么解串输出使用FIFO输出,设置为FALSE则不适用FIFO;

FIFO_SYNC_MODE设置FIFO是否为异步FIFO,这里可以看出FIFO可以用作跨时钟域,

IS_CLK_INVERTED、IS_CLK_B_INVERTED设置CLK和CLK_B是否反转,一般情况下设置0;

IS_RST_INVERTED设置复位是否反转,一般情况下设置0;

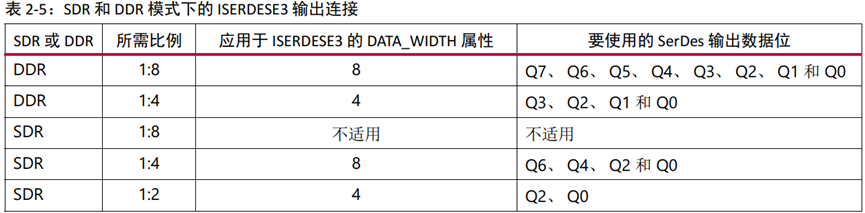

解串比例:

ISERDESE3对比ISERDESE2的解串比例选择也少了,SDR数据可按2位或4位解串,DDR数据可按4位或8为解串,关于在各个解串比例下,使用的输出的数据线Q如下表所示:

如果想要实现其他的解串比例,就需要额外编写逻辑处理,

但是我们看到端口和参数里没有SDR和DDR的选项,

ISERDESE2中的SDR和DDR选择是显式指定的,

但ISERDESE3则是隐式指定,需要CLK、CLK_B和DATA_WIDTH来一同配合:

DDR模式:CLK连接到高速时钟,CLK_B连接到CLK的反相,同时DATA_WIDTH设置为4,解串比例1:4,DATA_WIDTH设置为8,解串比例1:8;

SDR模式:CLK连接到高速时钟,CLK_B连接到地,也就是1’b0,同时DATA_WIDTH设置为4,解串比例1:2,DATA_WIDTH设置为8,解串比例1:4;

FIFO使用:

在使用FIFO时,将端口FIFO_EMPTY直接取反后连接到FIFO_RD_EN端口驱动读使能,ISERDESE3带有一个8元素的FIFO,由FIFO的空信号直接取反控制读使能,而不是由外部逻辑控制读使能,这是为了避免FIFO读指针和写指针在8周期内发生重叠;

当参数FIFO_SYNC_MODE设置为FALSE时,可以将FIFO设置为异步FIFO,此时FIFO_RD_CLK端口输入的时钟可以和CLKDIV分频时钟来自不同时钟域,但是其时钟频率需保持一致;

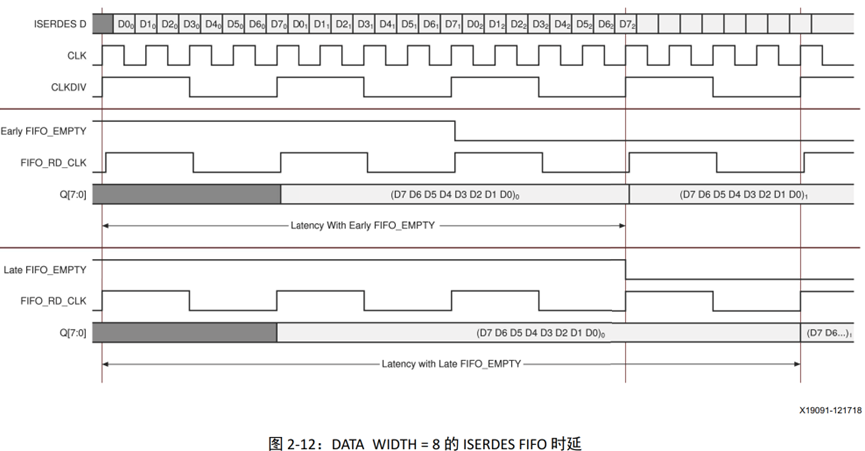

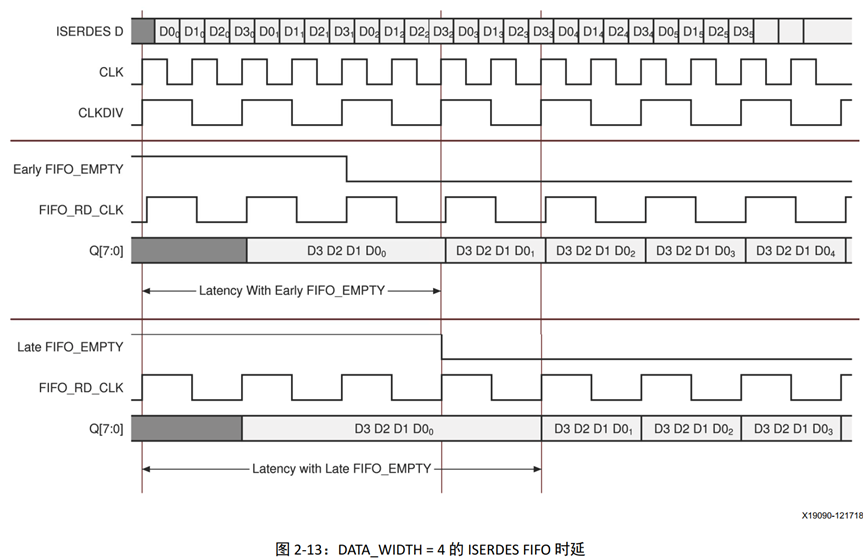

通过FIFO的时延如下两图所示:

当FIFO写指针更新时间相对于FIFO_RD_CLK较早时,通过FIFO的时延较短,

FIFO写侧是CLKDIV时钟控制,如上两图所示,

当FIFO_RD_CLK上升沿较CLKDIV偏后时,也就是出现Latency With Early FIFO Empty情况时,延时较短,也就是在FIFO_RD_CLK上升沿时,CLKDIV刚好提前一点驱动FIFO_EMPTY变化;

当FIFO_RD_CLK与CLKDIV对齐时,也就是Latency With Late FIFO Empty情况时,延迟比前一种情况长一个FIFO_RD_CLK时钟周期,也就是在FIFO_RD_CLK上升沿后一点,CLKDIV才成功驱动完FIFO_EMPTY的变化,于是读侧要得到FIFO_EMPTY为0的情况则要等到下一个FIFO_RD_CLK的上升沿采集时;

本文章由威三学社出品

对课程感兴趣可以私信联系