QD9361开发板教程:基于MIG IP的PL端DDR3测试

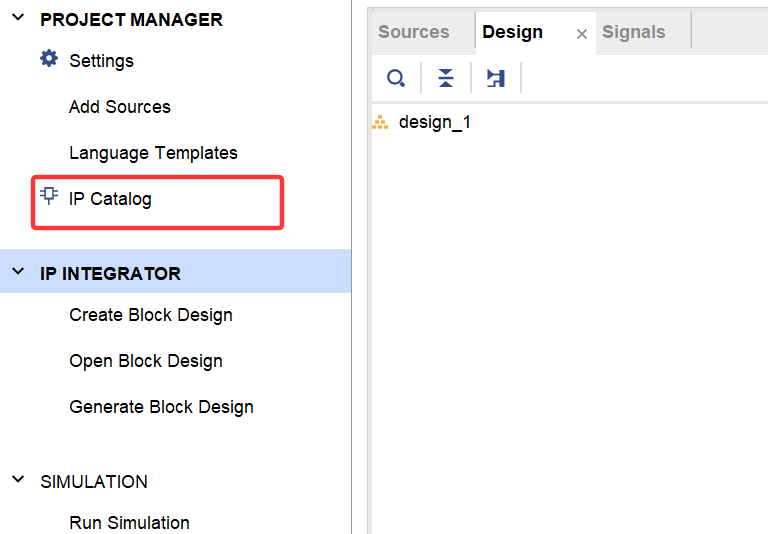

首先我们先建立一个工程,芯片型号选择xc7z100ffg900-2,创建完成点击IP Catalog,添加IP如图所示

|

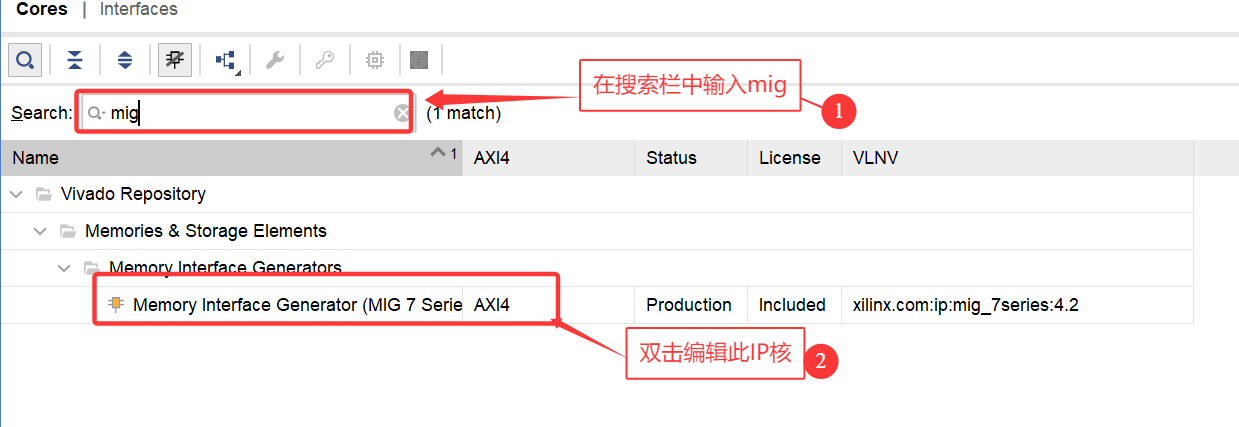

在搜索栏中输入mig,然后双击打开此IP核。

|

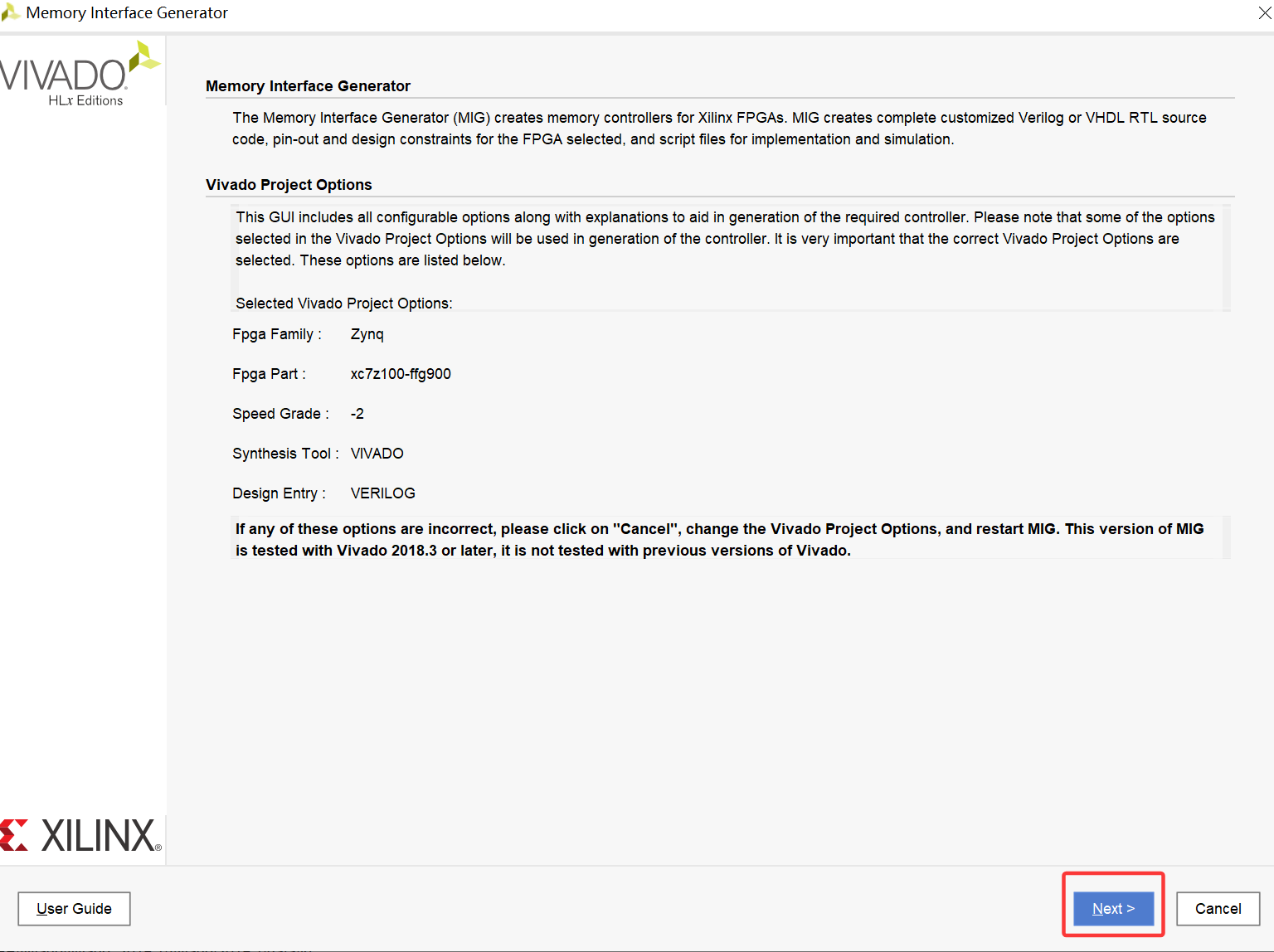

等待一会后,会出现此界面,该界面显示MIG的功能以及本工程选定的fpga器件型号,我使用的是xc7z100器件,直接进入下一步。

|

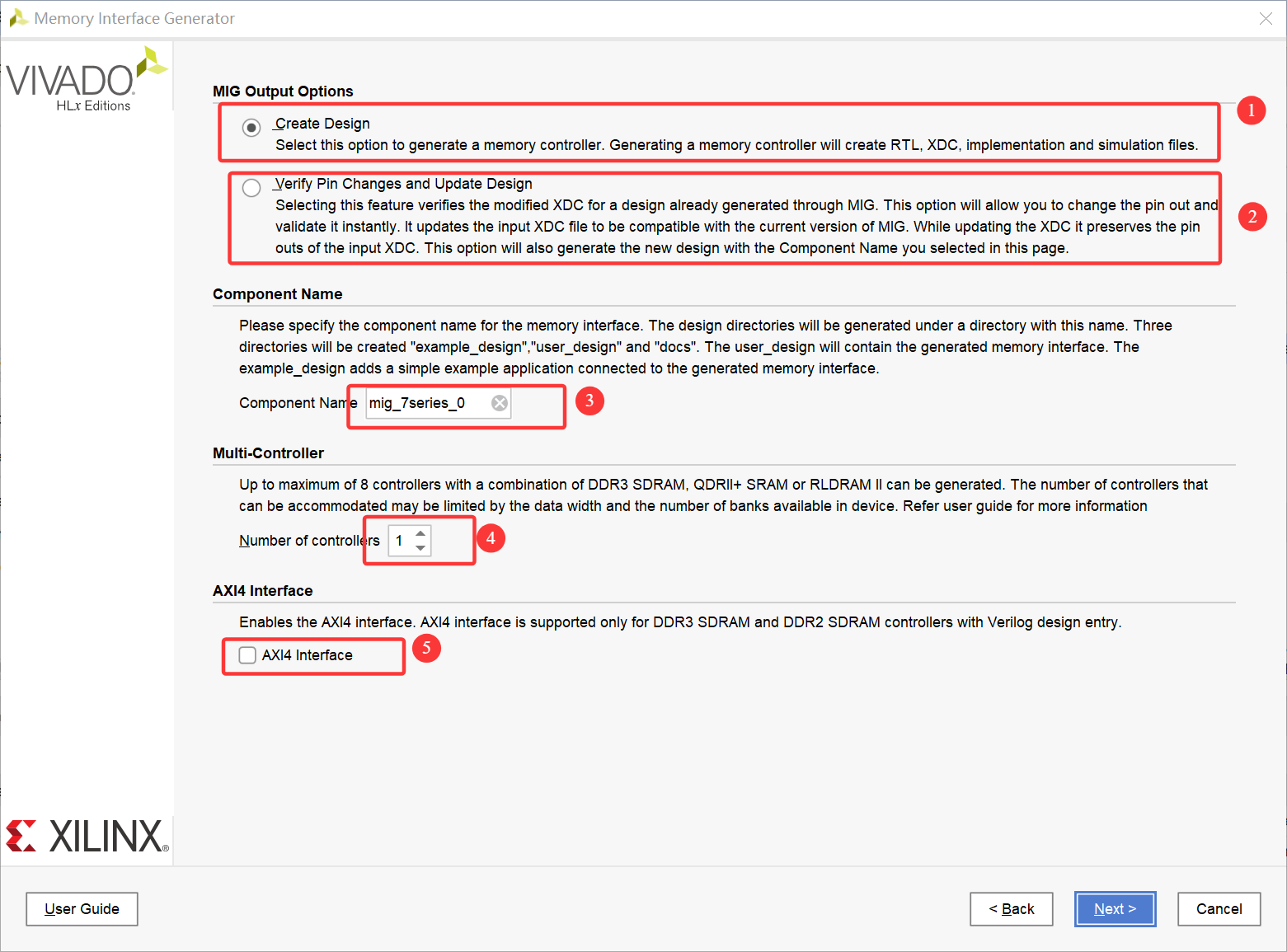

进入另一个页面

- 创建一个IP工程设计,本设计勾选此项

- 对已有的工程的XDC进行验证

- IP生成的模块名

- 由于这个IP支持多个控制器,所以这里需要选择主控的数量,FPGA使用的话一般只会存在一个,此处默认

- 此IP有两个接口默认比较适合内部使用,如果勾选会使用AXI总线。本设计不勾选

|

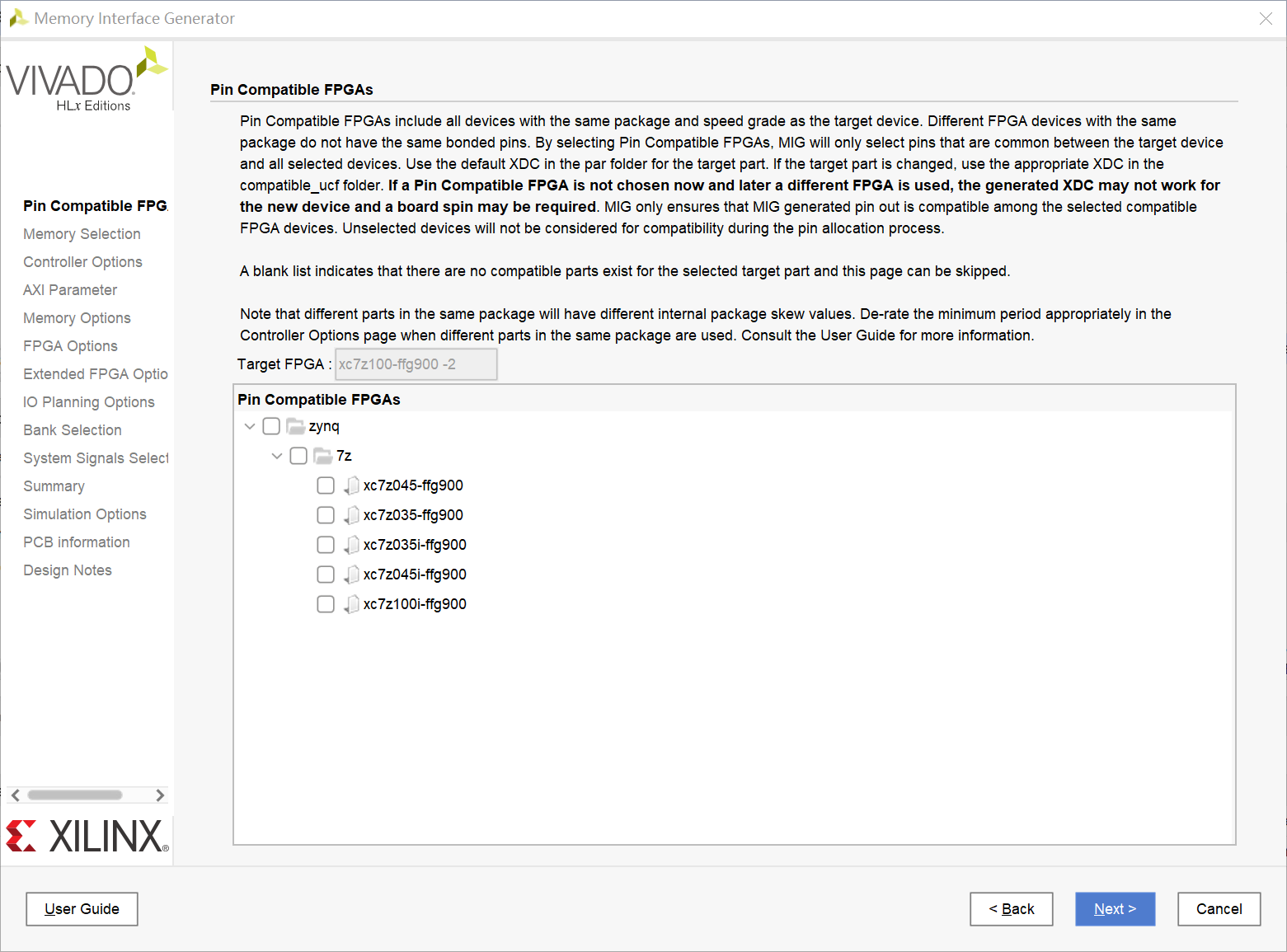

到FPGAs配置界面,本设计保持默认

|

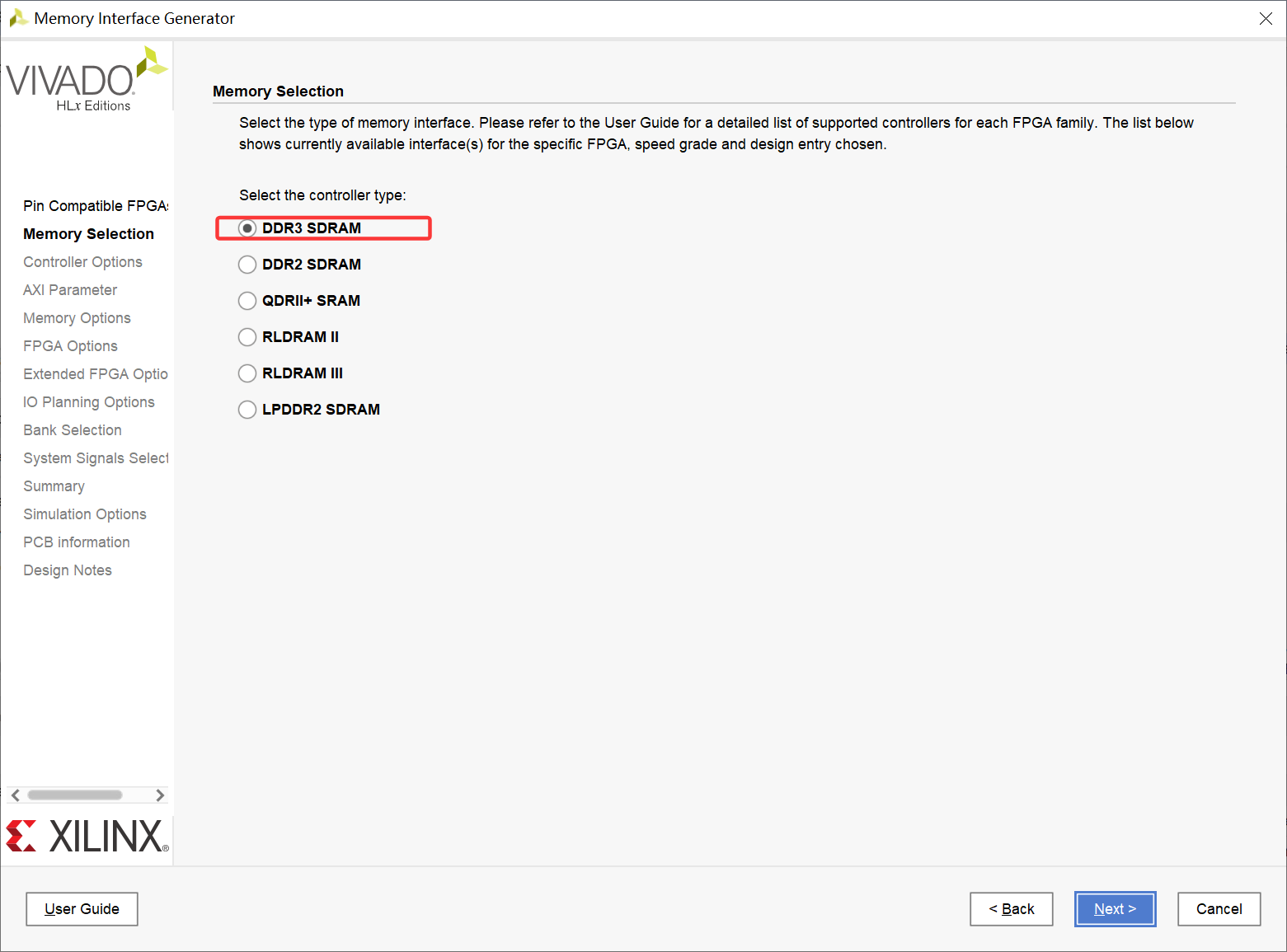

Memory Selection配置页面,此ip可以控制多种器件,因为本次设计是DDR3实验,所以选择DDR3 SDRAM

|

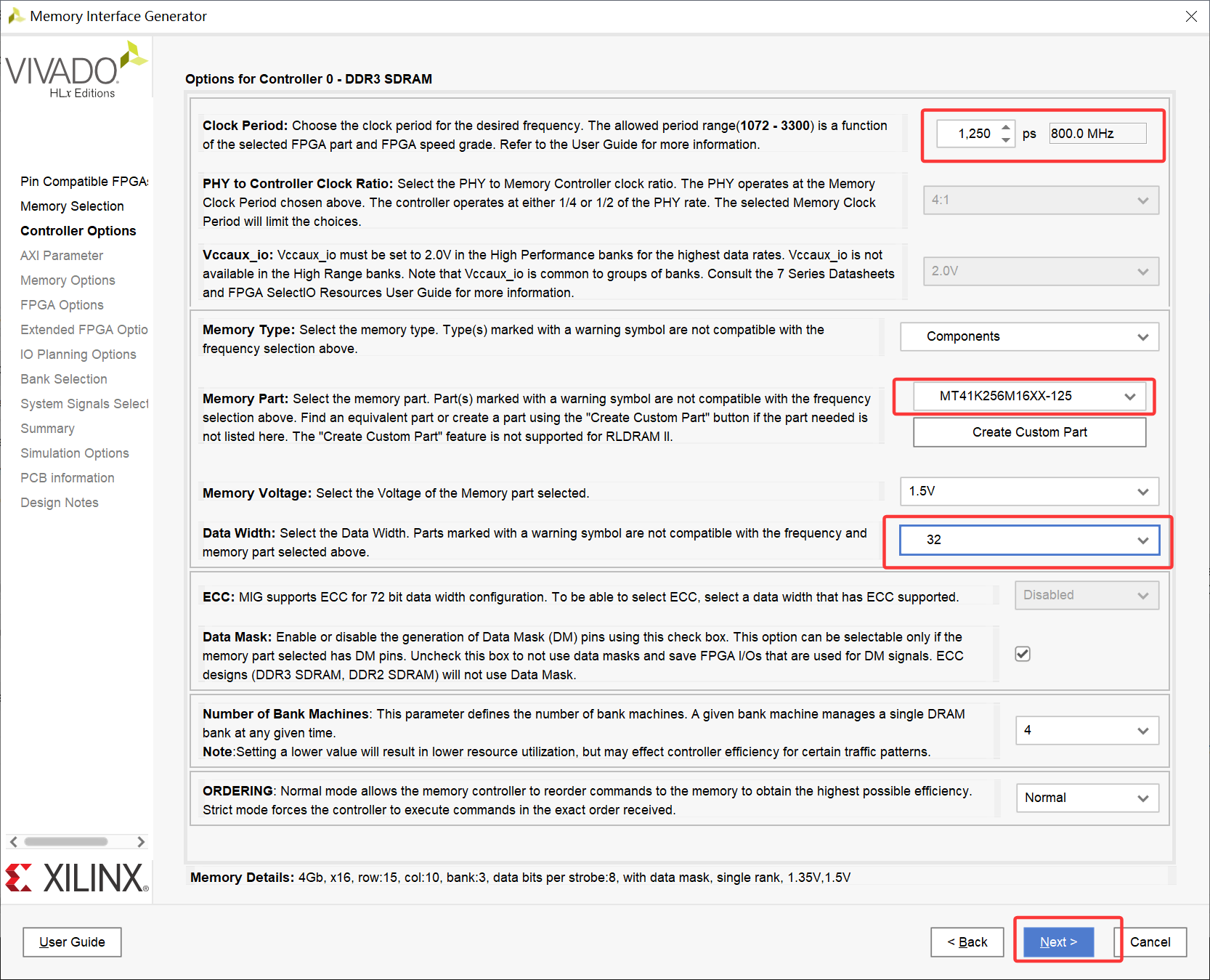

Controller Options配置页面

因为我们的开发板使用的是MT41K256M16RE-125,所以此处选择800MHZ,选择DDR类型,我们选择MT41K256M16XX-125,DDR3的数据位宽,根据原理图得到,一般是QDxx,最大数值加一,我们选择32

|

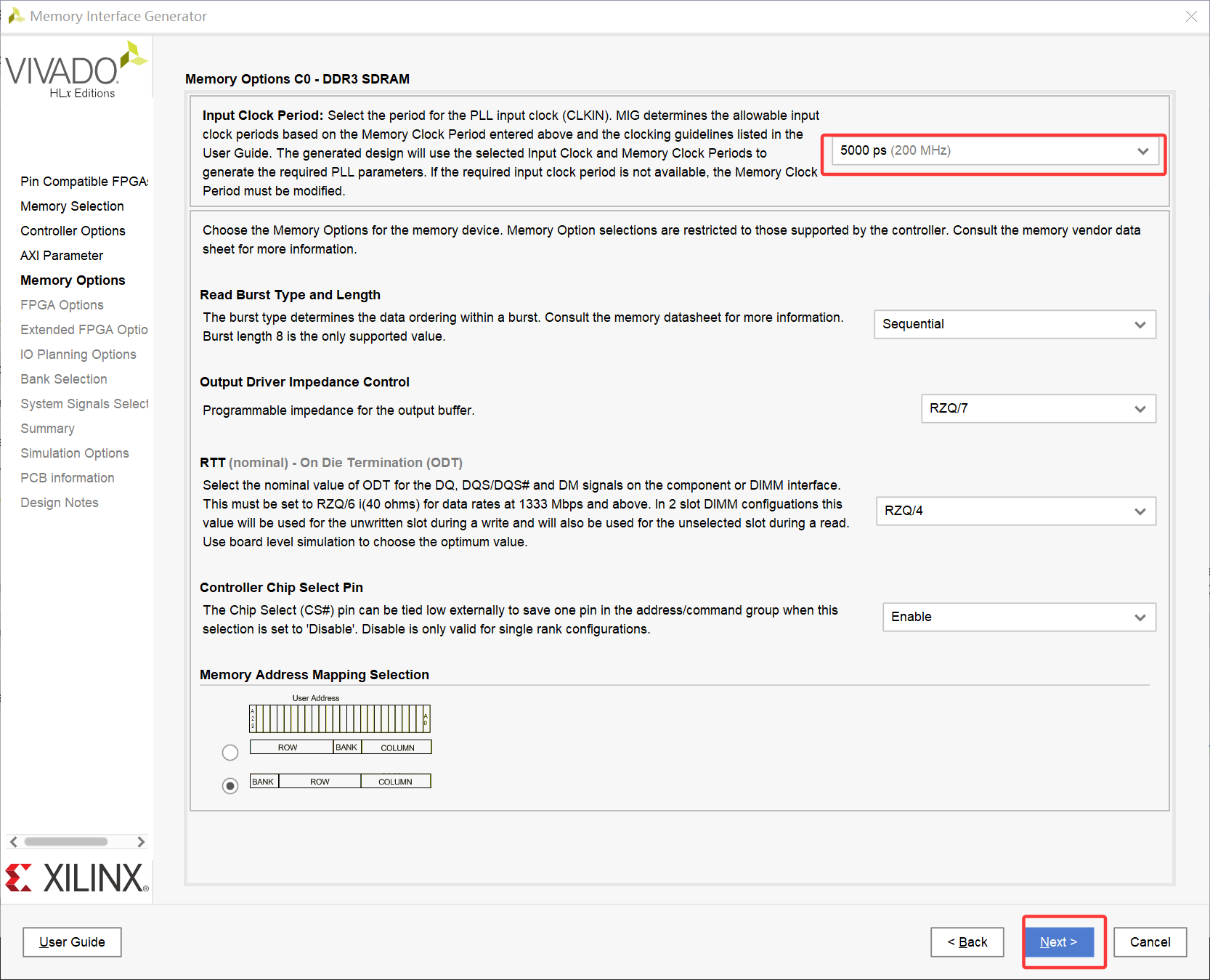

Memory Options配置页面,Input Clock Period我们选择200MHZ,这是系统时钟

|

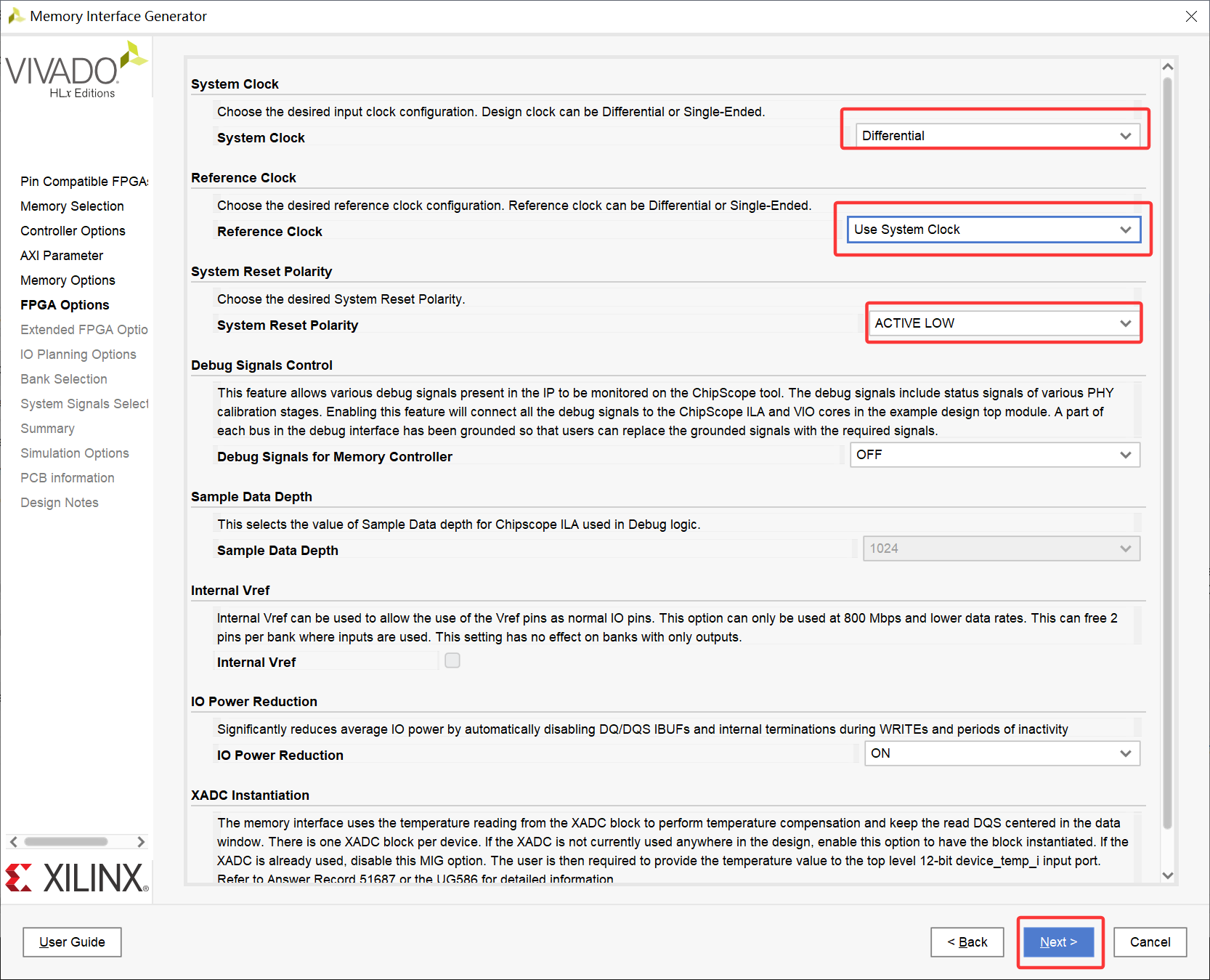

FPGA Options配置页面,系统时钟的来源,根据原理图选择差分信号(Differential),将参考时钟选择使用系统时钟(Use System Clock),系统复位低有效

|

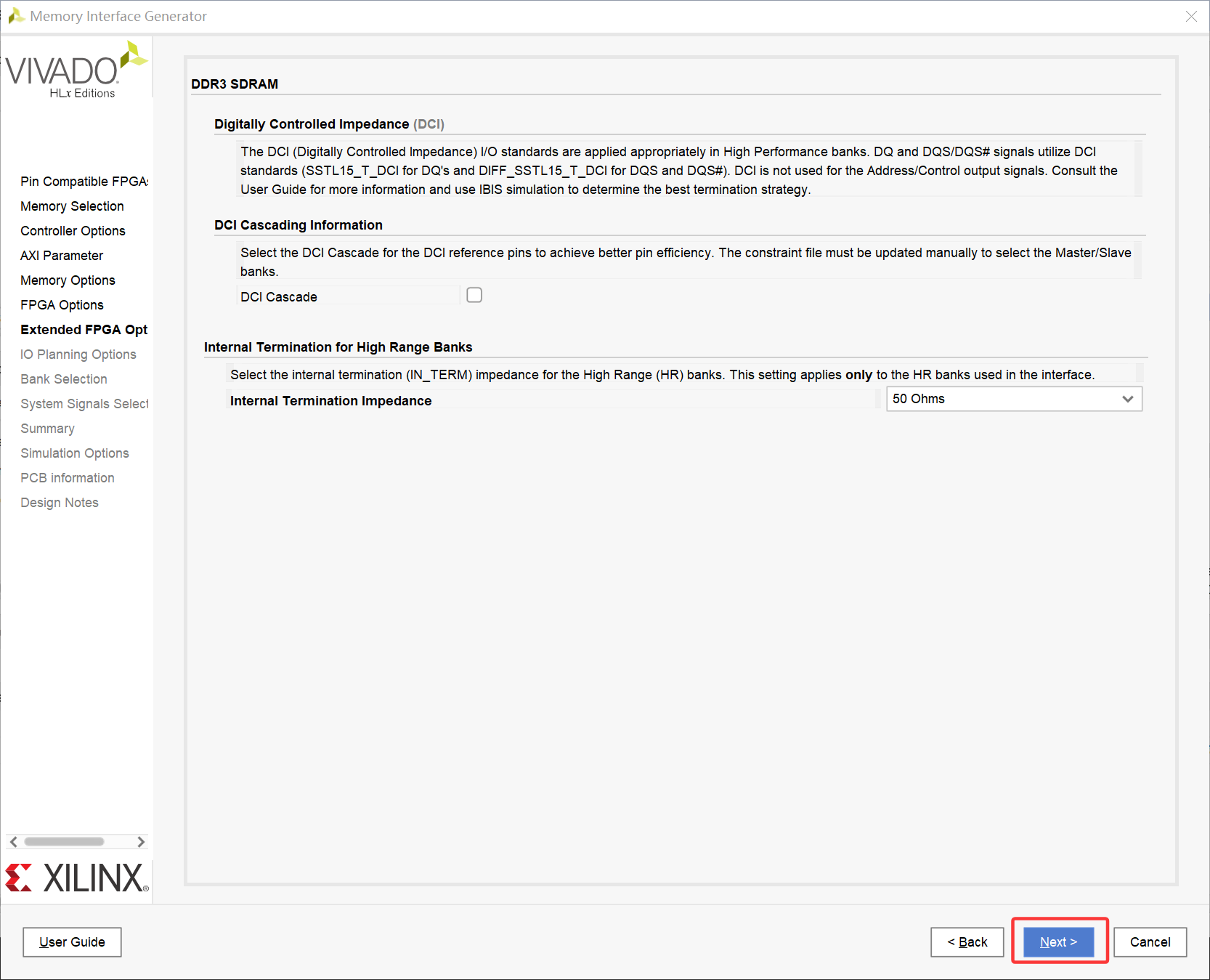

Extended FPGA Option 配置页面,此页默认,直接下一步

|

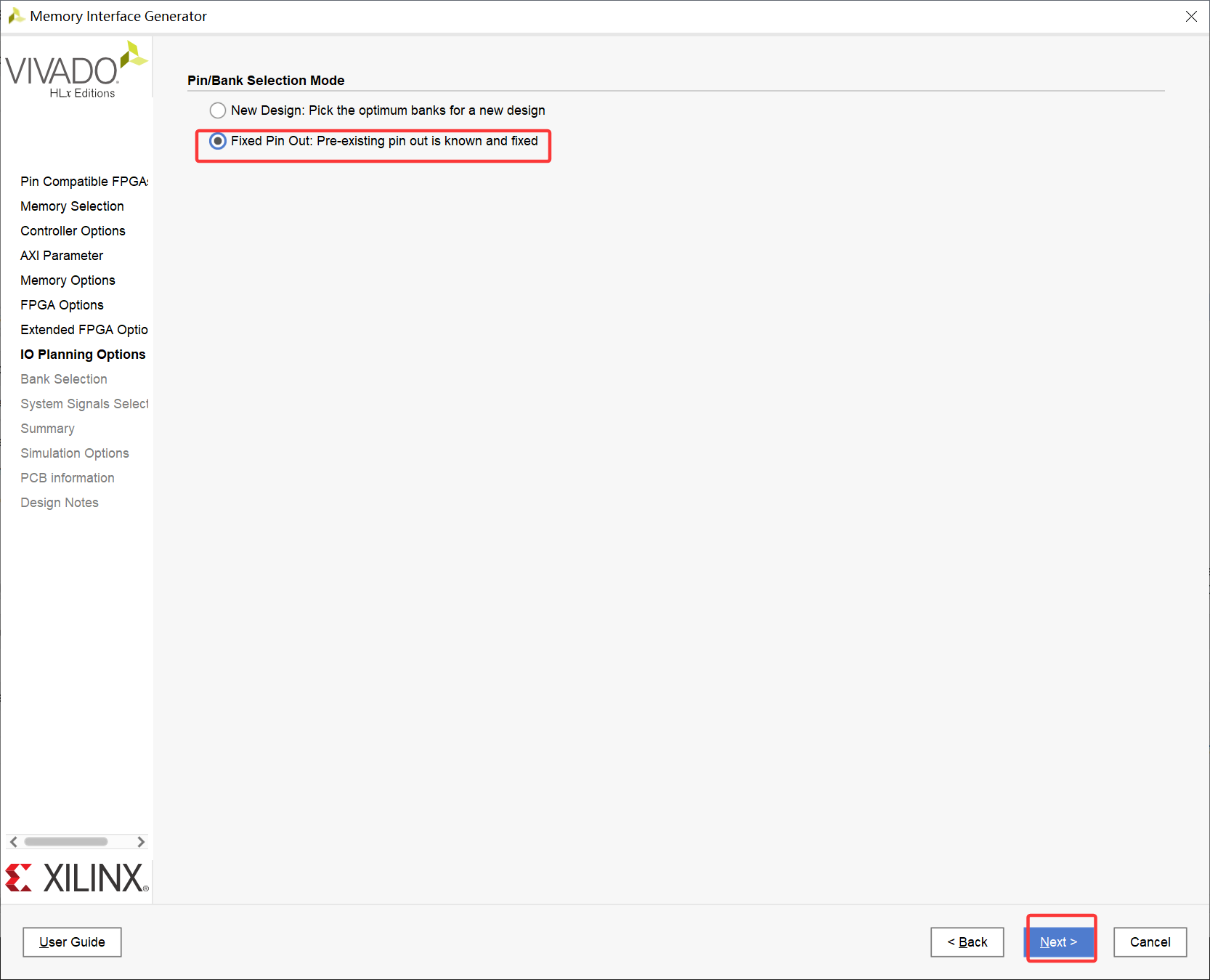

IO Planning Option配置页面,因为要上板实验所以选择“Fixed Pin Out: Pre-existing pin out is known and fixed”。

|

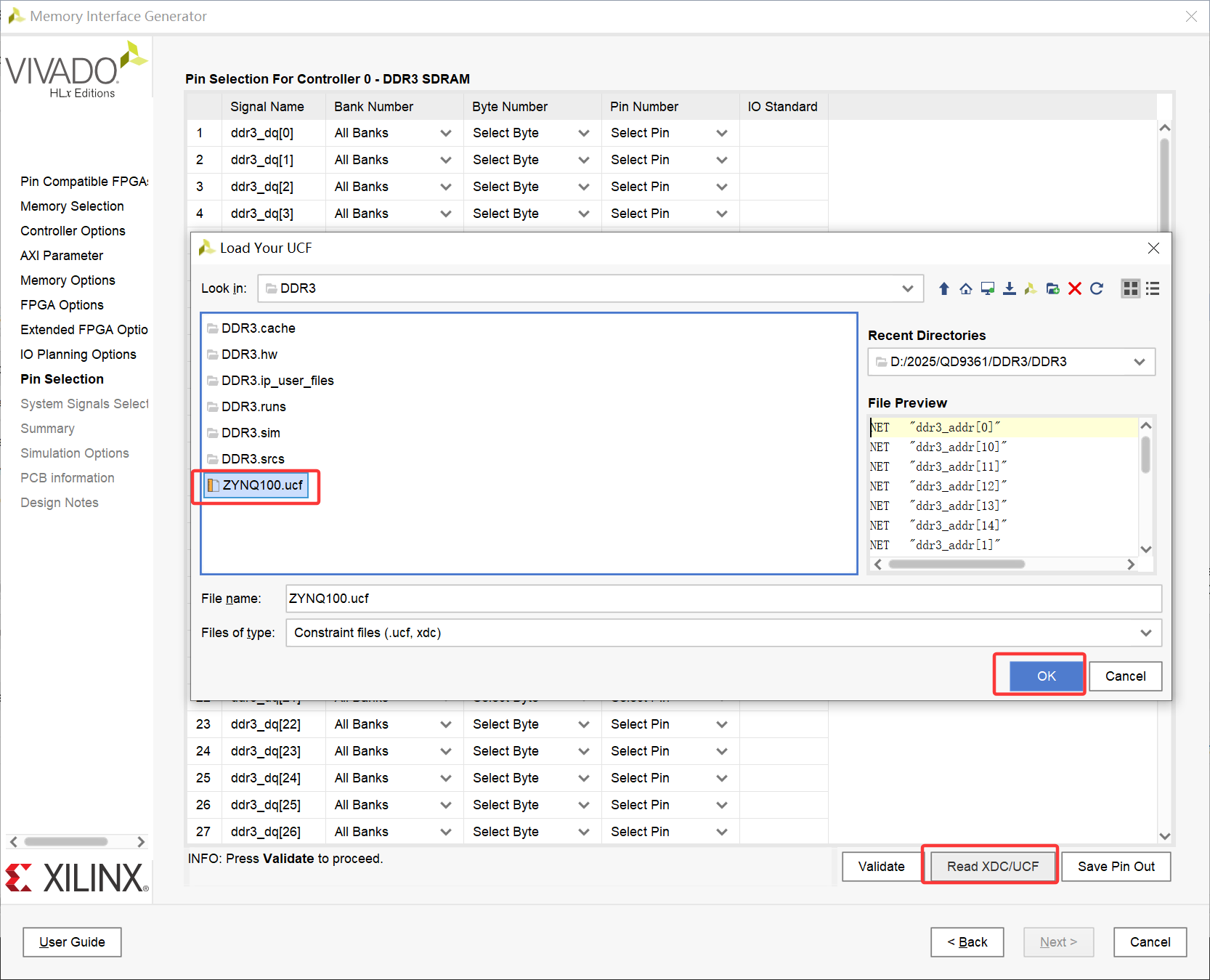

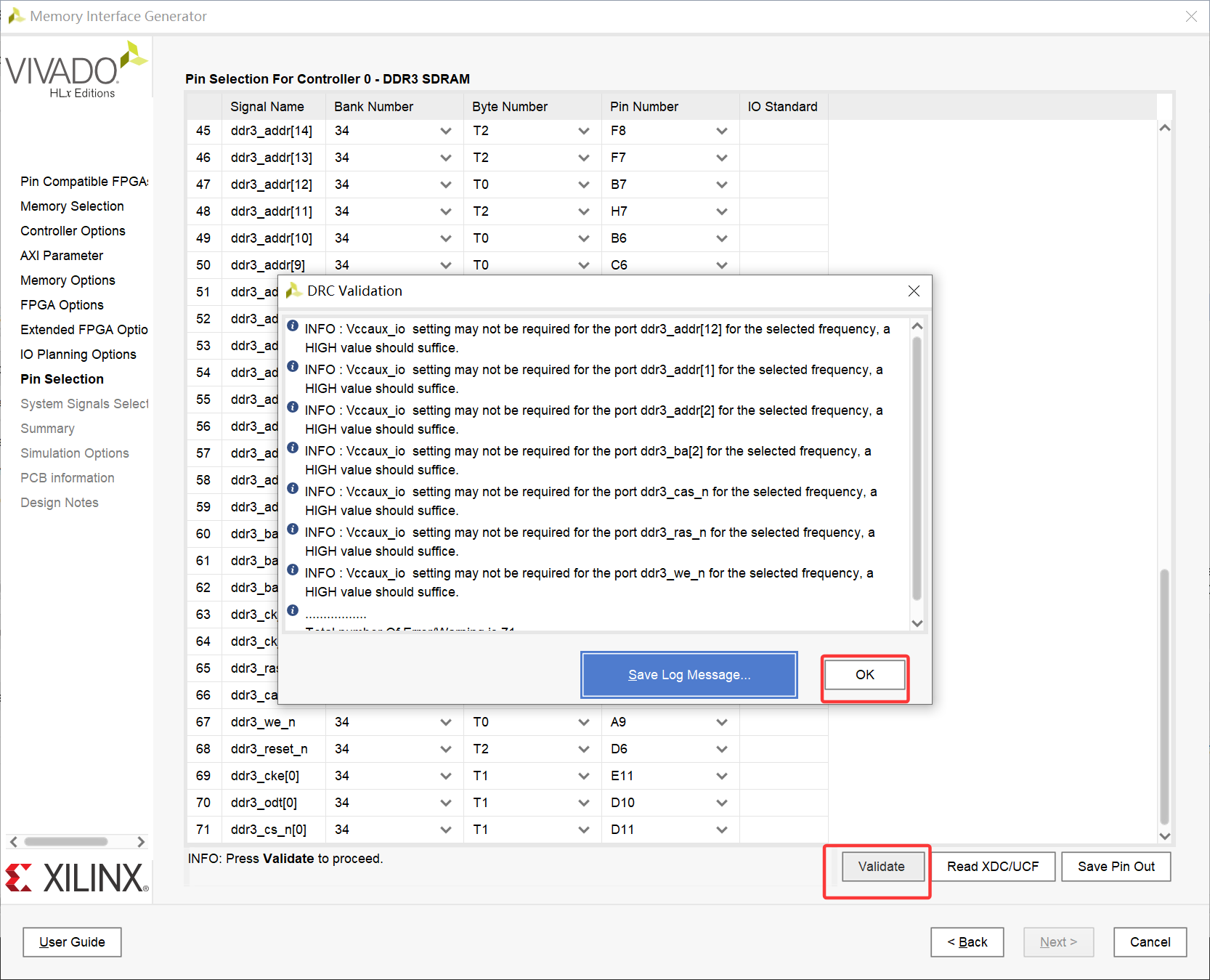

点击read XDC/UCF 根据原理图或者使用我们所提供的UCF文件,之后点击ok

|

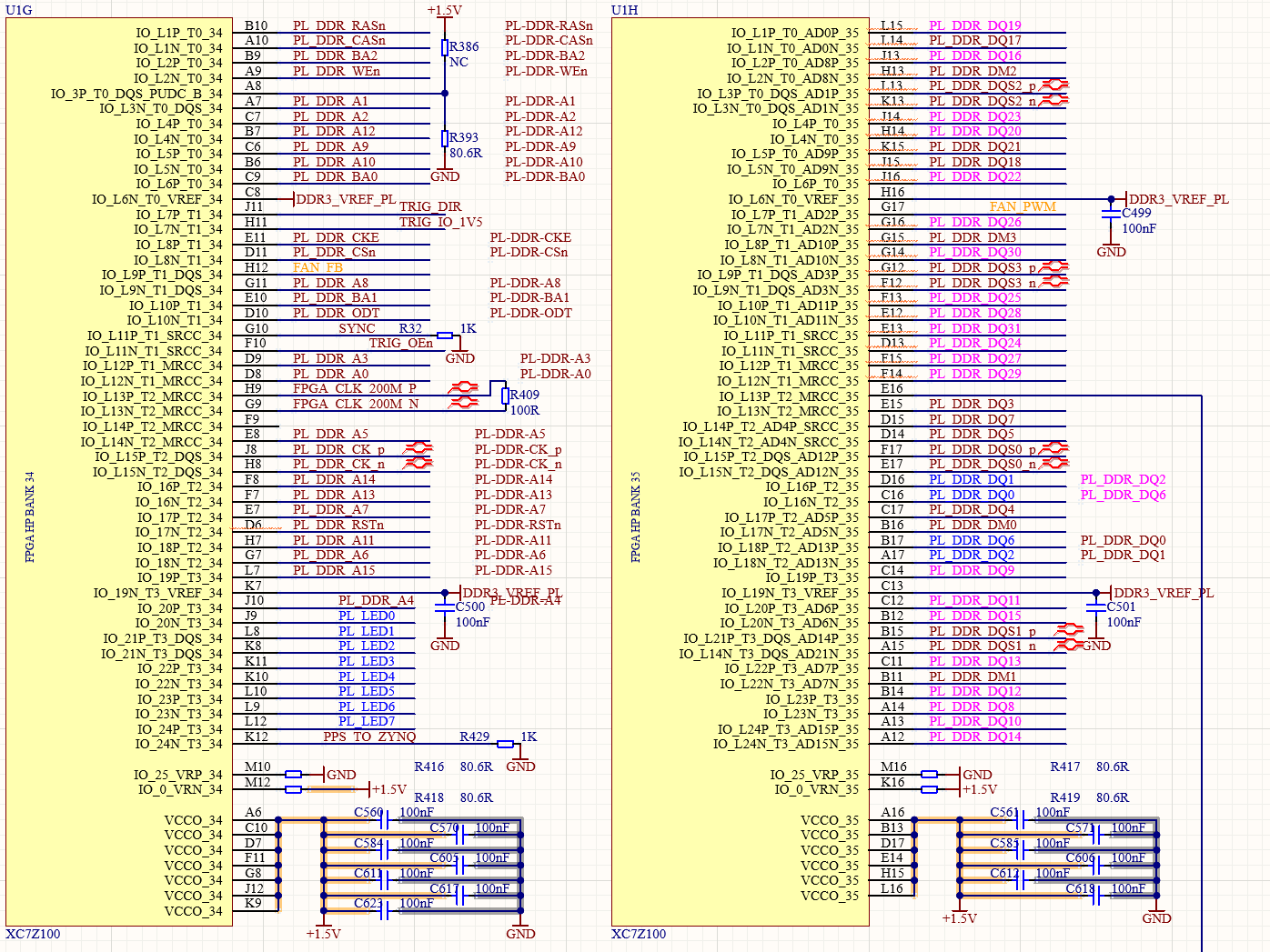

原理图

|

这时DDR3的引脚都已经绑定了,点击Validate。再点击ok,之后就直接下一步

|

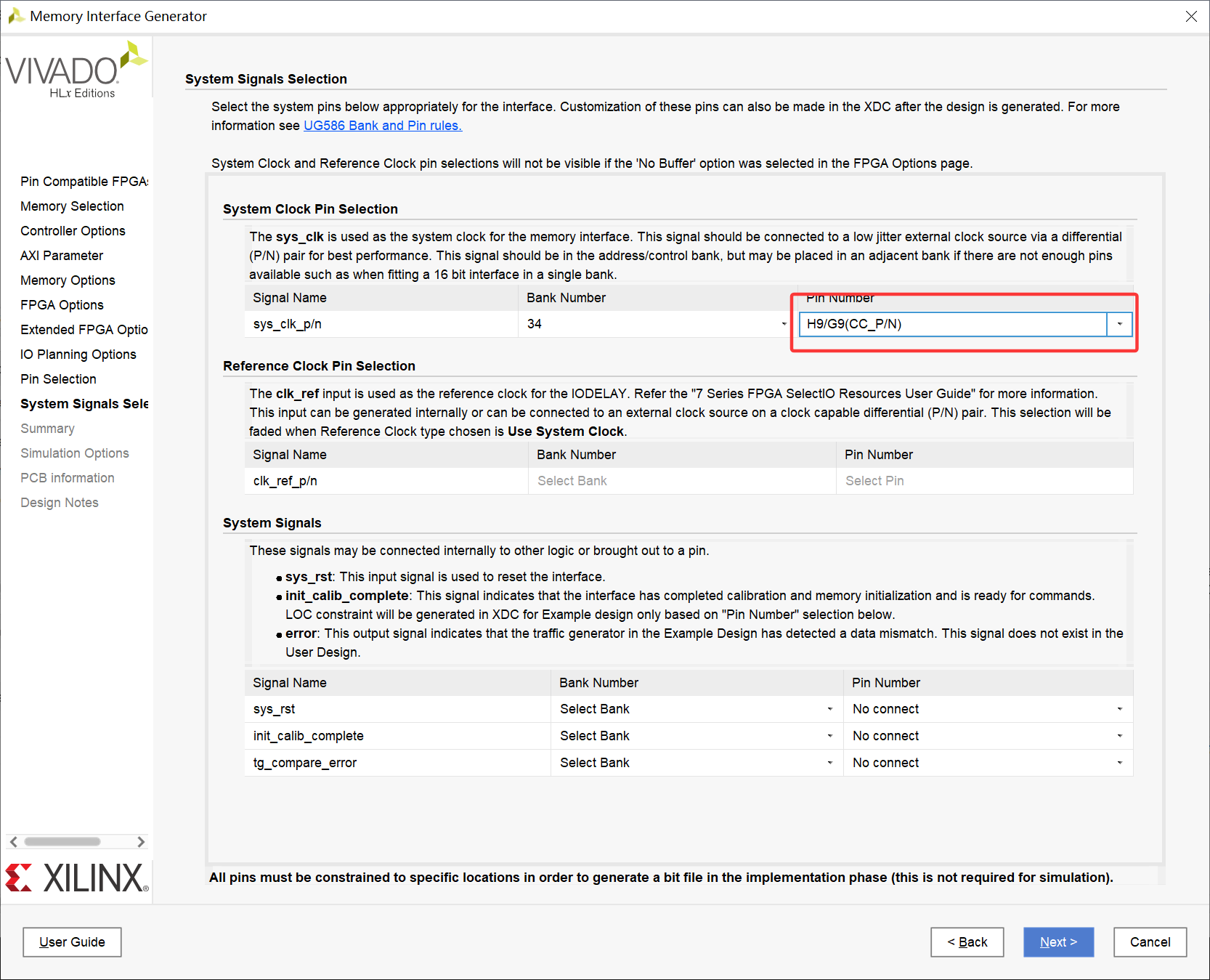

之后将系统时钟的引脚根据原理图选择引脚绑定,为H9/G9

|

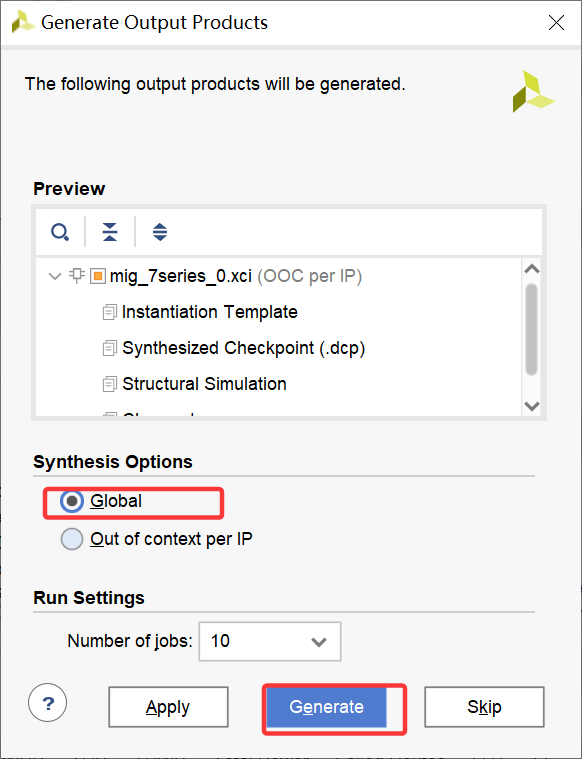

之后的所有页面就直接下一步就可以。直到创建完成,出现此界面,勾选Global然后点击Generate,之后就等待IP创建完成

|

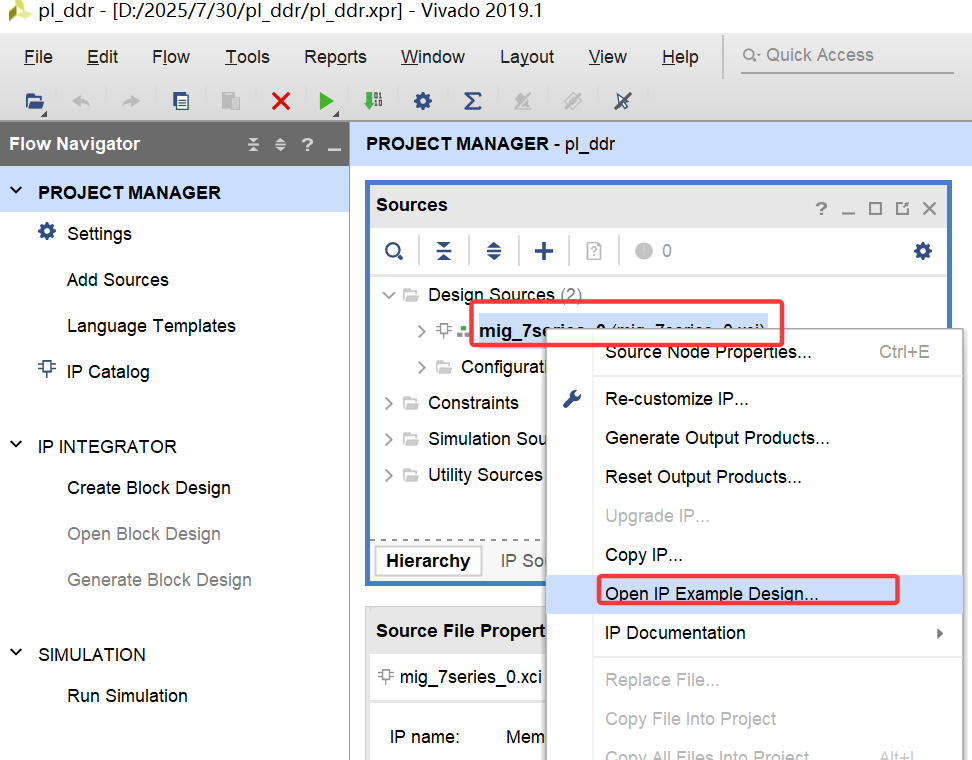

右键此IP核,之后选择Open IP Example Design

|

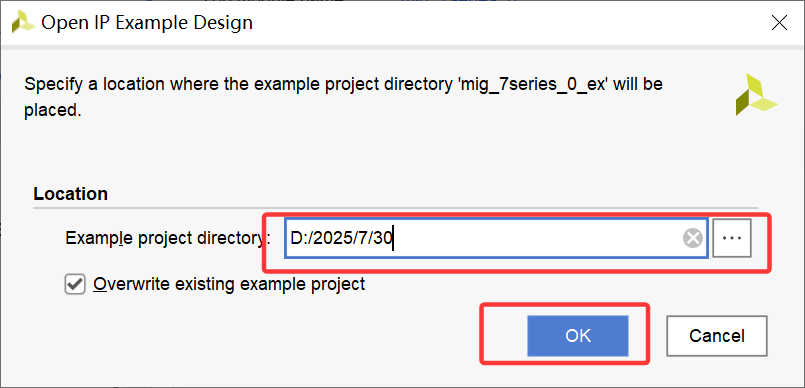

选择你想存放的位置,然后点击OK

|

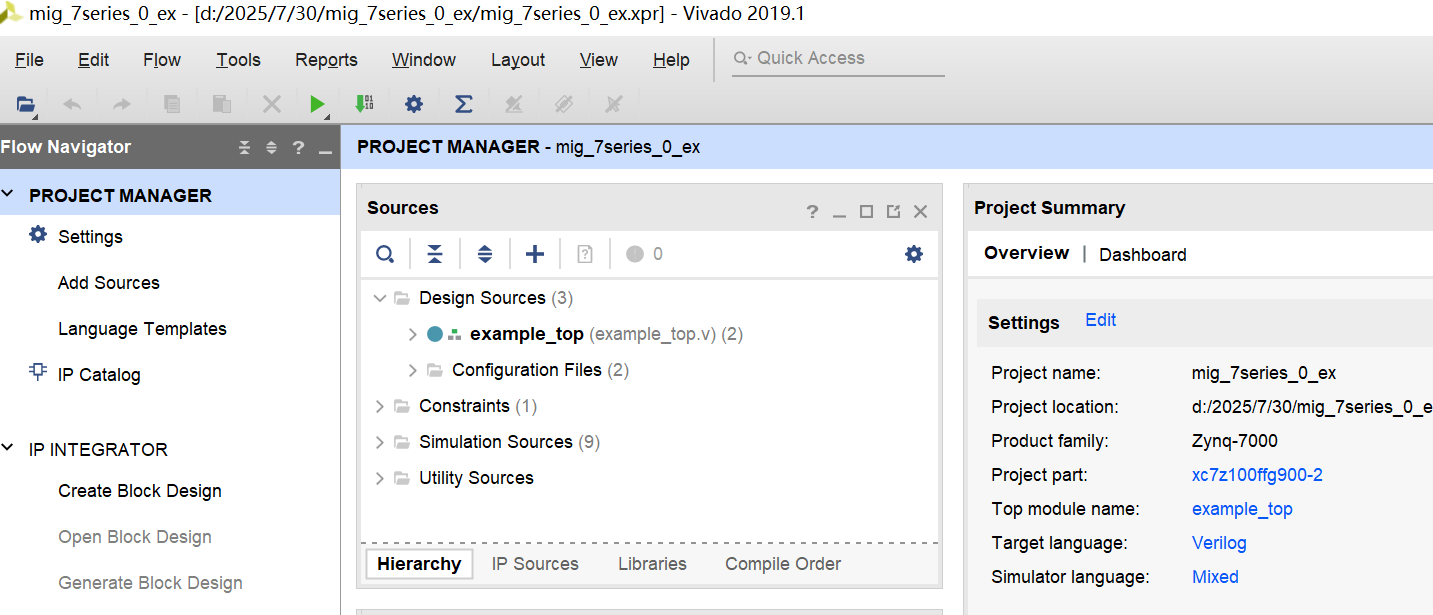

会重新打开一个vivado工程,这就是用mig IP重新生成的项目

|

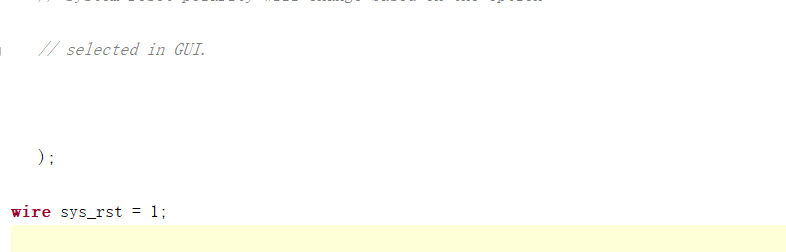

我们打开top层文件,找到系统复位(sys_rst)将他赋值为一

|

之后打开XDC文件进行引脚约束,将下面内容复制到XDC文件中,将init_calib_complete和 tg_compare_error都绑定到led上,这样可以看出是否运行成功

set_property PACKAGE_PIN J9 [get_ports tg_compare_error] set_property IOSTANDARD SSTL15_DCI [get_ports tg_compare_error] set_property PACKAGE_PIN L8 [get_ports init_calib_complete ] set_property IOSTANDARD SSTL15_DCI [get_ports init_calib_complete ] #LED1 set_property PACKAGE_PIN G9 [get_ports sys_clk_n] set_property IOSTANDARD LVDS [get_ports sys_clk_n] set_property PACKAGE_PIN H9 [get_ports sys_clk_p] set_property IOSTANDARD LVDS [get_ports sys_clk_p] |

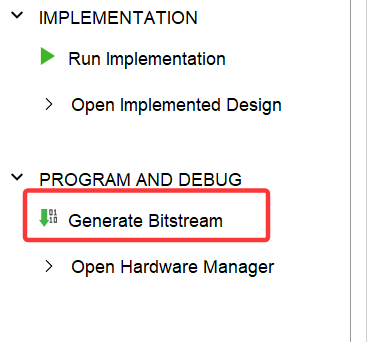

之后直接生成bit流文件

|

直接上板测试,当DS2灯亮时就代表测试通过。