Chrontel【CH7219A-BF】CH7219A USB-C和DP 1.4至HDMI 2.1协议转换器,带DSC解码功能

G通用 D描述

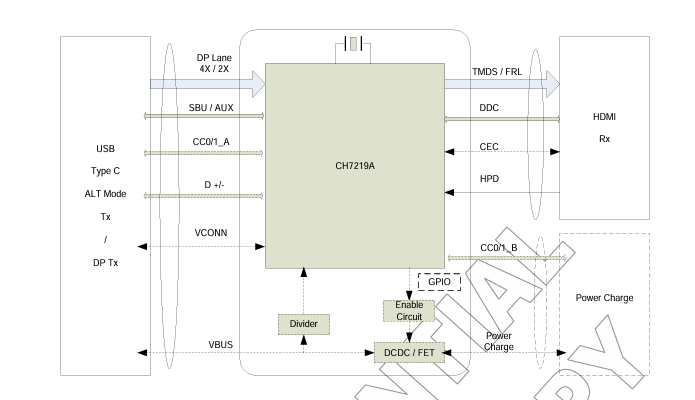

Chrontel 的 CH7219A 是一种低成本、低功耗的半导体器件 通过 USB Type-C 将 DisplayPort 信号转换为 HDMI 2.0 连接器。这款基于 USB Type-C 的创新型 DisplayPort 接收器具有高 高性能DSC解码器,集成HDMI 2.0发射器 专为 USB Type-C 转 HDMI 2.0 转换器、采用器和扩展坞而设计 装置。通过CH7219A先进的解码/编码算法, 输入DisplayPort高速串行多媒体数据可无缝衔接 转换为 HDMI/DVI 输出。

CH7219A的 DP 接收器符合 DisplayPort 规范 1.4 和嵌入式 DisplayPort (eDP) 规范版本 1.4。具有复杂的 DisplayPort 信号检测功能 和 Lane Swap/AUX 极性反转逻辑,CH7219A支持 USB Type-C电缆插头方向开关。集成了内部 HDCP 键,因此 设备支持 HDCP 1.4 和 2.3 规范。在设备的接收器中 块,支持四个具有数据速率的 DisplayPort 主链路通道输入 以 1.62Gbps、2.7Gbps、5.4Gbps 或 8.1Gbps 运行,并将输入转换为 信号转HDMI输出高达4K2K@60Hz。利用 USB 供电 控制逻辑、USB广告牌模块用于USB设备识别和 DisplayPort 的 Link Training 例程,CH7219A 能够立即 初始化时将视频显示调至 HDMI 2.0 电视/显示器 过程完成。

该CH7219A还支持多达 8 通道 来自 DP Rx 的音频输入和来自 HDMI Tx 的输出,采样率高达 192 KHz。可用音频带宽取决于像素时钟频率, 视频格式定时,以及内容保护是否重新同步 是需要的。

CH7219A与CH7217A引脚兼容。 凭借先进的 MCU 和片上闪存,CH7219A支持自动启动和 EDID 缓冲区。利用从嵌入式ROM自动加载的固件, CH7219A可以支持 DP 输入检测、HDMI 连接检测和 确定自动进入省电模式。

特征

1. VESA 显示端口 规范版本 1.4a

2. HDMI发射器支持 HDMI 规范 2.0 版

3. HDCP 1.4 和 HDCP 2.3 标准

4.支持HDCP中继器模式

5. 高动态范围 (HDR) 合并静态元数据

6. DTV配置文件未压缩高 速度数字接口 CTA-861-G

7. DSC标准v1.2a解码 能够

8. 视频色彩空间,包括 RGB 在 6/8/10/12 bpc,YCbCr4:4:4 和 YCbCr4:2:2 /4:2:0 在 8/10/12 bpc

9. RGB 转 YCC 4:4:4/4:2:2/4:2:0 实现 YCC 4:4:4/4:2:2 到 YCC 4:2:0 色彩空间转换

10. 数字音频支持多达 8 声道 LPCM(16/20/24 位),具有 采样率高达 192kHz,压缩音频格式(AC3、DTS、DTS-HD MA 和 杜比 MAT)、帧速率高达 1536kHz 的 HBR 音频格式和 3D 音频 采样率高达 192kHz 的格式

11. USB Type-C DisplayPort Alt-Mode 转 HDMI 2.0 协议转换器 准备

12. 集成 Ra、Rd 和 Rp 电阻器,用于 DFP/UFP 识别 连接

13. Type-C SBU 和 DisplayPort AUX 通道无缝切换

14. CC 通信上的 USB Power Delivery 3.1

15. 集成快速VBUS电压检测模块,支持FRS和 直通充电功能

16. 内置 USB Billboard Class 和 USB 2.0 PHY 支持 DisplayPort Alt 模式

17. 嵌入式微控制器、ROM 和 EDID 缓冲器

18. 通过 Chrontel 专有技术进行固件更新

19. 可配置的省电模式和低待机电流

20. 符合 RoHS 标准和无卤素封装

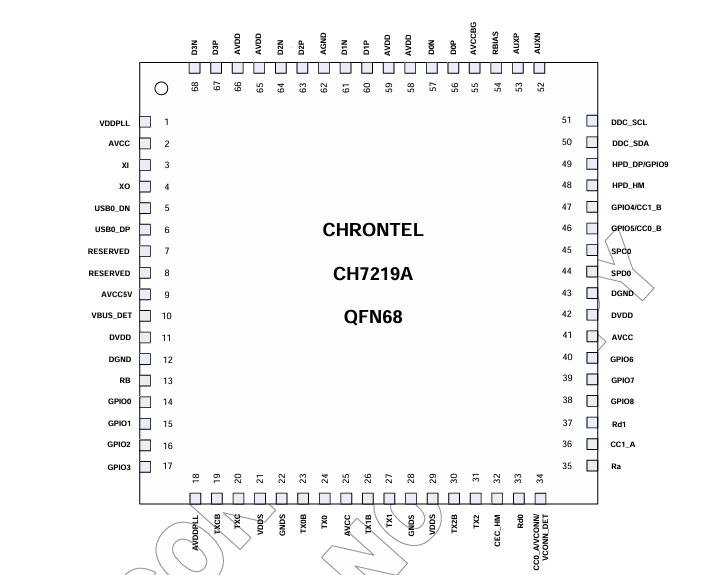

21. 采用 68 引脚 QFN 封装

上游 ( USB-C / DP )

1. 符合 USB Type-C 端口 带 USB Type-C 电缆和连接器规范修订版 2.0

2. 符合 USB PD 3.1 标准

3. 符合 DisplayPort 标准 USB Type C 标准上的备用模式

4. 符合VESA DisplayPort 规范 1.4 版和嵌入式 DisplayPort (eDP) 规范版本 1.4

本文档讨论了组件放置、电源去耦、接地、输入/输出信号接口的指导原则。本文档中讨论的内容和图示基于CH7219的68引脚QFN(8x8毫米)封装。

2.0 组件放置与设计考虑

与CH7219相关的组件应尽可能靠近相应的引脚。以下将描述如何连接关键引脚的指南,以及这些引脚相关组件的放置和布局指南。

2.1 电源去耦

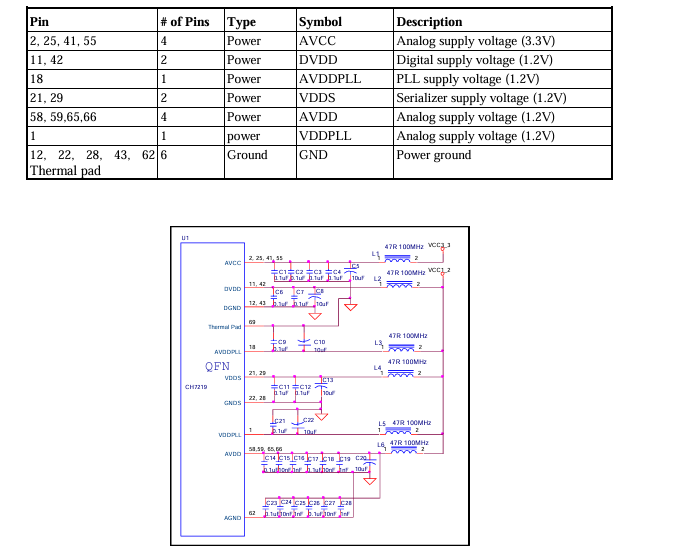

最佳的电源去耦是通过在每个电源引脚上放置陶瓷电容器来实现的,如图1所示。这些电容器(C1, C2, C3, C4, C6, C7, C9, C11, C12, C14, C15, C16, C17, C18, C19, C21, C23, C24, C25, C26, C27和C28)应尽可能靠近其各自的电源和地引脚,使用短而宽的走线以最小化引线电感。如果可能,在去耦电容器的地引脚和CH7219的地引脚之间应使用物理连接走线,此外还应使用地过孔。

2.1.1 地引脚

CH7219应连接到一个公共地平面,以提供低阻抗的回流路径。如果可能,每个CH7219地引脚应直接连接到其相应的去耦电容器地引脚,然后通过地过孔连接到地平面。应使用短而宽的走线以最小化引线电感。参见表1获取地引脚分配。

2.1.2 电源引脚

有十二个电源引脚:AVCC, DVDD, AVDDPLL, VDDS, AVDD和VDDPLL。参见表1获取电源引脚分配。参见图1获取电源去耦。