利用软件定义无线USRP X410、X440 电推进无线原型设计

概述

随着无线设备的应用日益增多,其需求和设计的复杂性也随之增加。对更多数据的需求推动着硬件设计向更宽的带宽、更高的频率和更多的通道发展,而软件则肩负着提供更高灵活性和更短上市时间的重任。

无论是在实验室中开发新型无线技术原型,还是在实际环境中评估系统,软件无线电 (SDR)都能提供理想的解决方案,确保满足性能和设计目标。

本文介绍了 NI Ettus USRP X410及其应用。这款通用软件无线电外设 (USRP) 旨在满足商业通信和国防应用从研究到部署的最新先进无线需求。

内容

- 无线原型设计的演变

- 新一代软件无线电

- 一个开放平台,助您实现下一次创新

- 可扩展的射频硬件设计

- 概括

- 后续步骤

无线原型设计的演变

在无人机防御和信号情报等快速发展的应用中,更快的部署和快速适应的能力至关重要。需要具有强大射频和信号处理能力的商用现货 (COTS) 系统,但开放平台也必不可少,以便灵活地增强功能,从而领先于威胁。对于部署用例,小尺寸、轻重量和低功耗 (SWAP) SDR 可实现移动就绪的便携式解决方案。

商业无线通信测试平台和原型通常需要处理蜂窝和无线连接的多个频段和标准。为了跟上 5G 等新的无线标准,需要在性能强大的硬件上开发和测试软件 IP,以验证从新型编码方案到先进的多输入多输出 (MIMO) 系统等各种技术,而这些技术通常需要通过无线 (OTA) 原型设计进行验证。

新一代软件无线电

NI Ettus USRP X410 是 Ettus Research 和 NI 联合推出的新一代高性能 SDR 中的首款产品。它将 NI 和 Ettus Research 的优势融合到一个无线电中,支持常用的开源工具流程,包括 USRP 硬件驱动程序 (UHD) 和 GNU Radio,以及 LabVIEW 软件。NI Ettus USRP X410 基于 Xilinx Zynq UltraScale+ RFSoC 构建,配备高性能射频发射器和接收器硬件,可提供 NI 迄今为止最强大的 SDR。RFSoC 以嵌入式处理器和可编程 FPGA 技术为基础,并集成了数据转换器(ADC/DAC)。四核 Arm® 处理器支持独立运行(嵌入式模式)或主机模式,并可连接外部主机运行您的应用程序。

图 3. NI Ettus USRP X410 集成了硬件和软件,可帮助您设计高性能无线系统的原型。

一个开放平台,助您实现下一次创新

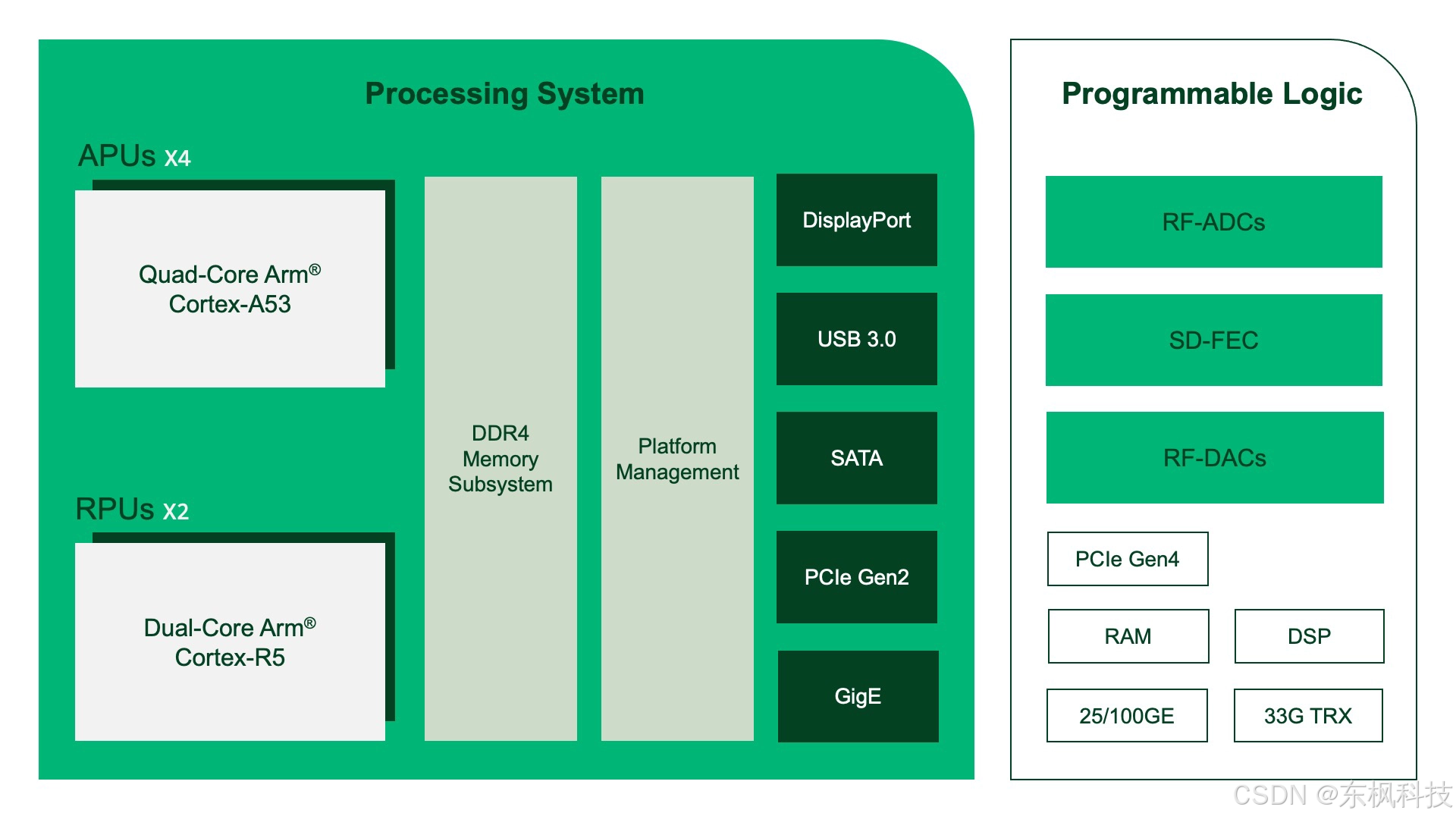

Xilinx Zynq UltraScale+ FPGA 的可编程逻辑部分拥有其他 USRP 产品两倍以上的 FPGA 资源,提供高吞吐量数字信号处理 (DSP) 和强化 IP 内核,例如板载软判决前向纠错 (SD-FEC) 和数字上/下变频 (DUC/DDC) 内核。SD-FEC 尤其适用于 5G 原型设计,可用于实时低密度奇偶校验 (LDPC) 编码/解码,这是 5G 中计算最密集的操作之一。在纯 FPGA 设计中,SD-FEC 逻辑可以跨越多个大型 Virtex-7 FPGA;因此,将其作为预制内核集成到硅片中可以节省大量空间和开发工作。NI

Ettus USRP X410 完全支持流行的射频片上网络 (RFNoC) 框架,使 FPGA 加速更容易通过软件应用程序编程接口 (API) 和 FPGA 基础架构实现。这可以帮助您快速启动并运行,从而专注于增值 IP。您可以使用 GNU Radio 图形界面、C++ 或 Python 将基于主机和 FPGA 的处理无缝集成到您的应用程序中。用于快速傅里叶变换 (FFT) 和有限脉冲响应 (FIR) 滤波器等常见功能的 RFNoC 模块库是一个不错的起点。然后,您可以使用您喜欢的硬件描述语言 (HDL) 将自己的 IP 模块添加到模块化架构中。

除了系统的 FPGA 结构部分外,Xilinx UltraScale+ RFSoC 还配备了四个板载应用处理单元 (APU) 和两个实时处理单元 (RPU),适用于需要板载嵌入式操作系统独立运行的应用。

图 4. Xilinx UltraScale+ RFSoC 的简化框图显示了需要板载嵌入式操作系统进行独立操作的应用程序的板载 APU 和 RPU。

可扩展的射频硬件设计

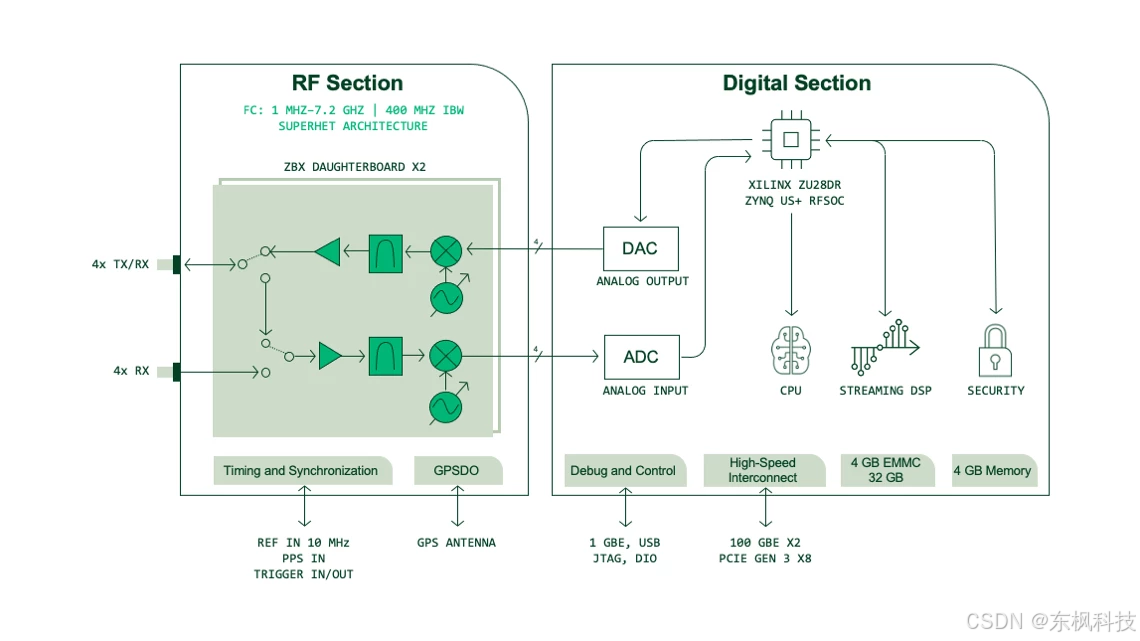

NI Ettus USRP X410 的频率范围覆盖 1 MHz 至 7.2 GHz,不仅涵盖传统的 6 GHz 以下 RF 频段,还涵盖最近开放的 5.925 GHz 至 7.125 GHz Wi-Fi 6E 免授权频段。凭借 400 MHz 的瞬时带宽,您可以利用更宽的信道,并实现信道绑定和载波聚合,从而实现更高的数据吞吐量。射频前端架构在 3 GHz 以下采用超外差两级变频,在 3 GHz 以上采用单级变频,并结合滤波和功率电平控制,可提供高保真信号的发送和接收。NI

Ettus USRP X410 将四个发送通道和四个接收通道集成到一个紧凑的 1/2 机架 1U 外形中,使其功能多样,易于运输,适合现场测试和操作。每个通道都是独立的,这意味着每个通道都可以调整到不同的频率,以用于频分双工 (FDD) 应用或同时仿真多个信号。通道还可以通过内部恒温晶体振荡器 (OCXO) 进行同步,您可以将其校准到 50 ppb 以内,使用内部 GPS 校准振荡器 (GPSDO) 进行时间戳,以及使用 10 MHz 参考和每秒脉冲 (PPS) 生成。对于更高的通道数,您可以通过导入外部参考时钟并使用 PPS 生成来同步多个设备,这些应用需要精确的时间对准,例如大规模 MIMO。

随着带宽增加和通道增多,在无线电上传输大量数据可能是一个挑战。为了解决这个问题,NI Ettus USRP X410 具有两个可配置的四通道小型可插拔 (QSFP) 端口,您可以使用它们来利用板载双 10 GbE 或双 100 GbE。此外,该无线电还包括一个 PCI Express x8 Gen 3 端口,传输速率高达 8 GB/s。

图5. NI Ettus USRP X410的框图显示了其RF和数字功能。

概括

NI Ettus USRP X410 性能强大,是您构建最新创新的理想平台。搭配您选择的软件工具链,这款软件无线电具备满足您需求的功能和灵活性。无论您是进行 5G 及更高技术的研究,还是部署系统以缓解日益严峻的威胁,NI Ettus USRP X410 都能加速您的无线设备原型开发。