STM32中SystemCoreClockUpdate函数解读

STM32中SystemCoreClockUpdate函数解读

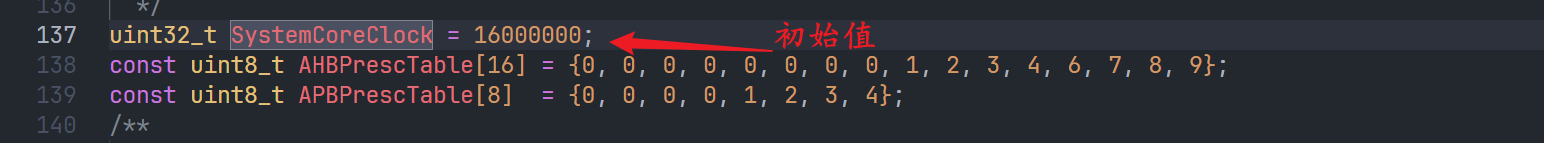

system_stm32f4xx.c file

SystemCoreClock是一个全局变量(uint32_t 类型), 存储当前系统的核心时钟频率(即HCLK, AHB 总线时钟).

每当系统时钟配置发生变化(如切换时钟源、调整 PLL 分频系数)后, 必须调用此函数重新计算 SystemCoreClock, 否则基于该变量的所有配置(如 SysTick、定时器)将会出错.

函数说明翻译

/*** @brief Update SystemCoreClock variable according to Clock Register Values.* The SystemCoreClock variable contains the core clock (HCLK), it can* be used by the user application to setup the SysTick timer or configure* other parameters.* 概要 根据时钟寄存器值更新SystemCoreClock变量.* SystemCoreClock变量包含内核时钟(HCLK), 可用于用户应用程序设置SysTick定时器或配置内核时钟.* * * @note Each time the core clock (HCLK) changes, this function must be called* to update SystemCoreClock variable value. Otherwise, any configuration* based on this variable will be incorrect. * * 注意 每次内核时钟(HCLK)发生变化时, 必须调用此函数以更新SystemCoreClock变量值, 否则任何基于该变量的配置都将是不正确的.** @note - The system frequency computed by this function is not the real * frequency in the chip. It is calculated based on the predefined * constant and the selected clock source:* * 注意 - 此函数计算的系统频率并非芯片中的真实频率, 它是根据预定义常数和所选时钟源计算得出的: ** - If SYSCLK source is HSI, SystemCoreClock will contain the HSI_VALUE(*)** - 如果SYSCLK源为HSI(内部高速时钟), SystemCoreClock将包含HSI_VALUE(*)* * - If SYSCLK source is HSE, SystemCoreClock will contain the HSE_VALUE(**)** - 如果SYSCLK源为HSE(外部高速时钟), SYstemCOreClock将包含HSE_VALUE(**)* * - If SYSCLK source is PLL, SystemCoreClock will contain the HSE_VALUE(**) * or HSI_VALUE(*) multiplied/divided by the PLL factors.* ** - 如果SYSCLK源为PLL(锁相环), SystemCoreClock将包含HSE_VALUE(**)或HSI_VALUE(**)乘以/除以PLL因子.* (*) HSI_VALUE is a constant defined in stm32f4xx_hal_conf.h file (default value* 16 MHz) but the real value may vary depending on the variations* in voltage and temperature. * * (*) HSI_VALUE时stm32f4xx_hal_conf.h文件中定义的常数 (默认值为 16MHz), 但实际值可能会因电压和温度的变化而变化.** (**) HSE_VALUE is a constant defined in stm32f4xx_hal_conf.h file (its value* depends on the application requirements), user has to ensure that HSE_VALUE* is same as the real frequency of the crystal used. Otherwise, this function* may have wrong result.** (**) HSE_VALUE是stm32f4xx_hal_conf.h文件中定义的常数 (其值取决于应用要求), 用户必须确保HSE_VALUE与所用晶体的实际频率相同, 否则该函数可能会产生错误结果* * - The result of this function could be not correct when using fractional* value for HSE crystal.* * - 当使用小数点后的HSE晶体值时, 该函数的结果可能不正确** @param None* @retval None*/

上述代码注释描述的是STM32 HAL库中的SystemCoreClockUpdate()函数, 其作用是根据当前时钟配置更新系统主频变量 systemCoreClock, 该参数至关重要, 提供整个系统的的时钟频率基准, 影响延时函数、定时器配置、通信波特率等关键参数计算.

SystemCoreClockUpdate函数

void SystemCoreClockUpdate(void)

{uint32_t tmp = 0, pllvco = 0, pllp = 2, pllsource = 0, pllm = 2;/* 确定 SYSCLK系统时钟来源 *//* Get SYSCLK source -------------------------------------------------------*/tmp = RCC->CFGR & RCC_CFGR_SWS;switch (tmp){/* 内部高速时钟 */case 0x00: /* HSI used as system clock source */SystemCoreClock = HSI_VALUE; break;/* 外部高速时钟 */case 0x04: /* HSE used as system clock source */SystemCoreClock = HSE_VALUE; break;/* 锁相环 */case 0x08: /* PLL used as system clock source *//* 计算PLL输出频率 *//* PLL_N 对分频后的时钟进行倍频 *//* PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_NSYSCLK = PLL_VCO / PLL_P*/ /* PLL输入源 */pllsource = (RCC->PLLCFGR & RCC_PLLCFGR_PLLSRC) >> 22;/* PLLM分频系数 对输入时钟进行分频 */pllm = RCC->PLLCFGR & RCC_PLLCFGR_PLLM;if (pllsource != 0){/* HSE used as PLL clock source */pllvco = (HSE_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> 6);}else{/* HSI used as PLL clock source */pllvco = (HSI_VALUE / pllm) * ((RCC->PLLCFGR & RCC_PLLCFGR_PLLN) >> 6);}/* PLLP分频系数 对PLL_VCO输出进行分频 */pllp = (((RCC->PLLCFGR & RCC_PLLCFGR_PLLP) >>16) + 1 ) *2;SystemCoreClock = pllvco/pllp;break;default:SystemCoreClock = HSI_VALUE;break;}/* 用用AHB预分频系统, 得到最终HCLK频率 *//* Compute HCLK frequency --------------------------------------------------*//* Get HCLK prescaler */tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> 4)];/* HCLK frequency */SystemCoreClock >>= tmp;

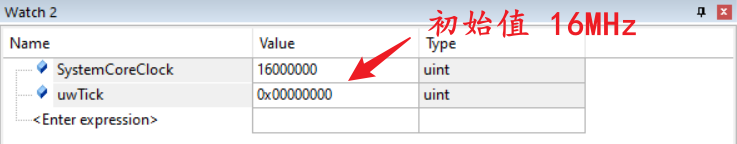

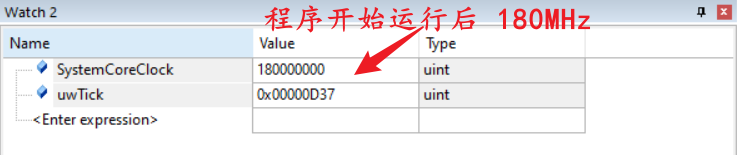

}可在调试过程中查看该全局变量的值

1. 初始值

2. debug调试

相关参考链接

STM32 SystemCoreClockUpdate()函数详解-CSDN博客