【CAN】01.CAN简介硬件电路

0&1.CAN简介&硬件电路

- 0.CAN简介

- 汽车内部CAN拓扑图

- 1.硬件电路

- 1.1 基本电路

- 一、所有CAN节点的通用硬件规则

- 二、高速CAN的专属规则(闭环总线)

- 三、低速CAN的特殊处理(开环总线)

- 四、总线物理特征必须牢记

- 五、终极重点:为什么能总线仲裁?

- 1.2 CAN电平标准

- 1. 高速 CAN 电平标准

- 2. 低速/容错 CAN 电平标准

- 1.3 CAN收发器-TJA1050(高速CAN)

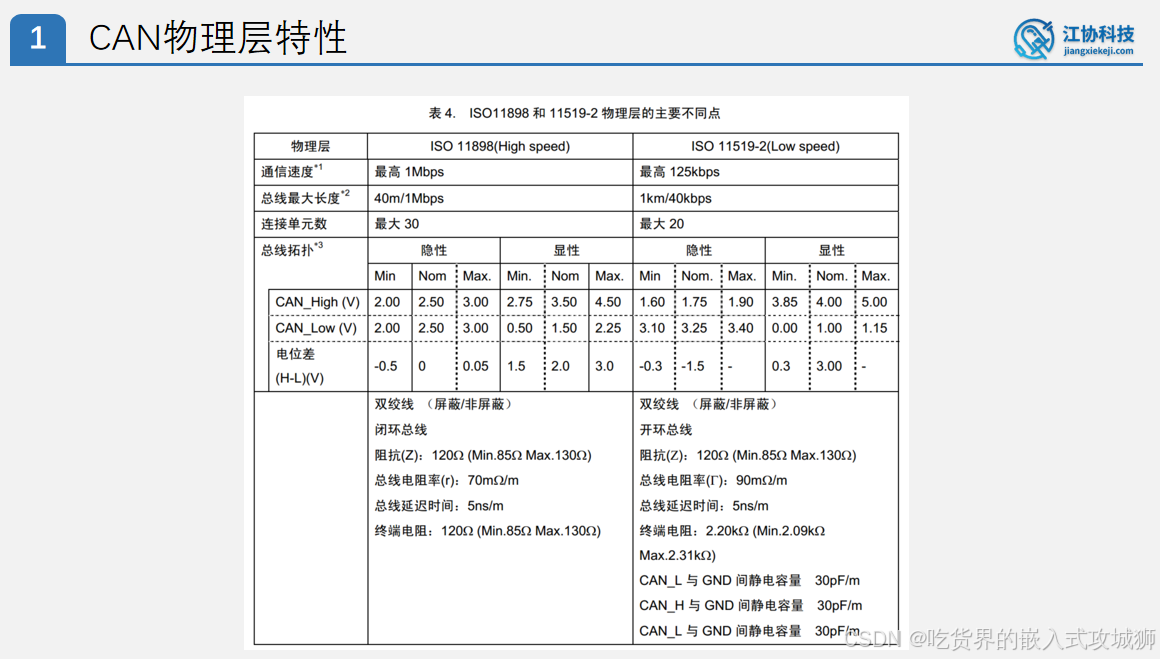

- 1.4 CAN物理层特性

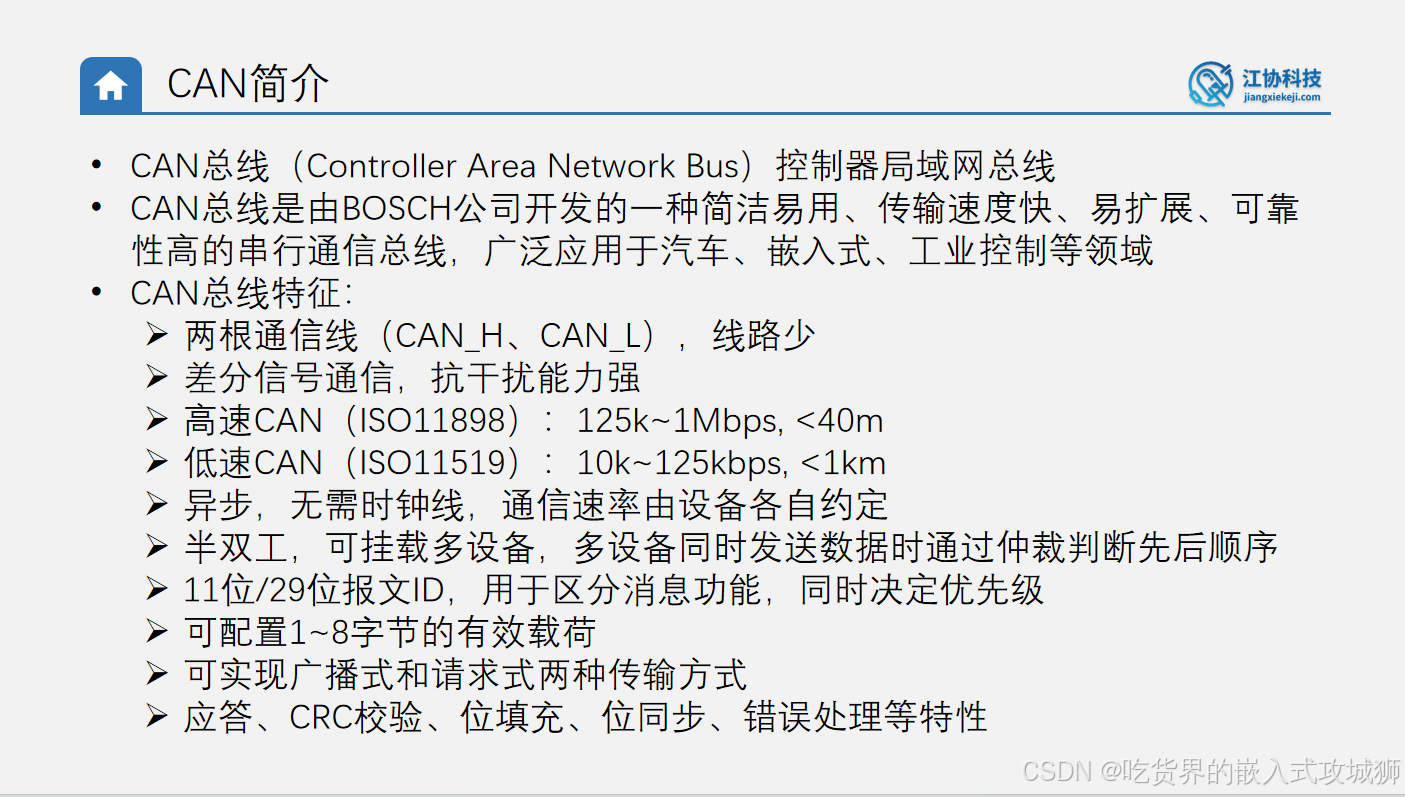

0.CAN简介

说明:

虽然差分信号各设备不共地可以使用,但是这可能会让收发器承受较高的共模电压。在实际应用中,为了安全和稳定,CAN通信一般还是会共地的共地,即,再额外使用一根线,把各设备的GND连接在一起。

此外,如果除了传递信号,还需要为设备传递供电电源。那么就需要再加一根电源正的线路CAN_H,CAN_L电,电源正,电源负(GND)这4根线一起构成完整的供电和通信线路。

广播式:一个设备发送,其他设备都能收到,接收方根据报文ID决定用不用这个数据

请求式:数据发送方不会主动广播自己的数据,只有接到接收方发出的请求,发送方才会发数据,这样一个数据的传输就需要先请求再接收两个过程

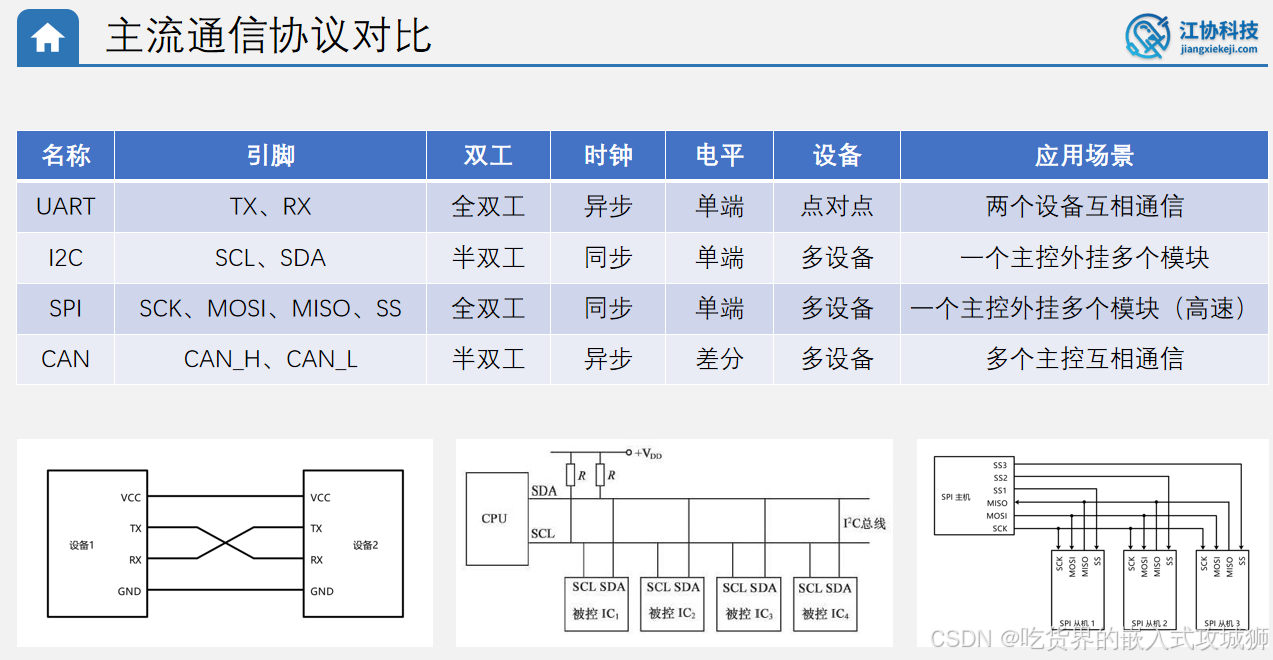

以下是UART、I2C、SPI和CAN协议的对比总结:

1. 基础特性对比

| 特性 | UART | I2C | SPI | CAN |

|---|---|---|---|---|

| 通信类型 | 异步(无时钟) | 同步(共享时钟) | 同步(共享时钟) | 异步(基于帧) |

| 全/半双工 | 全双工(独立收发线) | 半双工(单数据线) | 全双工(双数据线) | 半双工(差分总线) |

| 设备数量 | 点对点(仅2设备) | 多从设备(理论128+) | 多从设备(需片选线) | 多节点(多主架构) |

| 拓扑结构 | 点对点 | 总线型(共享SDA/SCL) | 总线型(带片选线) | 总线型(差分线) |

2. 硬件与传输细节

| 特性 | UART | I2C | SPI | CAN |

|---|---|---|---|---|

| 线数 | 2线(TX/RX) | 2线(SDA/SCL) | 3线+片选(SCK/MOSI/MISO) | 2线(CAN_H/CAN_L,差分信号) |

| 速率 | 低(通常≤115.2 kbps) | 标准模式:100 kbps 高速:3.4 Mbps | 高(可达数十Mbps) | 最高1 Mbps(线长↑则速率↓) |

| 寻址方式 | 无地址(点对点) | 7/10位从机地址 | 片选信号选中从机 | 消息ID标识符(11/29位) |

| 错误检测 | 奇偶校验(可选) | ACK/NACK机制 | 无原生校验(依赖应用层) | 强校验(CRC、ACK、帧检查) |

| 冲突处理 | 不适用(点对点) | 主设备控制无冲突 | 主设备选择从机 | 多主仲裁(ID优先级竞争) |

3. 应用场景

- UART:简单调试、短距离通信(如PC与单片机)。

- I2C:板内低速设备互联(传感器、EEPROM)。

- SPI:高速外设(显示屏、FLASH存储器)。

- CAN:高可靠性场景(汽车、工业控制)。

4. 优缺点总结

-

UART

- 优点:简单、全双工。

- 缺点:无多设备支持,速率低。

-

I2C

- 优点:多设备、少线数。

- 缺点:速率受限,需上拉电阻。

-

SPI

- 优点:高速、全双工。

- 缺点:线数多(设备增加时需更多片选线)。

-

CAN

- 优点:高可靠性、多主架构、长距离。

- 缺点:协议复杂,成本较高。

关键区别速记

- 速率:SPI > I2C > CAN(短距离)> UART

- 复杂度:CAN > I2C > SPI > UART

- 可靠性:CAN(带自动重传、错误检测) > 其他

- 设备扩展:CAN(多主)≈ I2C > SPI > UART(仅点对点)

实际选择需根据速度、设备数量、抗干扰需求等场景权衡。

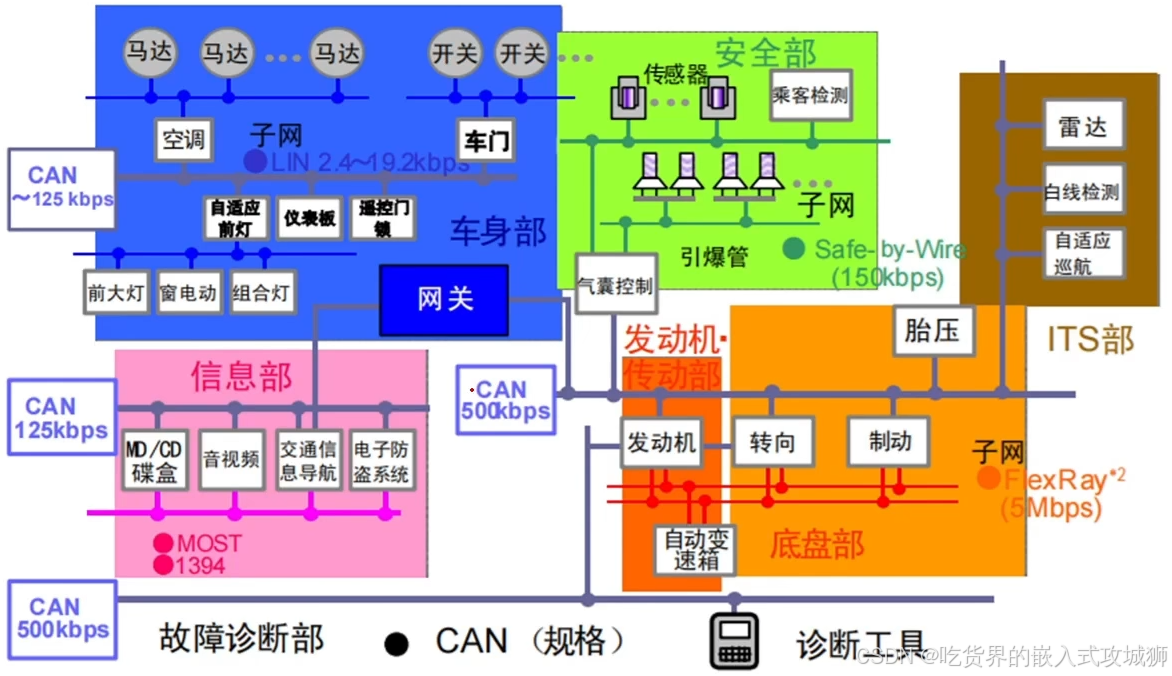

汽车内部CAN拓扑图

动力CAN网络

如图右下角,发动机,自动变速箱,底盘,转向,制动等实时性要求较高的部件,一般采用500kdps的CAN速率

车身CAN网络

与车身部分相关,网关也在其中,会将自适应灯,仪表板,空调,车门等部分接入CAN网络,其中有些部分的下属分支会采样LIN总线来控制下属模块。

组合仪表CAN网络

针对在汽车前端如驾驶室的组合仪表,需要接收到来自各个部件的CAN信息并显示在仪表上

诊断CAN网络

在对车身进行诊断时,也会单独接一路CAN总线出来

1.硬件电路

1.1 基本电路

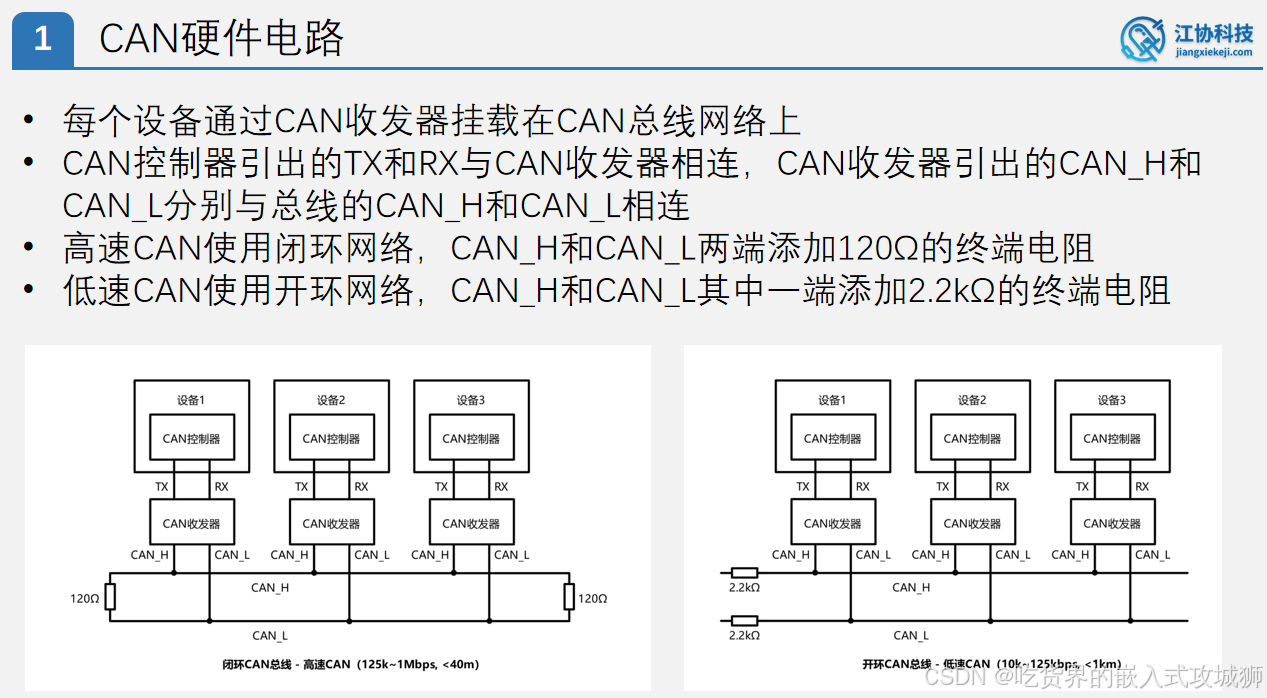

一、所有CAN节点的通用硬件规则

步骤①:控制器 → 收发器 → 总线

所有设备必须通过CAN收发器接入总线!主控芯片(比如STM32)内部有CAN控制器,控制器只负责协议层,干不了体力活。想连总线必须外挂收发器芯片(例如TJA1050)!

为什么?因为控制器的TX/RX是TTL电平且驱动能力弱,根本扛不住总线上的干扰。所以必须靠收发器实现两件事:把TTL电平转成差分信号,同时增强驱动能力。

步骤②:接线顺序别搞反

- 控制器侧:CPU的TX引脚 → 收发器TX引脚,CPU的RX引脚 → 收发器RX引脚,无需交叉!

- 总线侧:收发器CAN_H接总线CAN_H,CAN_L接总线CAN_L,极性一致即可,所有节点并联到总线上。

二、高速CAN的专属规则(闭环总线)

必备特征➊:头尾加120Ω电阻

高速总线必须是闭环!最后一个节点的CAN_H和CAN_L之间要并联120Ω电阻。原理就像水管堵头:

- 阻抗匹配:高频信号遇到断头会反射回来,和原信号叠加导致波形畸变。120Ω的电阻代表总线特性阻抗,能吸收信号防止反射(类似于在管道末端装缓冲垫)。

- 隐性电压维稳:没人发数据时,120Ω电阻把CAN_H和CAN_L压差拉到0V(逻辑"1"),确保总线处于静默状态。

显性/隐性实操演示:

- 发"0"(显性):收发器强行拉高CAN_H,拉低CAN_L,产生2V压差。

- 发"1"(隐性):收发器直接摆烂不管,120Ω电阻自动把两线压差归零,根本不用动手!

常见错误:忘了加电阻 → 信号跳变时波形疯狂振荡,数据错乱!

三、低速CAN的特殊处理(开环总线)

特征➊:单边2.2kΩ电阻

低速总线(容错CAN)是开环结构!只在总线一端接2.2kΩ电阻(另一端悬空),为什么能防反射?因为低速信号边沿缓,反射问题不严重。这个电阻实际上是偏置电阻,提供一个默认的静默电平。

隐性状态差异:

没有120Ω电阻的暴力归零手段,隐性状态电平靠收发器内部电路维持,抗干扰能力比高速CAN弱。

重要警示:

- 低速CAN不能混用高速收发器!例如TJA1050只能用于高速,低速要用TJA1055(带内部偏置)。

- 速度差距极大:高速CAN支持1Mbps,低速一般≤125kbps。

四、总线物理特征必须牢记

双绞线非选配:

- CAN_H和CAN_L必须双绞!差分信号抗干扰的核心就是靠双绞抵消磁场干扰。

- 单股平行线距离一长必出问题,别不信邪!

拓扑禁忌:

- 高速CAN严禁分叉!所有节点必须在一条主干线上,像糖葫芦一样串起来(手拉手拓扑)。

- 星型/树型拓扑会破坏阻抗连续性 → 信号反射警告!

五、终极重点:为什么能总线仲裁?

硬件决定了规则:显性电平(0)优先级碾压隐性(1)。若两个节点同时发数据:

- 某个bit发"0"的节点会强行覆盖发"1"的节点,后者自动退出发送。

- 这一切都依赖收发器和终端电阻的配合,硬件设计错了一切白搭!

总结一句话:CAN总线的稳定性和仲裁功能,全藏在硬件电路这些细节里!

疑惑点:125 Kbps CAN属于低速还是高速?

核心结论:

-

125 Kbps CAN 明确属于低速/容错CAN (Low-Speed / Fault-Tolerant CAN)。

- 遵循标准: ISO 11898-3。

- 物理层: 使用专用的低速/容错CAN收发器 (如 TJA1054, TJA1055)。

- 特性: 牺牲速度,换取更强的抗干扰能力、容错能力(支持单线工作)和更低的电磁辐射(EMI)。

- 典型应用: 汽车车身控制系统(门窗、座椅、空调、灯光等),对实时性要求不高但对可靠性和故障容忍度要求高的场景。

-

“高速CAN理论下限125Kbps”的说法不准确,是误解。

- 标准无定义: ISO 11898-2(高速CAN)标准没有规定最低工作速率。

- 技术可行性: 高速CAN控制器和收发器技术上可以在很低速率(如10 Kbps, 50 Kbps)工作。

- 工程实践来源: 这个说法源于高速CAN收发器的物理特性:

- 高速收发器针对**中高波特率(如50Kbps - 1Mbps)**优化。

- 在远低于125 Kbps(尤其<50Kbps)时,其固有的快速信号边沿可能导致信号振荡/反射等问题,增加设计难度和潜在错误风险。

- 因此,125 Kbps 常被视为一个工程经验上的“安全且易于实现的低速率起点” 使用高速收发器,但这不是硬性技术下限。

- 最佳实践: 如果应用速率在 125 Kbps 或更低,强烈推荐使用低速/容错CAN (ISO 11898-3)。它在低速段提供更好的鲁棒性、容错性和设计便利性,是规范且优化的选择。

一句话总结:

125 Kbps 是低速/容错CAN的标准速率,不属于高速CAN。所谓“高速CAN理论下限125Kbps”是误解,源于高速收发器在极低速率下的工程挑战;实际低速应用应首选低速/容错CAN方案。

补充说明常见速率梯度:

- 高速CAN (ISO 11898-2): 典型速率 1 Mbps, 500 Kbps, 250 Kbps。偶尔也见 125 Kbps(需注意潜在信号挑战,非最优选)。

- 低速/容错CAN (ISO 11898-3): 标准速率范围 40 Kbps - 125 Kbps(常见 125 Kbps, 83.3 Kbps, 50 Kbps)。

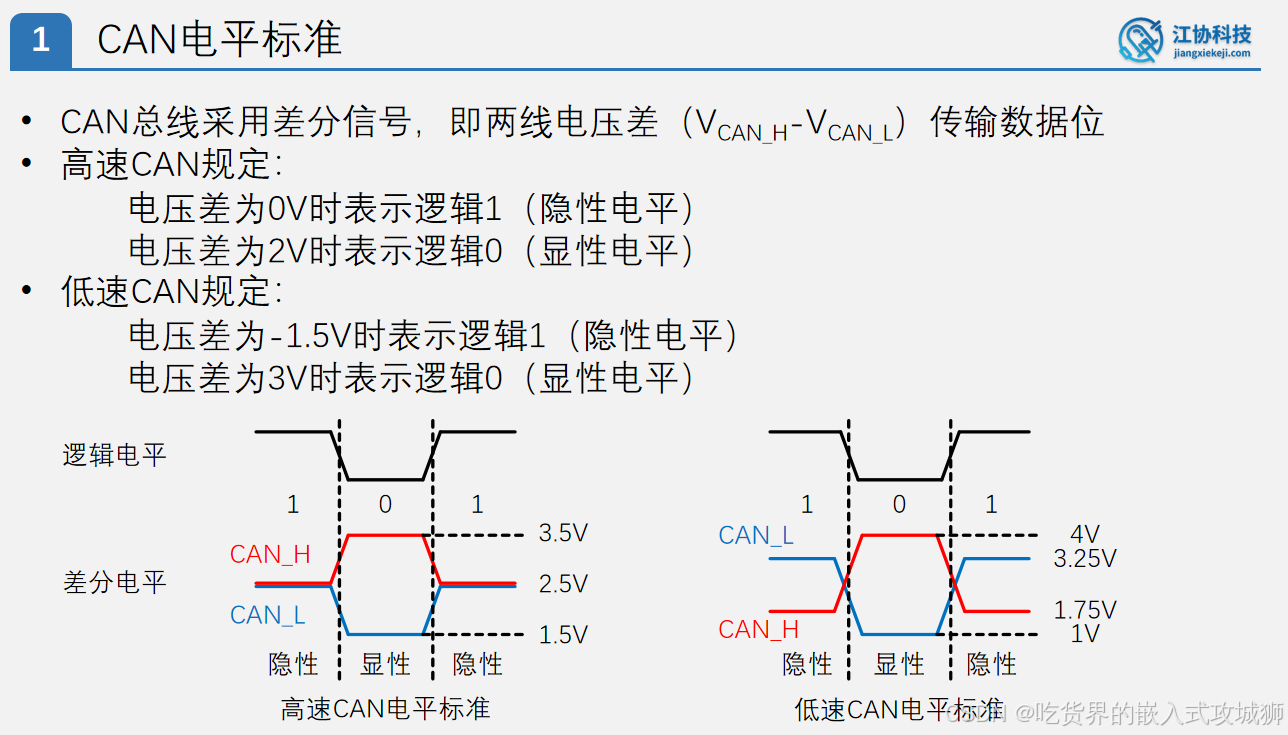

1.2 CAN电平标准

CAN 总线电平标准详解

我们接下来分析 CAN 总线的电平标准。如前所述,CAN 总线采用差分信号传输数据,即通过两根线(CAN_H 和 CAN_L)之间的电压差(Vdiff = VCAN_H - VCAN_L)来表示数据位(1 或 0)。

1. 高速 CAN 电平标准

- 逻辑 1 (隐性电平): 当 Vdiff ≈ 0 V(即 CAN_H 和 CAN_L 对地电压均约为 2.5 V)时,表示逻辑 1。此状态称为隐性电平。

- 逻辑 0 (显性电平): 当 Vdiff ≈ 2 V(例如 CAN_H ≈ 3.5 V, CAN_L ≈ 1.5 V)时,表示逻辑 0。此状态称为显性电平。

为什么逻辑 1 对应隐性,逻辑 0 对应显性?

这个定义看似反直觉(通常认为 1 代表“有”或“活动”,应为显性),但有其设计原因:

- 总线状态本质:

- 隐性状态 (逻辑 1): 表示总线处于“空闲”或“默认”状态。此时两根线电压相等(无电压差),信号线“收紧”(趋向相同电位),不需要设备主动驱动。这是总线的自然、被动状态。

- 显性状态 (逻辑 0): 表示总线被某个设备主动驱动以传输数据。此时两根线产生显著电压差(如 2 V),信号线“张开”(电位分离)。这是需要设备干预的“活动”状态。

- 电路设计惯例: 总线默认状态=CAN隐性电平=逻辑1:对于CAN总线来说,默认状态是隐性电平,而对于一般电路来说默认状态是高电平1,所以在CAN总线里面,隐性电平为逻辑1。

- 线与逻辑: CAN 总线具有“线与”特性。当多个节点同时发送时,显性电平 (逻辑 0) 会覆盖隐性电平 (逻辑 1)。这与数字电路中“0 强于 1”(低电平有效,或开漏输出下拉时)的常见设计原则一致。

简单来说:显隐性描述的是CAN总线的状态;1和0,是为了与电路约定俗成的规则对应。

波形表示方式

- 差分电平表示: 精确绘制 CAN_H 和 CAN_L 两条线各自的电压波形。

- 逻辑电平表示: 为了简化时序图的绘制(画两根线较繁琐),并且因为总线实际只有隐性(1)/显性(0)两种有效状态,常用单根线的高低电平来象征性地表示总线的状态:

- 高电平 代表 隐性状态 (逻辑 1) -> 总线空闲/默认

- 低电平 代表 显性状态 (逻辑 0) -> 总线活动/数据发送

- 重要提示: 逻辑电平图上的“高/低”并非表示 CAN 总线上传输的是单端的高低电平信号。它仅代表此时总线是处于“收紧”的隐性状态(逻辑 1)还是“张开”的显性状态(逻辑 0)。实际物理层传输的始终是差分信号。

2. 低速/容错 CAN 电平标准

低速 CAN 的电平规定原理与高速 CAN 相同,但参数不同:

- 逻辑 1 (隐性电平): Vdiff ≈ -1.5 V (例如 CAN_L ≈ 3.25 V, CAN_H ≈ 1.75 V)

- 逻辑 0 (显性电平): Vdiff ≈ 3 V (例如 CAN_L ≈ 1 V, CAN_H ≈ 4 V)

高速与低速 CAN 设计差异分析

- 电平幅度: 低速 CAN 显性电平的差分幅度更大(3V vs 2V),隐性电平也有反向偏置(-1.5V)。这增大了逻辑 0 和逻辑 1 之间的电压差“行程”。

- 目的: 增大电压差行程是为了增强抗干扰能力和信号在更长距离传输时的鲁棒性。即使线路上存在一定的压降,较大的差分电压仍能清晰地区分逻辑状态。

- 隐性状态差异: 低速 CAN 在隐性状态时,CAN_H 和 CAN_L 电压不相等(这与高速 CAN 隐性时电压相等不同)。

- 终端电阻影响: 由于低速 CAN 隐性状态下两线电压不等,其不能像高速 CAN 那样在总线两端使用一个单一的、连接 CAN_H 和 CAN_L 的终端电阻(通常为 120Ω)。高速 CAN 使用这种电阻是为了在隐性状态(两线等电位)时形成电流回路,并帮助总线在显性驱动结束后快速、稳定地回归到隐性状态(电压相等)。这种快速回归是高速 CAN 能实现高传输速率的关键因素之一。低速 CAN 回归隐性状态相对较慢,因此其最大传输速率较低。

疑惑点:为什么低速CAN要“增大电压差行程”来应对压降?线路上存在一定的压降 ?

核心结论:

“线路上存在一定的压降” 是一个在电子工程和电力传输中非常基础且重要的概念。它指的是 电压(或电势差)在电流流过导体(如电线、电缆、PCB走线)时,沿着导体长度方向逐渐降低的现象。

以下是详细的解释:

-

根本原因:导体的电阻

- 任何实际的导线(如铜线、铝线)都不是理想导体,它们本身具有一定的电阻。

- 根据欧姆定律 (V = I * R),当电流

I流过具有电阻R的导体时,就会在导体两端产生一个电压降V。 - 这个电压降

V的方向与电流方向相反,表现为从电源正极出发,沿着导线流向负载,电压值逐渐降低。

-

物理过程:能量转换

- 电流流过电阻时会做功,将一部分电能转换成热能(焦耳热)。

- 正是这部分被消耗掉的能量,导致了电压沿着导线长度的降低。导线越长或电阻越大(或电流越大),产生的热量越多,电压降就越大。

-

类比理解:水流系统

- 想象一条长长的水管(代表导线)连接水泵(代表电源)和水龙头(代表负载)。

- 水泵提供水压(代表电压),推动水流(代表电流)流过水管。

- 水管壁本身对水流有摩擦阻力(代表电阻)。水流克服阻力前进时,水压会沿着水流方向逐渐降低。当你打开水龙头时,水龙头处的水压肯定低于水泵出口处的水压。这个水压的损失就是“压降”的类比。

-

在信号传输(如CAN总线)中的具体表现和影响:

- 信号源发送端: 驱动芯片(CAN收发器)在总线(CAN_H和CAN_L)上产生一个目标差分电压

V_diff_sent(例如低速CAN显性状态目标为3V)。 - 信号接收端: 接收芯片需要检测总线上的实际差分电压

V_diff_received。 - 压降的产生: 当信号电流流过具有电阻的总线电缆(尤其是长距离传输时)时,根据欧姆定律

V_drop = I_signal * R_wire:I_signal:传输信号所需的电流。R_wire:导线的总电阻(与导线长度、截面积、材料有关)。

- 结果: 接收端实际测量到的差分电压

V_diff_received会低于发送端发出的目标电压V_diff_sent。即:

V_diff_received ≈ V_diff_sent - V_drop - 负面影响:

- 信号幅度减小: 接收端看到的信号“强度”变弱了。如果压降过大,

V_diff_received可能降低到接近甚至低于接收器能够可靠识别逻辑状态(1或0)的阈值电压。 - 误码风险增加: 原本清晰的逻辑“0”(显性,大正压差)可能因为压降变得不够“显性”,容易被噪声干扰,或者在接收端被误判为逻辑“1”(隐性,小或负压差)。反之亦然。

- 传输距离受限: 压降是限制信号能够可靠传输的最大距离的关键因素之一。

- 信号幅度减小: 接收端看到的信号“强度”变弱了。如果压降过大,

- 信号源发送端: 驱动芯片(CAN收发器)在总线(CAN_H和CAN_L)上产生一个目标差分电压

-

为什么低速CAN要“增大电压差行程”来应对压降?

- 低速CAN设计用于更长距离的传输,这意味着潜在的压降

V_drop会更大。 - 通过显着增大逻辑“0”(显性)和逻辑“1”(隐性)之间的目标电压差

V_diff_sent(例如从高速CAN的2V增大到低速CAN的3V或更大范围),即使经过长距离传输产生了可观的压降V_drop(比如0.5V甚至1V),接收端测量到的实际电压差V_diff_received仍然足够大。 - 这个“足够大”的

V_diff_received确保了:- 逻辑“0”和逻辑“1”之间仍有清晰可辨的电压差。

- 接收器能可靠地区分两种状态。

- 系统对压降和噪声具有鲁棒性,降低了误码率。

- 低速CAN设计用于更长距离的传输,这意味着潜在的压降

总结:

“线路上存在一定的压降” 就是指 由于导线本身的电阻,当电流(信号电流或电源电流)流过它时,沿着导线方向电压会逐渐降低。在长距离信号传输(如汽车CAN总线、工业现场总线、电力传输)中,这是一个必须考虑的关键因素,因为它会削弱信号强度,影响系统可靠性和最大传输距离。设计时(如低速CAN)通过增大初始信号幅度(电压差)来预留“余量”,就是为了抵消这种压降带来的负面影响。

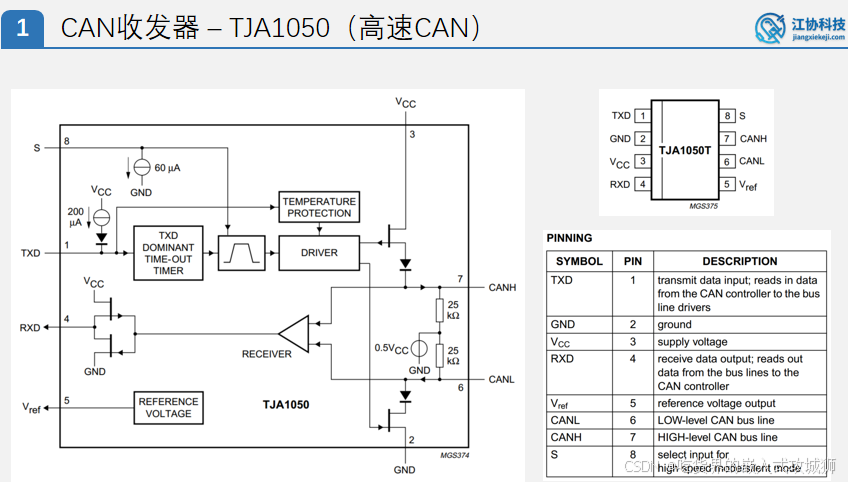

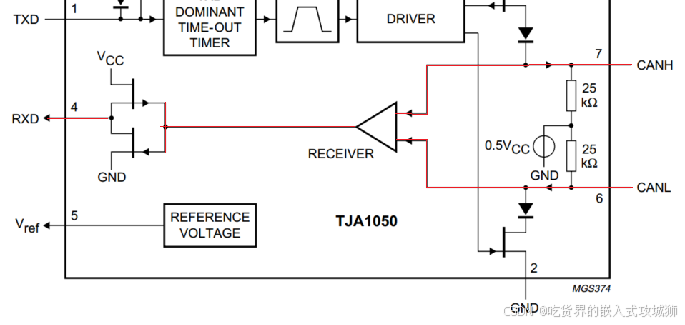

1.3 CAN收发器-TJA1050(高速CAN)

CAN收发器(TJA1050)内部结构与功能详解

理解CAN设备需要通过CAN收发器连接总线后,我们进一步分析收发器的核心功能和工作机制。以TJA1050高速CAN收发器为例(8引脚封装),其框图清晰地展示了内部结构。

1. 核心功能概述

- 接口转换: 连接微控制器(逻辑电平:TXD, RXD)与物理CAN总线(差分信号:CAN_H, CAN_L)。

- 信号方向:

- 发送(TX): 将控制器输出的逻辑信号(TXD) 转换为驱动CAN总线的差分信号。

- 接收(RX): 将CAN总线上的差分信号转换为控制器可识别的逻辑信号(RXD)。

- 总线状态管理: 提供隐性状态偏置,并包含保护机制(显性超时、热关断)。

2. 引脚功能简述

- GND, VCC (5V): 电源与地。

- TXD, RXD: 连接微控制器的CAN控制器模块(逻辑电平接口)。

- CAN_H, CAN_L: 连接物理CAN总线(差分信号接口)。

- Vref (可选): 参考电压输出,通常可悬空。

- S (可选): 模式选择引脚(高速模式 / 静默模式)。内部有下拉电流源,悬空时默认输入低电平(高速模式)。

3. 发送路径 (逻辑信号 -> 差分信号)

- 输入驱动 (TXD):

- 当 TXD = 1 (高电平,逻辑1 / 隐性):

- 内部驱动器关闭输出级。

- CAN_H 和 CAN_L 不被驱动,总线状态由外部终端电阻决定(呈现隐性电平,Vdiff ≈ 0V)。

- 当 TXD = 0 (低电平,逻辑0 / 显性):

- 内部驱动器激活输出级。

- 上管导通: 将 CAN_H 拉高(趋向 VCC)。

- 下管导通: 将 CAN_L 拉低(趋向 GND)。

- 在 CAN_H 和 CAN_L 之间产生显著电压差 (≈2V),总线呈现显性电平。

- 当 TXD = 1 (高电平,逻辑1 / 隐性):

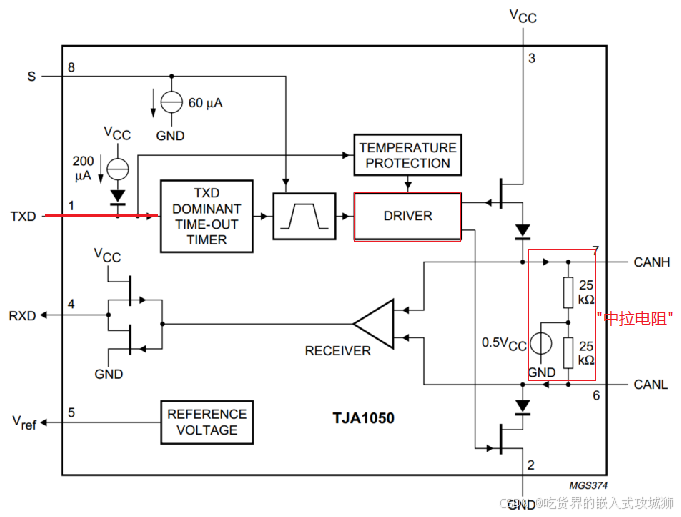

- 内部偏置电阻: 内部电阻网络(描述中的“中拉电阻”)将 CAN_H 和 CAN_L 偏置到约 0.5 * VCC (≈2.5V) 的共模电压。这有助于在总线隐性状态下稳定总线电压(与终端电阻共同作用),但其阻值较大,稳定总线的主要作用仍由外部终端电阻 (通常 120Ω) 承担。

4. 接收路径 (差分信号 -> 逻辑信号)

- 差分接收器: 持续监测 CAN_H 和 CAN_L 之间的电压差 (Vdiff)。

- 内部比较与电平转换:

- 当检测到显性电平 (Vdiff ≈ 2V, 逻辑0) 时,接收器输出低电平 (0)。

- 当检测到隐性电平 (Vdiff ≈ 0V, 逻辑1) 时,接收器输出高电平 (1)。

- 输出驱动 (RXD): 内部电平转换电路(描述中的“两个管”构成反相器)将接收器的输出驱动到RXD引脚:

- 总线显性 (逻辑0) -> RXD 输出低电平 (0)

- 总线隐性 (逻辑1) -> RXD 输出高电平 (1)

5. 关键保护与辅助功能

- 显性超时定时器 (TXD Dominant Timeout):

- 问题: 如果控制器故障导致 TXD 持续为低 (显性),收发器会持续驱动总线为显性状态,阻塞整个总线通信。

- 保护机制: 该定时器监控 TXD 低电平持续时间。若超过设定时间(典型值~1ms),收发器强制释放总线(等效于 TXD=1),使总线回归隐性状态,防止总线锁死。

- 输入钳位 (TXD 悬空处理): 内部电路确保若 TXD 引脚悬空,其输入被钳位为逻辑高电平 (隐性),防止不确定状态导致总线误操作。

- 热关断保护 (Thermal Shutdown): 检测芯片结温。若温度超过安全阈值,强制关闭输出驱动器,断开收发器与总线的连接,防止芯片损坏并避免干扰总线。

- 模式选择 (S 引脚): 选择工作模式:

- 高速模式 (S=低电平,默认): 正常高速通信模式。

- 静默模式 (S=高电平): 接收功能正常,发送功能被禁用(TXD 输入被忽略,输出驱动器关闭)。适用于仅需监听总线的节点。

6. 收发器行为总结

- TXD=1 (高电平) / TXD悬空: 收发器不驱动总线。总线由终端电阻维持隐性状态 (逻辑1)。

- TXD=0 (低电平): 收发器主动驱动总线,产生显性状态 (逻辑0) 的差分信号。

- 显性超时: TXD=0 持续时间过长时,收发器自动停止驱动总线,恢复隐性状态。

- 总线状态 -> RXD: 总线显性 -> RXD=0 (低电平);总线隐性 -> RXD=1 (高电平)。

1.4 CAN物理层特性