PCIe Base Specification解析(一)

文章目录

- 1. Introduction

- 1.1 A Third Generation I/O Interconnect

- 1.2 PCI Express Link

- 1.3 PCI Express Fabric Topology

- 1.3.1 RC

- 1.3.2 Endpoint

- 1.3.2.1 Legacy Endpoint Rules

- 1.3.2.2 PCI Express Endpoint Rules

- 1.3.2.3 RC Integrated Endpoint Rules

- 1.3.3 Switch

- 1.3.4 Root Complex Event Collector

- 1.3.5 PCI Express to PCI/PCI-X Bridge

- 1.4 Hardware/Software Model for Discovery, Configuration and Operation

- 1.5 PCI Express Layering Overview

- 1.5.1 Transaction Layer

- 1.5.2 Data Link Layer

- 1.5.3 Physical Layer

- 1.5.4 Layer Functions and Services

- 1.5.4.1 Transaction Layer Services

- 1.5.4.2 Data Link Layer Services

- 1.5.4.3 Physical Layer Services

- 1.5.4.4 Inter-Layer Interfaces

- 1.5.4.4.1 Transaction/Data Link Interface

- 1.5.4.4.2 Data Link/Physical Interface

1. Introduction

本章概述了PCI Express架构和关键概念。PCI Express是一种高性能的通用1/0互连,用于各种未来的计算和通信平台。保留了关键的PCI属性,例如其usage model,load-store architecture和 software interfaces,而其并行总线实现则被高度可扩展的完全串行接口所取代。PCI Express利用点对点互连,基于Switch的技术和分组协议的最新进展来提供新级别的性能和功能。PCI Express 支持的一些高级功能包括电源管理,服务质量(QoS),热插拔支持,数据完整性和错误处理。

1.1 A Third Generation I/O Interconnect

此第三代I/0互连的高级需求如下:

-

支持多个细分市场和新兴应用:

- 桌面,移动设备,工作站,服务器,通信平台和嵌入式设备的统一1/0架构。

-

能够提供低成本,多种解决方案:

- 在系统级别达到或低于PCI的成本。

-

支持多种平台互连:

- 通过连接器或电缆进行芯片级互连或板级互连。

-

新的机械外形规格(mechanical form factors):

-

[M.2], [CEM] (Card Electro-Mechanical), [U.2], [OCuLink]

注:Form Factor(外形规格),指的是PCle机械接口元件。

M.2接口是一种新的主机接口方案,可以兼容多种通信协议,如sata、PCle、USB、HSIC、UART、SMBus等。

CEM指的就是插槽接口。

M.2接口的固态硬盘主要优点在于体积小巧、性能出色,比较广泛的用于台式电脑、笔记本、超级本等便携设备中。而U.2接口则具备速度更快,2.5英寸更好的与目前SATA3.0接口固态硬盘兼容,适合主流笔记本、台式电脑,未来潜力较大。不过配备U.2接口的固态硬盘比较少,尚等待成熟。

OCuLink是PCI-SIG定义的支持PCle 4 Lane的接口,体积更小巧,用来取代刚刚成为标准的U.2 SF-8639。最关键的是,它已经为PCI-E 4.0和PCI-E 5.0标准做好了准备,数据传输率再次翻番至16GT/s至32GT/s。

-

-

PCI兼容软件模型:

- PCI系统配置软件可以无修改的用于枚举和配置PCI Express 设备。

- 可以无修改的在现有操作系统上boot起来。

- 无需修改即可支持现有I/0设备驱动程序。

- 通过采用PCI configuration paradigm 来配置/启用新的PCI Express Function的能力。

-

性能:

-

低开销,低延迟的通信可最大程度地提高应用程序有效负载带宽和链路效率。

-

每个引脚的高带宽可最大程度地减少每个设备和连接器接口的引脚数。

-

通过聚合通道和信令频率扩展性能。

-

-

高级特性:

-

理解不同的数据类型和排序规则。

-

电源管理和预算。

- 识别给定Function的电源管理功能的能力。- 控制给定Function进入相应低功耗状态的能力。- 能够接收Function当前电源状态的报告。- 能够生成从主电源的电源关闭状态唤醒的请求。- 能够对设备加电进行排序,以允许在功率预算中采用合适的平台策略。

-

-

支持差异化服务的能力,即不同的服务质量(QoS)。

-

面对队头阻塞,能够为每个QoS数据流提供专用的链路资源,以提高结构效率和有效的应用程序级性能。(VC 技术)

-

每个组件中QoS仲裁策略可配置。

-

能够标记每个数据包的端到端QoS。

-

能够创建端到端同步(基于时间的注入速率控制)解决方案。

-

-

热插拔支持。

-

支持已有的PCI热插拔解决方案。

-

支持原生的热插拔解决方案(不使用任何边带信号)。

-

支持异步移除。

-

所有外形规格的设备支持统一的软件模型。

-

-

数据完整性。

-

对于所有的TLP和DLLP都支持链路级数据完整性。(LCRC技术)

-

支持高可用性解决方案的端到端数据完整性。(ECRC技术)

-

-

错误处理。

-

支持PCI级别的错误处理。

-

支持高级错误报告和处理的能力,以改进故障隔离和恢复的解决方案。

-

-

工艺技术独立性。

- 发送器和接收器支持不同的DC共模电压。

-

易于测试。

- 通过简单地连接到测试设备即可测试电气一致性。

1.2 PCI Express Link

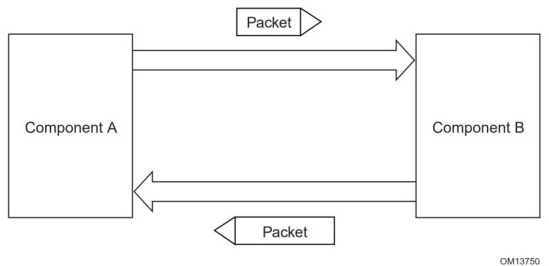

链路表示两个组件之间的双单工(dual-simplex)通信通道。基本的PCI Express链路由两个低压差分驱动信号对组成:发送信号对和接收信号对,如Figure 1-1所示。

Figure 1-1: PCI Express Link

主要链路特征有:

-

基本链路:PCI Express链路由双单向差分链路组成,实现为发送对和接收对。使用编码方案(参见Chapter 4)嵌入数据时钟,以实现很高的数据速率。

-

信号速率:初始化后,每个链路只能在支持的一种信号速率。

-

对于第一代PCI Express技术,2.5 Gigabits/second/Lane/direction的原始带宽(raw bandwidth)。

-

第二代提供有效的5.0 Gigabits/second/Lane/direction的原始带宽。

-

第三代提供了有效的8.0 Gigabits/second/Lane/direction的原始带宽。

-

第四代提供了有效的16.0 Gigabits/second/Lane/direction的原始带宽。

-

第五代提供了有效的32.0 Gigabits/second/Lane/direction的原始带宽。

-

-

Lanes:链路必须支持至少一个Lane-每个Lane代表一组差分信号对(一对用于传输,一对用于接收)。为了扩展带宽,链路可以设计成xN Lane,其中N可以是任何支持的链路宽度。以2.5GT/s数据速率运行的x8链路表示每个方向的原始带宽总带宽为20Gigabits/s。本规范描述了x1,x2,x4,x8,x12,x16和x32通道宽度的操作。

-

初始化:在硬件初始化期间,每个PCI Express

链路是在链路两端的两个设备协商通道宽度和操作频率之后建立的。不涉及固件或操作系统软件。 -

对称性:每个链路必须在每个方向上支持对称数量的通道,即x16链接表示每个方向上有16个差分信号对。

1.3 PCI Express Fabric Topology

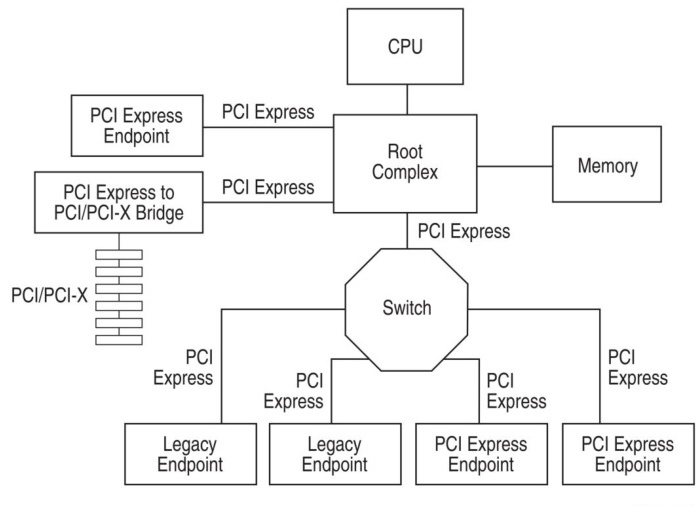

Figure 1-2给出了一个拓扑结构的例子,其中涉及的设备类型有RC(RC)、Endpoints(I/O devices)、Switch、PCI Express to PCI/PCI-X Bridge。

Figure 1-2: Example Topology

1.3.1 RC

- RC表示将CPU/内存子系统连接到I/0的I/0层次结构的根。

- RC可以支持多个Port。每个接口定义了一个独立的分层结构。

-

通过RC在层次结构hierarchy domain之间路由对等事务的功能是可选实现的,并且取决于实现。例如,一个实现可以在RC

内部内部合并一个真实的或虚拟的Switch,从而以软件透明的方式实现对等传输的全面支持。与Switch的规则不同,在hierarchy

domain之间对等路由事务时,通常允许RC将数据包拆分为较小的数据包,例如,将一个256字节有效负载分成两个128字节有效负载的数据包。产生的数据包要遵守此规范中包含的一般数据包定义规则(例如,Max_Payload_Size,Read

Completion Boundary等)。组件设计人员应注意,将数据包拆分为较小的数据包可能会对性能造成负面影响,尤其是对于将寻址PCI Express至PCI Express to PCI/PCI-X Bridge后面的设备的事务进行寻址时。例外:支持Vendor_Defined Message的对等路由的RC不允许将Vendor_Defined Message数据包拆分为较小的数据包(除了128字节边界以外,即除最后一个数据包外的所有数据包必须是128的整数倍),以保证能通过PCI Express将消息转发到PCI/PCI-X Bridge。有关更多信息,请参阅《PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0》。

-

- RC可以发起配置请求。

- RC可以发起I/0请求。

- 允许RC生成到选定根端口的80h和84h位置之一或两个位置的I/O Request,而不考虑该Root Port的PCI桥I/O解码配置;建议仅在特别需要时才启用此机制。

- RC一定不能作为Completer支持Lock语义。

- RC可以发起锁定请求。

1.3.2 Endpoint

Endpoint是这样一种Function:它可以是PCI Express事务的请求者或完成者,可以代表它自己,也可以代表不同的non-PCI Express 设备(PCI设备或主机CPU除外),例如PCI Express连接的图形控制器或PCI Express USB主机控制器。Endpoint分为Legacy、PCI Express或RCIEP。

1.3.2.1 Legacy Endpoint Rules

- Legacy Endpoint 必须是具有Type 00h Configuration Space header的一个 Function。

- Legacy Endpoint 可以接受配置请求。

- Legacy Endpoint 可以接受I/0请求。

- Legacy Endpoin 允许接收对位80h和84h的任意1/0请求,而无需考虑该Endpoint的I/0解码配置。

- Legacy Endpoint 可以生成I/0请求。

- 如果设备的旧版软件支持要求所需,则Legacy Endpoint可以作为Completer支持锁定存储器语义。

- Legacy Endpoint 不能发送Locked Request。

- Legacy Endpoint 可以实现 Extended Configuration Space

Capabilities,但是会被软件忽略。 - Legacy Endpoint 不能发出超过4GB地址空间的请求。

- Legacy Endpoint 如果需要中断源支持,则需要支持MSI或MSI-X或两者都支持。如果实现了MSI,则允许Legacy

- Endpoint 支持MSI Capability的32位或64位Message Address版本。

- Legacy Endpoint 可以通过32bit Base Address register 访问存储器资源。

- Legacy Endpoint必须出现在由RC发起的层次结构域的其中之一里边。

1.3.2.2 PCI Express Endpoint Rules

- PCI Express Endpoint 必须是具有Type 00h Configuration Space

header的一个Function。 - PCI Express Endpoint 可以接受配置请求。

- PCI Express Endpoint 不得依赖操作系统通过BAR声明的I/0资源分配。

- PCI Express Endpoint 不能生成I/0请求。

- PCI Express Endpoint 不能作为Completer 支持 Locked Request,也不能作为Requester生成该请求。兼容PCI Express的软件驱动程序和应用程序要防止在访问PCI Express Endpoint时使用锁定语义。

- PCI Express Endpoint 可以作为 Requester 生成超过4GB地址空间的Memory请求。

- PCI Express Endpoint 如果需要支持中断源,则需要支持MSI或MSI-X或两者都支持。如果实现了MSI,则允许Legacy Endpoint 支持MSI Capability 为64位Message Address版本。

- 通过BAR请求内存资源的PCI Express Endpoint必须设置BAR的Prefetchable字段,除非该范围包含具有读取副作用的地址或有该Function不允许写入合并的地址。有关设置Prefetchable字段的更多信息,请参见Section 7.5.1.2.1。

- 对于PCI Express Endpoint,所有设置了Prefetchable字段的BAR都必须支持64位寻址。对于未设置Prefetchable字段的所有BAR,允许使用32位寻址。

- BAR请求的最小内存地址范围是128个字节。

- PCI Express Endpoint 必须出现在由RC发起的层次结构域的其中之一里边。

1.3.2.3 RC Integrated Endpoint Rules

RCiEP的应用场景是集成在RC内部,专门用于访问存储器。

- RC Integrated Endpoint(RCiEP)是在包含Root Port的RC的内部逻辑上实现的。

- RCiEP必须是具有Type 00h Configuration Space header的一个Function。

- RCiEP必须可以作为Completer支持配置请求。

- RCiEP不得要求通过BAR声明I/0资源。

- RCiEP不能生成I/0请求。

- RCiEP不能作为Completer支持Locked Request,也不能作为Requester 生成该请求。兼容PCI Express的软件驱动程序和应用程序要防止在访问RCiEP时使用锁定语义。

- 要求作为内存事务的请求者运行的RCiEP必须能够生成等于或大于主机能够作为Completer处理的地址。

- RCiEP如果需要中断源支持,则需要支持MSI或MSI-X或两者都支持。如果实现了MSI,则允许RCiEP支持MSI Capability

的32位或64位Message Address版本。 - RCiEP可以通过32位BAR地址访问存储器资源。

- RCiEP不能实现Link Capabilities、Link Status、Link Control、Link Capabilities 2、Link Status 2和Link Control 2 寄存器。

- 如果RCiEP与一个可选实现的Root Complex Event Collector相关联,则RCiEP必须通过Root Complex Event Collector 发送 PME 信令和错误条件信令。

- RCiEP不能与一个以上的Root Complex Event Collector 相关联。

- RCiEP 不能实现ASPM。

- RCiEP可能无法独立于整个RC进行热插拔。

- RCiEP不得出现在RC可见的任何层次结构域中。

- RCiEP不得出现在Switch中。

1.3.3 Switch

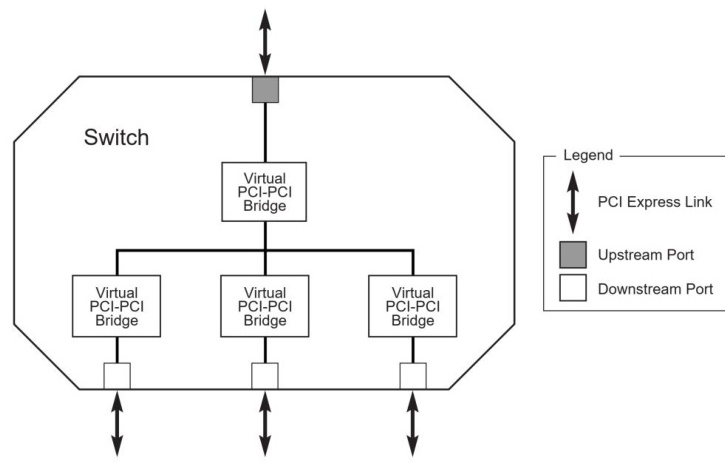

Switch 定义为多个虚拟PCI-to-PCI Bridge 设备的逻辑组合,如Figure 1-3所示。所有Switch均受以下基本规则约束。

Figure 1-3: Logical Block Diagram of a Switch

- 从配置软件的视角,Switch是两个或多个逻辑PCI-to-PCI Bridge。

- Switch使用PCI桥机制转发事务,例如基于地址的路由,如Section 6.14。

- 除非本文档中另有说明,否则Switch必须支持在任何一组Port之间转发所有类型的事务层数据包。

- 必须支持Locked Request,如Section 6.5描述。Switch的下游端口不需要支持作为锁定请求的发射端口。

- 每个使能的Switch端口都要遵循流控制协议。

- 不允许Switch将数据包拆分为较小的数据包,例如,不得将具有256字节有效负载的单个数据包分为两个128字节有效负载的数据包。

- 当在同一虚拟通道上发生争用时,可以使用轮询或加权轮询来实现Switch的Ingress Port之间的仲裁。规范在后续章节会对此进行更详细的描述。

- 端点(由Type 00h Configuration Space header表示)不得在Switch内部总线上的配置软件中显示为表示Switch下游端口的虚拟PCI-to-PCI Bridge的对等方。

1.3.4 Root Complex Event Collector

- Root Complex Event Collector为来自RCiEP的错误和PME消息提供支持。

- Root Complex Event Collector 需要遵循所有的RCiEP的规则。

- Root Complex Event Collector 不需要解码任何Memory请求或1/0请求。

- Root Complex Event Collector 由其 Device/Port Type值标识(请参阅Section7.5.3.2)。

- Root Complex Event Collector的 Base Class 为08h, Sub-Class为06h, Programming Interface为00h。

- Root Complex Event Collector驻留在RC中的总线上。多个Root Complex Event Collector允许驻留在单个总线上。

- Root Complex Event Collector 与其支持的RCiEP位于同一逻辑总线上。

- 多个 Root Complex Event Collector允许驻留在单个逻辑总线上。

- Root Complex Event Collector 通过 Root Complex Event Collector Endpoint Association Capability 显式声明支持的RCiEP。

- Root Complex Event Collector的实现是可选的。

1.3.5 PCI Express to PCI/PCI-X Bridge

- PCI Express to PCI/PCI-X Bridge 设备用于连接PCI Express和PCI/PCI-X外设。

- PCI Express-至PCI/PCI X Bridge的PCI Express-端口必须符合本文档的要求。

1.4 Hardware/Software Model for Discovery, Configuration and Operation

PCI/PCle 硬件/软件模型包括discover、configure和使用一个Function所必需的体系结构,而无需特定于Function的知识。关键要素包括:

- 一种配置模型,为系统软件提供发现系统中可用硬件Function的方法。(Capability)

- 为诸如内存空间和中断之类的可寻址资源执行基本资源分配的机制。(BAR)

- 启用/禁用 Function 响应收到的Request以及Function 发起 Request的控制信息。(BME)

- 定义明确的排序和流控制模型,以支持一致/稳健的硬件/软件接口实现。

PCI Express 配置模型支持两种机制:

- PCI兼容配置机制:PCI兼容机制支持与PCI 3.0或更高版本的操作系统以及它们相应的总线枚举和配置软件的100%兼容性。

- PCI Express 增强的配置机制:提供了增强的机制以增加可用配置空间的大小并优化访问机制。

每个PCI Express链路均通过虚拟PCI-to-PCI Bridge结构进行映射,并具有与其关联的逻辑PCI总线。虚拟PCI-to-PCI Bridge 可以是PCI Express RC Port、Switch Upstream Port 或 Switch Downstream Port的一部分。Root Port是一种虚拟的PCI-to-PCI Bridge 结构,它是从PCI ExpressRC中产生PCI Express层次结构域的。设备被映射到配置空间,以便每个设备都将响应特定的设备编号。

1.5 PCI Express Layering Overview

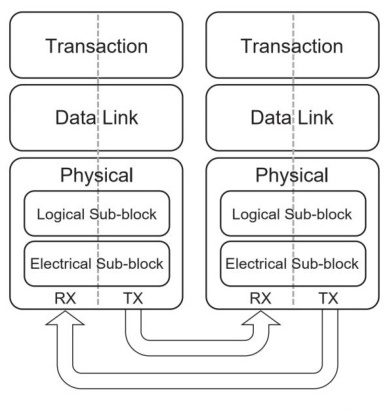

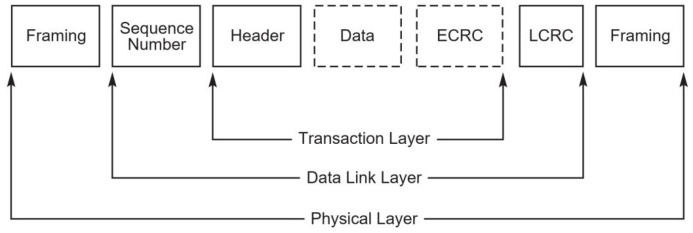

PCI Express 结构如 Figure 1-4。

Figure 1-4: High-Level Layering Diagram

该分层定义的目的是促进读者对规范的理解。请注意,此分层并不意味着特定的PCI Express实现。

PCI Express 使用数据包在组件之间传递信息。数据包在事务和数据链路层中形成,以将信息从发送组件传送到接收组件。当传输的数据包流经其他层时,它们会以处理这些层的数据包所需的附加信息进行扩展。在接收端发生相反的过程,数据包从其物理层表示转换为数据链路层表示,最后(对于事务层数据包)转换为可以由接收设备的事务层处理的形式。Figure 1-5显示了通过层的事务级别数据包信息的概念性流程。

Figure 1-5: Packet Flow Through the Layers

注意,出于链路管理的目的,在两个数据链接层之间支持一种更简单的分组通信形式。

1.5.1 Transaction Layer

事务层的主要责任是事务层数据包(TLP)的组装和拆卸。TLP用于通信事务,例如读和写以及某些类型的事件。事务层还负责管理TLP的基于信用的流控制功能。

每个需要响应包的请求包都实现为split transaction。每个数据包都有一个唯一的标识符,该标识符使响应数据包可以定位到正确的请求者。数据包格式支持不同形式的寻址,具体取决于事务的类型(Memory、I/O、Configuration和Message)。Packet还可以具有No Snoop, Relaxed Ordering 和ID-Based Ordering(IDO)等属性。

事务层支持四个地址空间:它包括三个PCI地址空间(memory、I/O和configuration),并添加了Message Space。该规范使用Message Space 来支持所有先前的边带信号,例如中断,电源管理请求等。您可以将PCI Express消息事务视为“虚拟线”,因为它们的作用是消除当前平台实现中使用的各种边带信号。

1.5.2 Data Link Layer

数据链路层处于PCle协议栈的中间层,充当事务层和物理层之间的中间阶段。数据链路层的主要职责包括链路管理和数据完整性,包括错误检测和错误纠正。

数据链路层的传输端接受由事务层组装的TLP,计算并应用数据保护代码和TLP序列号,并将它们提交给物理层,以在链路上传输。接收数据链路层负责检查接收到的TLP的完整性,并将其提交给事务层进行进一步处理。在检测到TLP错误后,此层负责请求重发TLP,直到正确接收到信息或确定链路已失败为止。

数据链路层还生成并使用用于链路管理功能的数据包。为了将这些数据包与事务层(TLP)使用的数据包区分开,当引用数据链路层生成和使用的数据包时,将使用术语“数据链路层数据包(DLLP)”。

1.5.3 Physical Layer

物理层包括用于接口操作的所有电路,包括驱动器和输入缓冲器,并行到串行和串行到并行转换,PLL和阻抗匹配电路。它还包括与接口初始化和维护有关的逻辑功能。物理层以实现特定的格式与数据链路层交换信息。该层负责将从数据链路层接收的信息转换为适当的序列化格式,并以与连接到链路另一端的设备兼容的频率和宽度在PCI Express 链路上传输该信息。

PCI Express 架构具有“钩子”特性,可以通过速度升级和高级编码技术来支持将来的性能增强。未来的速度,编码技术或媒体可能只会影响物理层的定义。

1.5.4 Layer Functions and Services

1.5.4.1 Transaction Layer Services

事务层在生成和接收TLP的过程中,与链路另一侧的事务层交换流控制信息。它还负责支持软件和硬件启动的电源管理。

初始化和配置功能要求事务层执行以下操作:

- 存储由处理器或管理设备生成的链路配置信息。

- 通过物理层关于宽度和工作频率的硬件协商而生成的Store Link 功能。

事务层的数据包生成和处理服务要求它:

- 从设备核心请求生成TLP。

- 将收到的请求TLP转换为对设备核心的请求。

- 将收到的完成数据包转换为可交付给核心的有效负载或状态信息。

- 检测不受支持的TLP,并调用适当的机制来处理它们。

- 如果支持端到端数据完整性,请生成端到端数据完整性CRC并相应地更新TLP header。

流控制服务:

- 事务层跟踪整个链路上TLP的流量控制信用。

- 使用数据链路层的传输服务将事务信用状态定期发送到对端事务层。

- 对端流控制信息用于限制本端TLP传输。

排序规则:

- 符合PCI/PCI-X的生产者消费者排序模型。

- 额外支持Relaxed Ordering。

- 额外支持ID-Based Ordering。

电源管理服务:

- ACPI/PCI电源管理。

- 硬件控制的自主电源管理可在全开机状态下最大程度地降低功耗。

Virtual Channels 和 TrafficClass:

- 提供虚通道机制和流量类别标识的组合以支持针对某些类别的应用程序的区分服务和QoS支持。

- 虚通道提供了一种在链路的给定公共物理资源上支持多个独立逻辑数据流的方法。从概念上讲,这涉及将不同的数据流复用到单个物理链路上。

- 流量类别是一个事务层数据包标签,它通过系统未经修改地进行端对端的传输。在系统内的每个服务点(例如,Switch),流量类别标签用于应用适当的服务策略。每个流量类别标签都定义一个唯一的排序域-不为包含不同流量类别标签的数据包提供排序保证。

1.5.4.2 Data Link Layer Services

数据链路层负责与链路另一侧的设备可靠地交换信息。

初始化和电源管理服务:

- 接受来自事务层的电源状态请求并传送到物理层。

- 将active/reset/disconnected/power等链路状态传达给事务层。

数据保护,错误检查和重试服务:

- CRC生成。

- 存储TLP用于数据链路级别重试。

- 错误检查。

- TLP应答和消息重试。

- 错误报告和记录。

1.5.4.3 Physical Layer Services

接口初始化,维护控制和状态跟踪:

- 复位、热插拔控制、状态信息。

- 互联电源管理。

- 链路宽度和通道映射。

- 通道极性翻转。

符号和特殊有序集生成:

- 8b/10b编解码。

- 嵌入式时钟调节和对齐。

符号传输和对齐:

- 传输电路。

- 接收电路。

- 接收侧的弹性缓冲器。

- 接收侧的Lane-to-Lane de-skew。

DFT支持的功能:

- Compliance pattern。

- Modified Compliance pattern。

1.5.4.4 Inter-Layer Interfaces

1.5.4.4.1 Transaction/Data Link Interface

事务层到数据链路层提供:

- 要通过链路发送的数据。

- 本地的TLP传输握手机制。

- TLP边界信息。

- 请求的链路电源状态。

数据链路层到事务层提供:

- 从链路接收的数据。

- 接收到的数据的组包信息。

- 链路实际的电源状态。

- 链路状态信息。

1.5.4.4.2 Data Link/Physical Interface

数据链路层到物理层提供:

- 要通过链路发送的数据。

- 数据传输握手机制。

- TLP和DLLP边界信息。

- 请求的链路电源状态。

物理层到数据链路层提供:

- 从链路接收到的数据。

- TLP和DLLP数据的组包信息。

- 物理层的错误检测信息。

- 实际链路状态。

- 连接状态信息。