戴维南端接与 RC端接

戴维南端接与 RC端接:

终端的并联端接存在很多不足的地方。例如,上拉端接会抬高信号的低电平,下拉端接会降低信号的高电平,这两种端接方式虽然都可以抑制过冲和振铃,但同时也会减小信号裕量,如果使用不当还会造成信号电平的误触发。那么有没有一种端接方式既可以抑制过冲和振铃,又没有这些缺陷呢?方法是有的,那就是综合这些端接的优点,想办法回避这些端接的缺点。下面我们就来看看戴维南端接和RC端接。

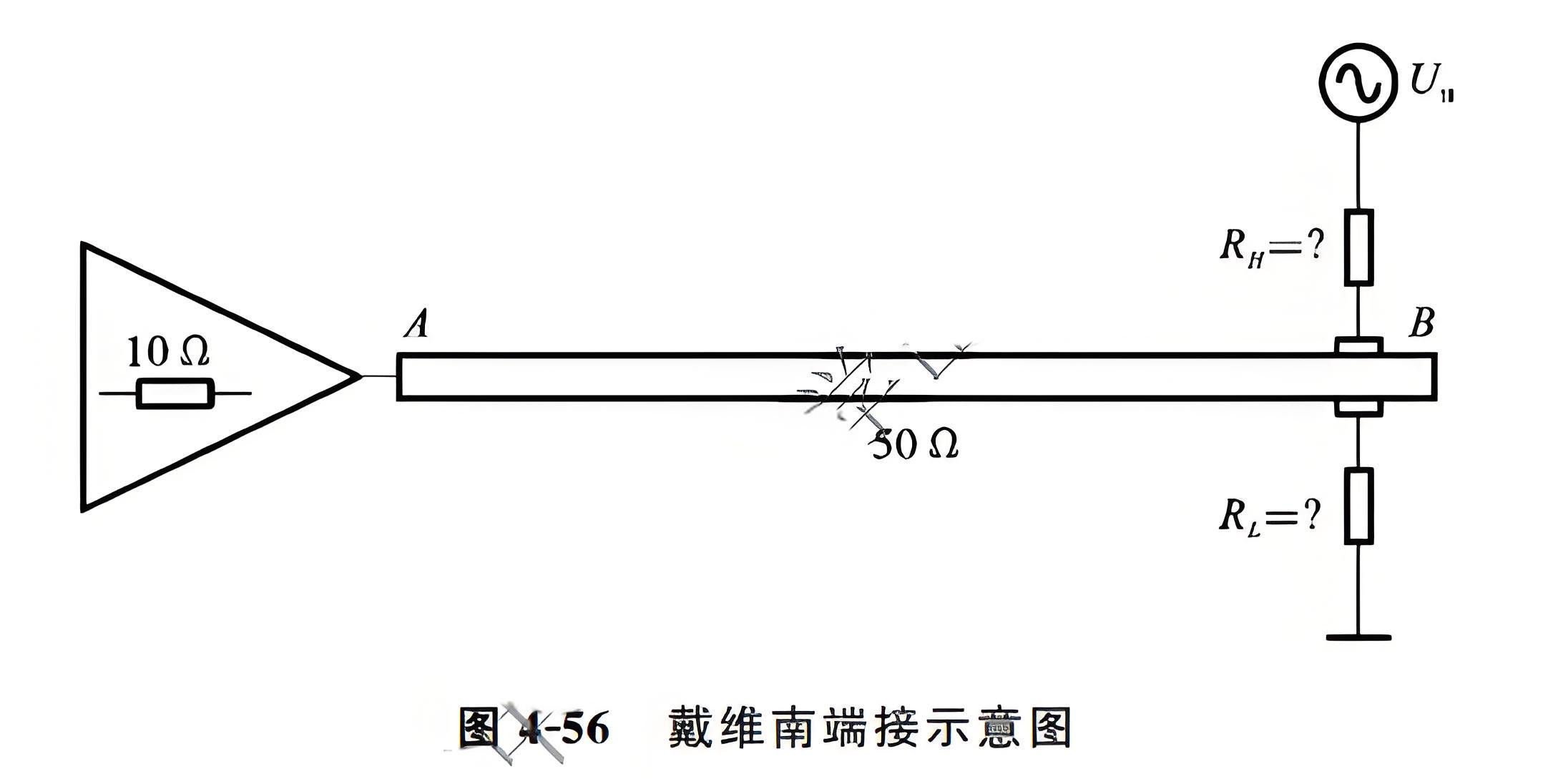

戴维南端接综合了上拉和下拉并联端接的方法,如图4-56所示。

我们见得最多的使用戴维南端接的信号就是DDR2的地址、控制命令信号,还记得曾经的一个100Ω电阻上拉端接到1.8 V的电压,另一个100 Ω电阻下拉端接到地的情形吗?虽然空间已经很小了,但还是不得不连接这些电阻,这个就是戴维南端接。

要实现阻抗匹配,就必须满足两个端接电阻的并联值等于传输线的阻抗值,即=

*

/(

+

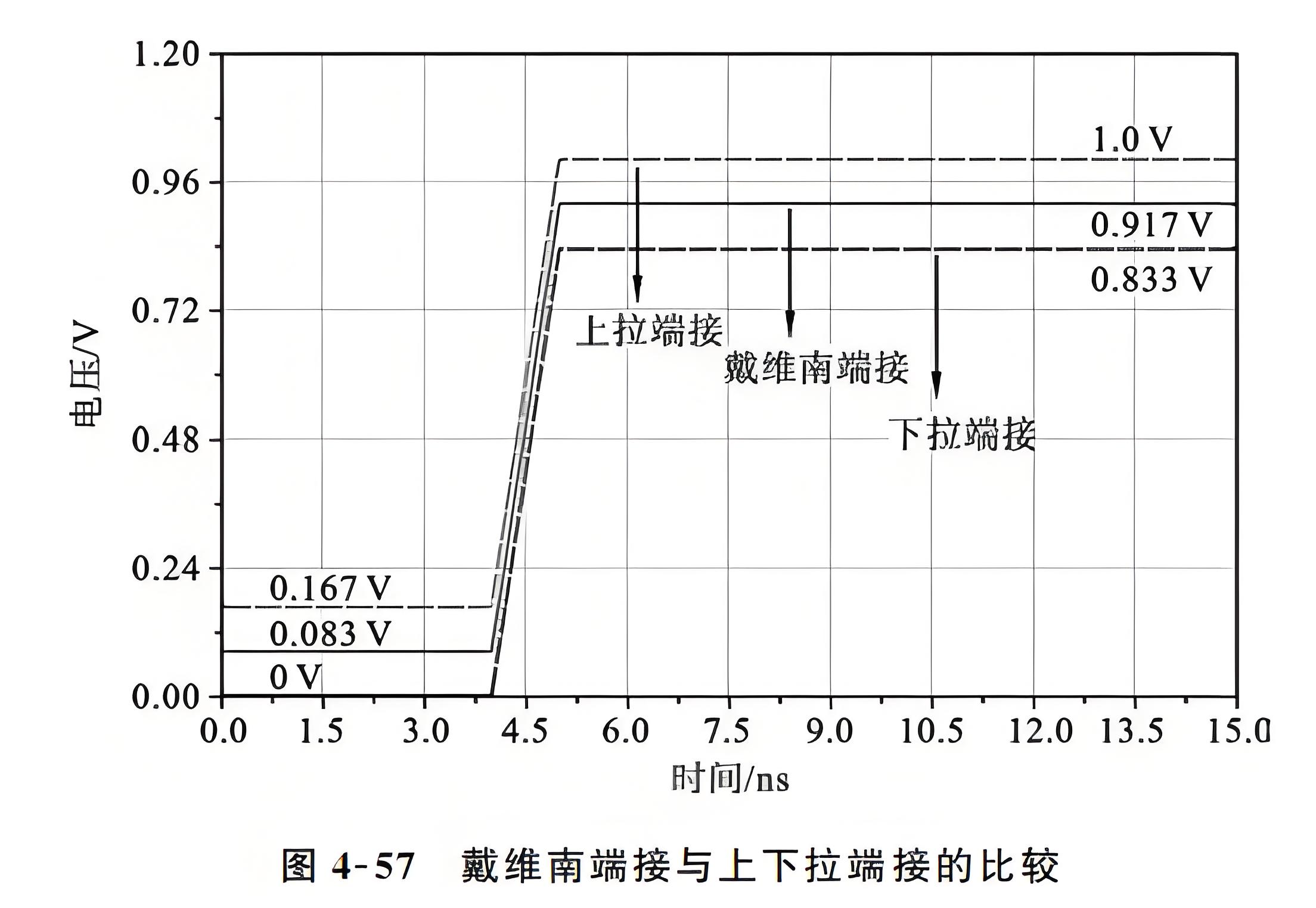

)相对于上拉端接和下拉端接,采用戴维南端接会对信号产生什么影响呢?这里也做了一个仿真对比。在阻抗匹配的情况下(上拉电阻和下拉电阻等于传输线阻抗,戴维南端接并联阻抗等于传输线阻抗),在如图4-57所示的仿真波形中,对比了上拉端接、下拉端接以及戴维南端接之间的区别。

通过图4-57我们可以看到,采用戴维南端接后,终端电压的低电平和高电平都介于上拉端接和下拉端接之间。这种端接方式会使信号的摆幅减小。当然,图4-57只是简单地仿真了各种端接方式对阶跃信号的影响,实际电路在工作时传输的是数字信号。上拉端接和下拉端接的电阻的选择应该根据具体的信号来确定,一般可以通过仿真软件来确定合适的上拉端接和下拉端接的电阻阻值。

同时采用上拉端接和下拉端接,信号的摆幅就减小了,由于存在驱动器内阻,低电平不能等于0V,而且在电路没有工作时,上拉电阻和下拉电阻上依然会有电流,这样会增加电路的

功率消耗。为了解决这个问题,RC端接被派上了用场。

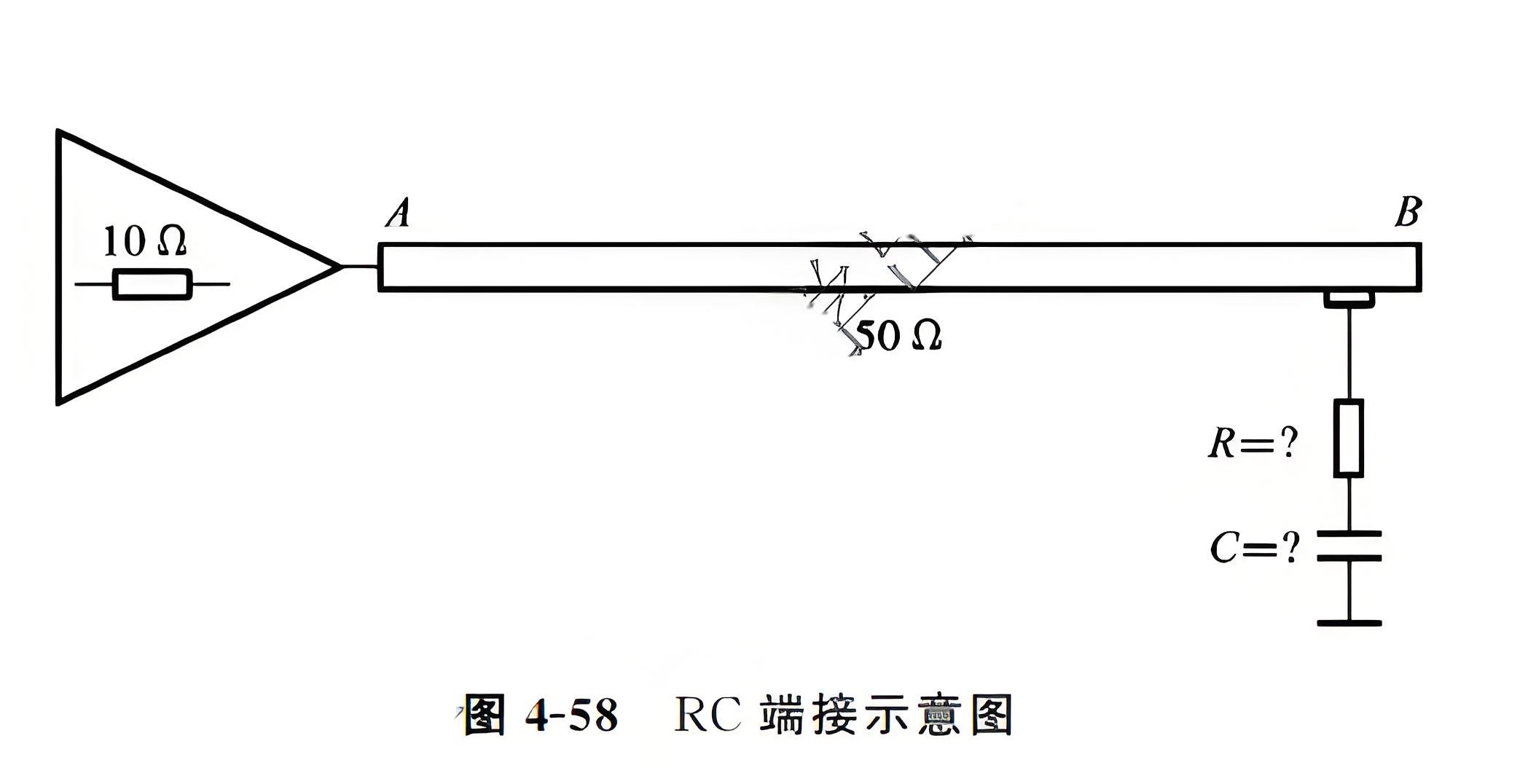

RC端接如图4-58所示,这种端接方式是在传统的末端下拉端接的基础上增加了一个电容。

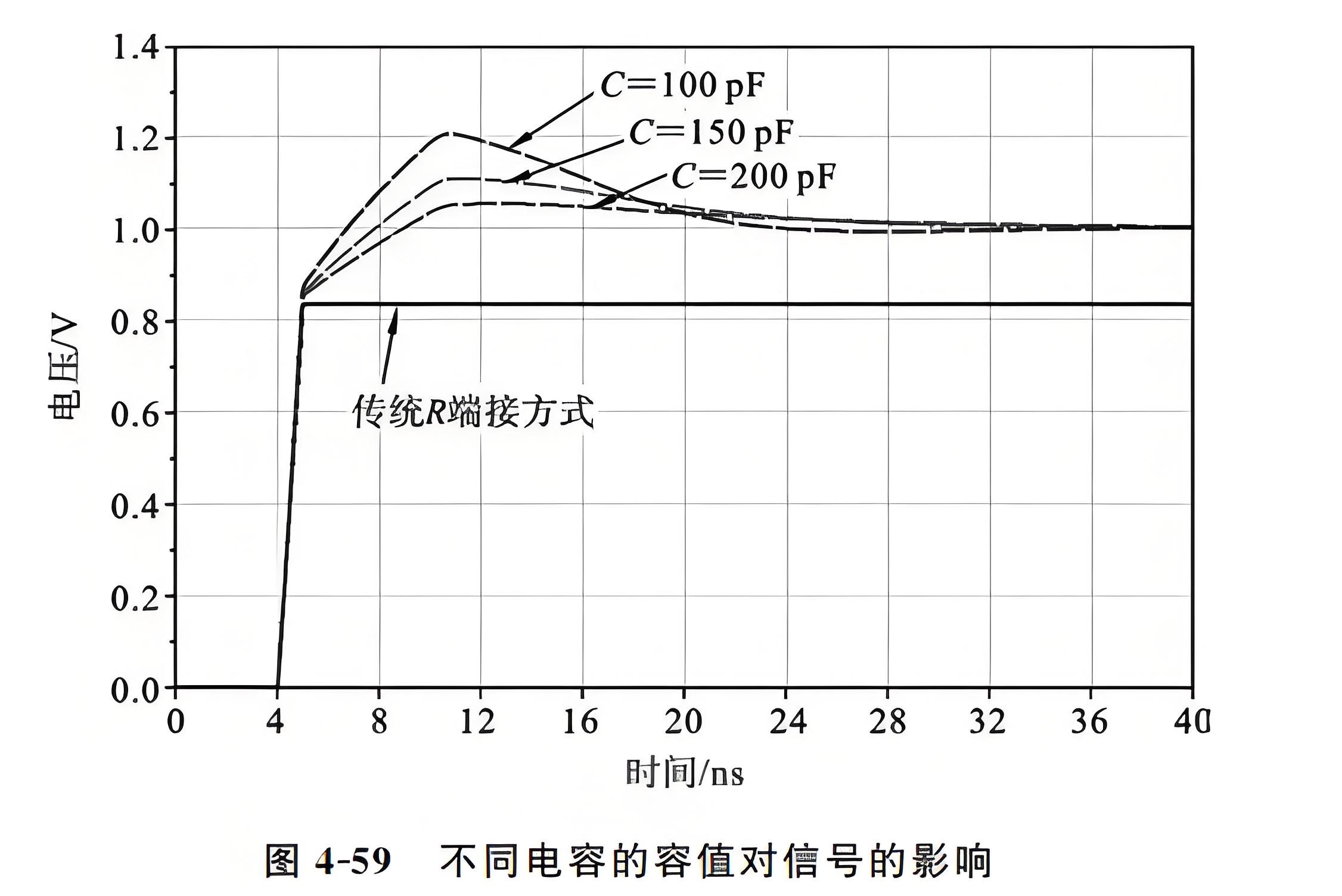

为实现阻抗匹配,R的电阻阻值也要等于传输线的阻抗值。而电容的容值对信号有什么影响呢?仿真结果如图4-59所示。

由图4-59可知,在端接电阻阻值一定的情况下,过冲的程度和电容的容值相关,电容越大,过冲的幅度越小,但相应的上升时间也就越慢。我们知道,电容是隔直通交的,上升沿到来时,电容的阻抗很低,相当于短路,于是端接电阻上有电流通过,电容起到端接的作用。一定时间后电压达到稳定,电容相当于断路,端接电阻也不再分压,此时稳定电压和输出电压相等。

RC端接最大的优点就是直流功耗较小,也不会拉低高电平的电压值,但是由于电容效应,信号中的高频分量会损失一部分,导致信号上升时间变缓,这会影响到系统的时序。所以我们在使用这种端接时一定要先进行仿真分析,确保端接对信号的影响在可以接受的范围内。

实际工程中,具体使用哪种端接方式,需要具体问题具体分析,信号性质不同,对信号质量的要求也不同,关键是要了解各种端接的特性,然后根据系统对信号的要求,酌情确定端接方案。

以上是对单线传输、点对点的端接方法做了基本介绍,真正意义上的高速信号都不能简单使用上面的端接方法,而是在这些端接方法的基础上要进行一些优化。有些芯片把这些端接电阻集成在芯片中,通过程序来控制这些端接的开启,例如,DDR颗粒自带的ODT功能,在了解了这些基本端接之后,再去学习这些片内端接就会容易得多。