PCIe(一)概述/拓扑/空间配置

一、PCI与PCIe总线

1.1 概述

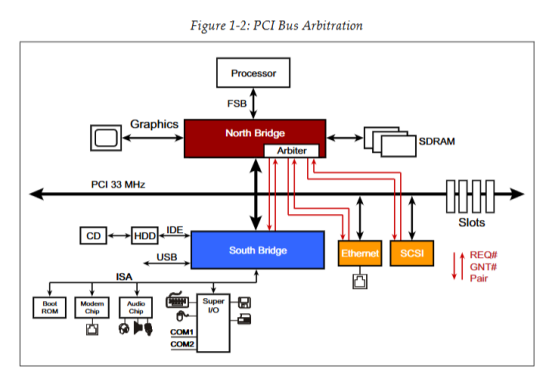

Peripheral Component Interconnect外围组件互联。PCIe总线是由PCI总线发展而来,多了个express,因此PCIe总线传输速度更快。PCI总线和PCIe总线都是属于局部总线,连接外部设备。在早期的PCI系统中,使用北桥来连接高速外围设备,负责核心系统通信,使用南桥来连接低速外设(如ISA总线,USB,SATA),管理中断控制器,时钟等系统信号。然而现代的PCIe架构将北桥集成到CPU中的根复合体中(Root Complex),南桥则被平台控制器中枢(PCH)取代。

1.2 基本特性

PCI总线是一种多设备共享的并行总线架构,有32位和64位两种。5v电压下时钟频率为33 MHz,此时 PCI总线的峰值带宽为133 MB/s(32位)或266 MB/s(64位)。3.3v电压下时钟频率为66 MHz, PCI总线的峰值带宽为266 MB/s(32位)或533 MB/s(64位)。

值得注意的是,PCIe是串行总线,使用差分信号以抗干扰,那为什么串行总线传输速率还要比并行传输要快呢?这是因为并行总线的多根信号线会存在time skew,必须要等到此次并行传输中最慢的一个信号被接收到,此次传输才算结束。其次并行总线依赖于外部时钟,为了保证接收端可靠采样,数据的传输延迟必须要小于一个时钟周期,如果总线变长,数据传输延迟势必会变大,这就需要更大的时钟周期,因此并行总线往往有频率上限。然而串行总线没有外部时钟,例如PCIe使用嵌入式时钟,时钟信息混在数据流中,不存在频率上限。

PCIe的多lane串行

PCI Express(PCIe)确实采用了串行点对点连接的设计,但其多Lane(通道)结构并非传统意义上的并行总线传输。

传统并行总线(如PCI/PCI-X)通过多根物理线路同时传输数据位,依赖同步时钟信号,易受信号偏移(skew)和时钟同步问题限制。

而PCIe的多Lane中每个Lane是独立的差分信号对(一对发送,一对接收),各Lane传输独立的串行数据流,无共享时钟。数据通过字节分割(Byte Striping)分散到各Lane,接收端通过Lane-to-Lane De-skew技术对齐数据,接收端需补偿各Lane的传输延迟差异。

二、拓扑结构

2.1 PCI拓扑结构

PCI采用的是总线型拓扑。多个PCI设备或者PCI桥设备共享该条PCI总线。设备通过#REQ信号请求总线使用权,由仲裁器(通常是在北桥)根据一些算法来进行响应#GNT。

2.2 PCIe拓扑结构

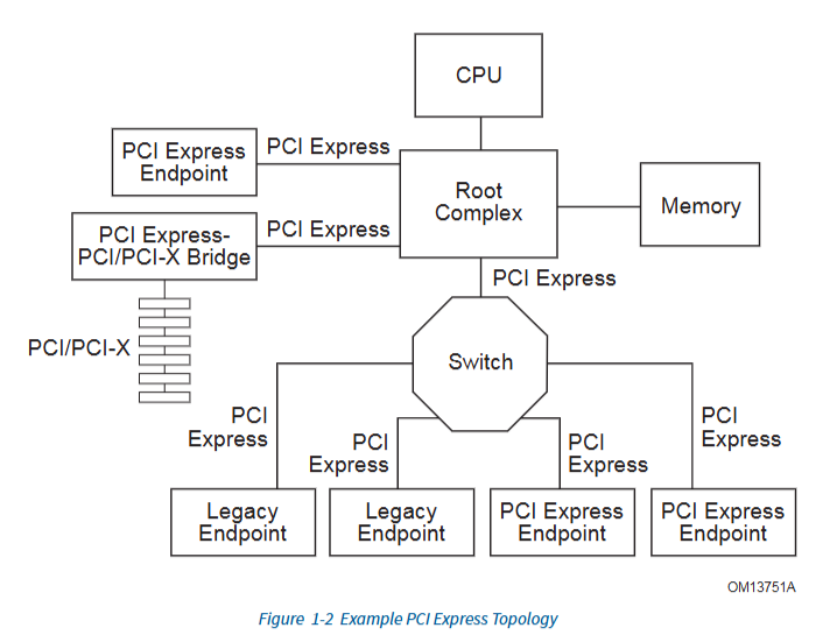

PCIe是树形结构,Root Complex位于拓扑的根部,一端与CPU相连,他通过根端口拓展出多个下游分支。Switch交换机作为内部节点可以聚合多个下游链路,提供更多的端口用以连接Endpoint,他可以连终端设备也可以连下游的switch,而桥接设备bridge是用于连接PCIe与其他总线的。

2.3 PCI设备标识

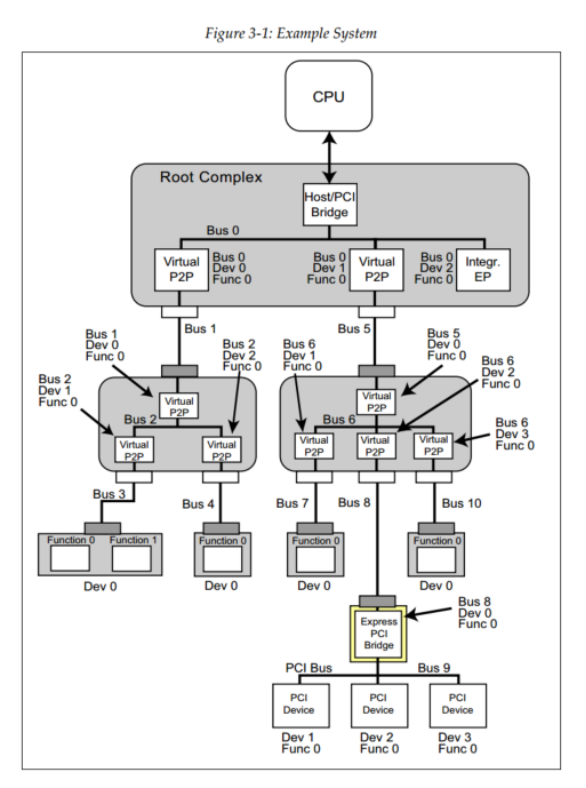

每个端点连接的PCI设备通过唯一的16位BDF(Bus:Device:Function)标识,Bus为8位,因此一个PCIe总线拓扑结构中,最多支持256级总线,Device为5位,因此每条总线最多挂载32个PCI设备。每个SW代表一级Bus,挂载在该SW下的所有PCIE设备(包括SW和EP)都属于这一级Bus。Function是3位

三、空间配置

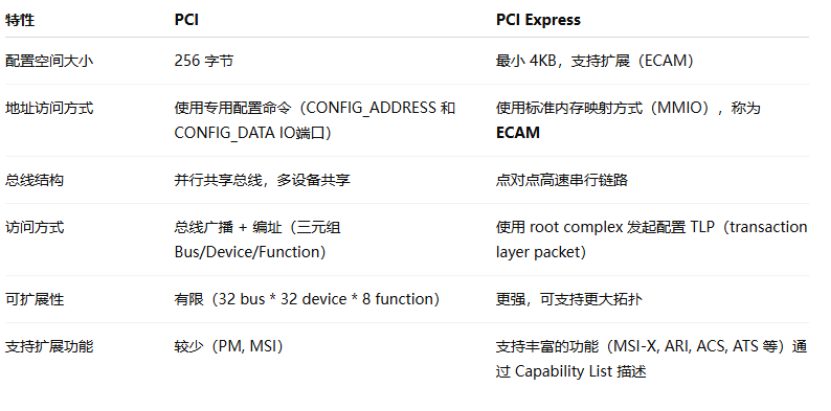

由于PCI/PCIe上挂了多个设备,而这些设备的资源(地址,IO,中断等)都必须统一管理以避免冲突,因此PCI规定,每个设备都必须有一个地址空间(PCI为256字节,PCIe为4KB)来存储设备信息、资源需求和系统分配的资源地址等。同时,PCIe 采用了内存映射(ECAM)和更丰富的扩展结构,解决了传统 PCI 配置空间扩展性差、访问效率低等问题。

3.1 PCI空间配置

256字节的配置空间中前64字节是强制的,剩余192是可选的。

枚举是PCI发现并启动某个PCI设备的方式

- 总线扫描

采用深度优先搜索(DFS)扫描每条总线的所有设备(Device 0-31)和功能(Function 0-7)。

通过读取Vendor ID(0x00)判断设备是否存在(非0xFFFF)。当确定该设备存在后,通过header type来判断是SW还是EP(EP的type为0,RC和SW的type为1)

- 设备配置

进行BAR初始化,桥设备配置,中断分配

- 树形拓扑构建

连接不同的总线,形成层次化拓扑,Root complex 连接总线0,发现桥设备后递归扫描下游的总线。

3.2 PCIe空间配置

PCIe的前64字节完全兼容PCI,后续空间仅PCIe支持,存放扩展功能(MSI/MSI-X PCI Express Capability(链路状态、宽度、速度) Power Management(PM) ARI、ACS、SR-IOV等)。

ECAM机制

Enhanced Configuration Access Mechanism。在 PCIe 中,配置空间不是通过 IO 端口访问,而是通过内存映射地址(MMIO)访问,这样可以让主机直接访问,并且可以挂载更多的设备。系统会保留一大段物理地址空间,专门用于 PCIe 配置空间。每个 PCIe Function 的 4KB 配置空间都被分配一个固定的内存地址,计算规则如下:

Address = ECAM_base + (Bus << 20) + (Device << 15) + (Function << 12)