4、程序的固化和下载(一)

目录

1 概述

2 ZYNQ 的启动

2.1 启动模式的设置

2.2 上电时序要求

2.3 ZYNQ 的启动流程

阶段 0:

阶段 1:

阶段 2:

3 纯 FPGA 工程下载

3.1 直接选择 bit 文件下载

step1:在打开的VIVADO软件界面,单击Open Hardware Manager。

step2:点击Auto Connect

step3:右键 FPGA 芯片信号选择 Program device 或者点击上方的 Program device 按钮

step4:选择对应的 Bit 文件

step5:点击Program下载完成

3.2 工程中下载对应 BIT 文件

step1:在打开的Vivado软件界面,单击Open Project。

step2:找到我们工程对应的***.xpr 文件

step3:点击 Open Target

step4:右键 FPGA 芯片信号选择 Program device 或者点击上方的 Program device 按钮

step5:选择对应的 Bit 文件

step6:点击Program下载完成

软件版本:vitis2021.1(vivado2021.1)

操作系统:WIN10 64bit

硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA

1 概述

基于 ZYNQ 的启动方式包括了 ZYNQ 的加载流程、支持的加载模式、裸机启动、LINUX 启动等。其中加载模式有常用的 JTAG 模式、QSPI 模式、SD 卡模式、NAND FLASH 模式、QSPI+EMMC 模式。如果需要详细了解其中的原理需要阅读大量资料和一些 XILINX 的 FSBL 代码以及 LINUX 启动部分的源码。

对于 SDK 开发的初级读者来说在刚开始入门的时候,掌握复杂的启动原理相对比较困难,所以对于初级读者关键还是掌握主要的启动模式方法、基本的启动流程原理,比如 QSPI 启动、SD 启动、如何制作 BOOT.BIN 文件的能力,满足一般的项目要求。对于需要更加深入掌握比如精简定制 fsbl、multiboot 方式、QSPI+EMMC 启动方式、JTAG 启动方式等,则可以详细阅读 ug585、ug821、阅读 fsbl 代码、分析 linux 中相关的 uboot 启动流程和参数设置。

2 ZYNQ 的启动

2.1 启动模式的设置

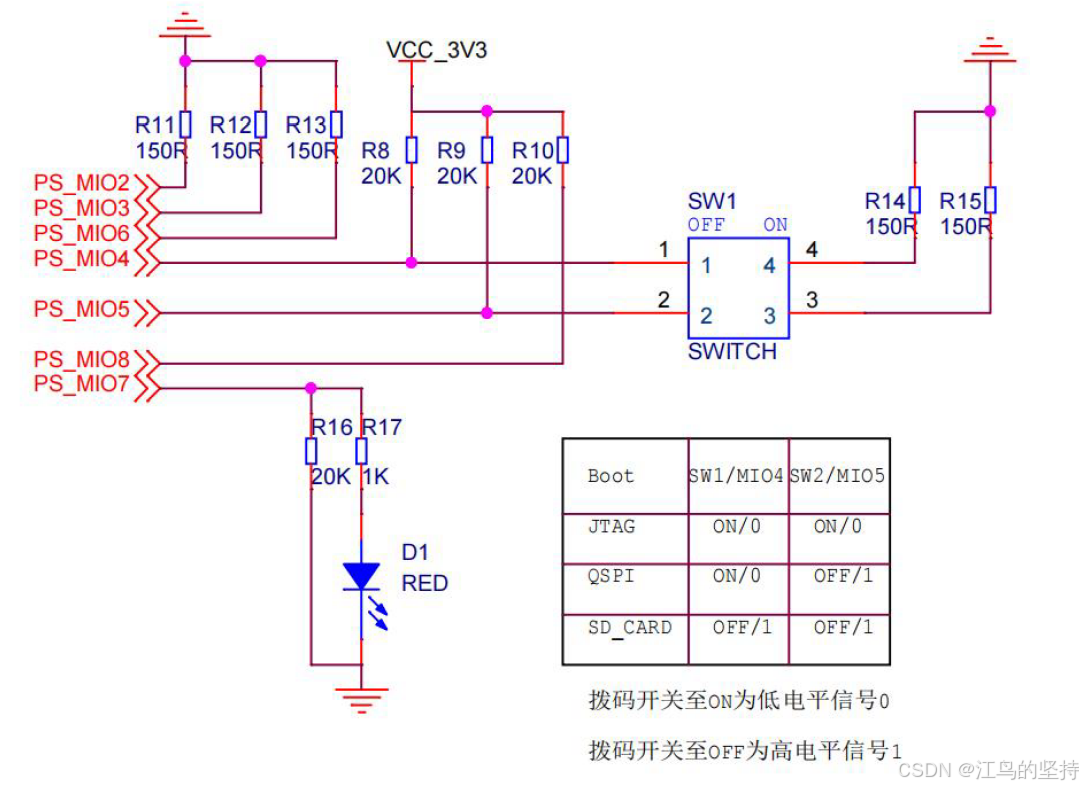

ZYNQ 支持 JTAG 启动模式、NOR BOOT 模式、NAND FLASH 启动模式、QSPI 启动模式、SD 卡启动模式。这里我们的硬件只支持 SD 卡启动模式、QSPI 启动模式、JTAG 启动模式。使用对应的启动模式前,请务必将开发板上的模式开关拨到对应模式的启动位置。

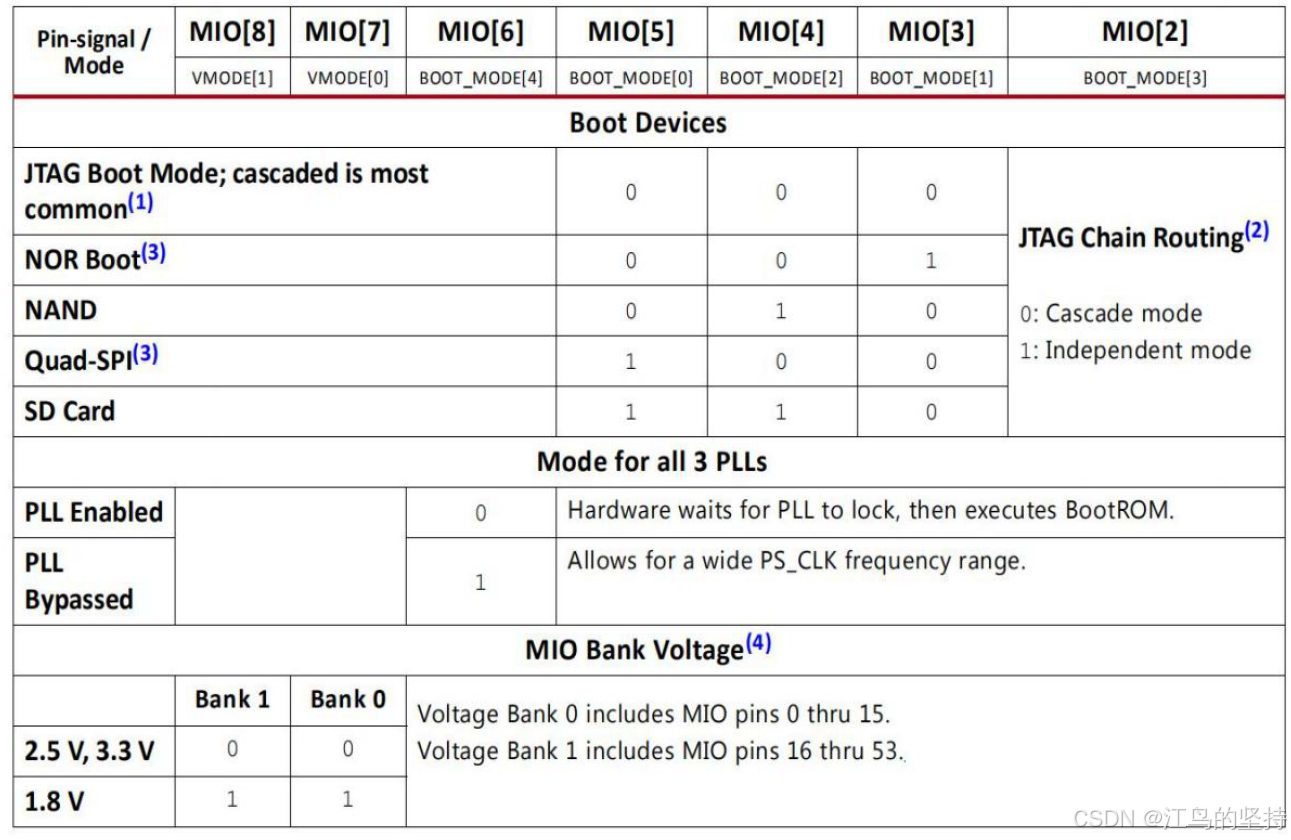

如下图1所示,MIO[8:2]为Zynq PS的IO引脚,已经引到芯片引脚上,通过对其配置便可以改变不同的启动方式 。

JTAG 启动模式

NOR BOOT 模式

NAND FLASH 启动模式

QSPI 启动模式

SD 卡启动模式

图1 启动模式配置

图2 启动外围电路图

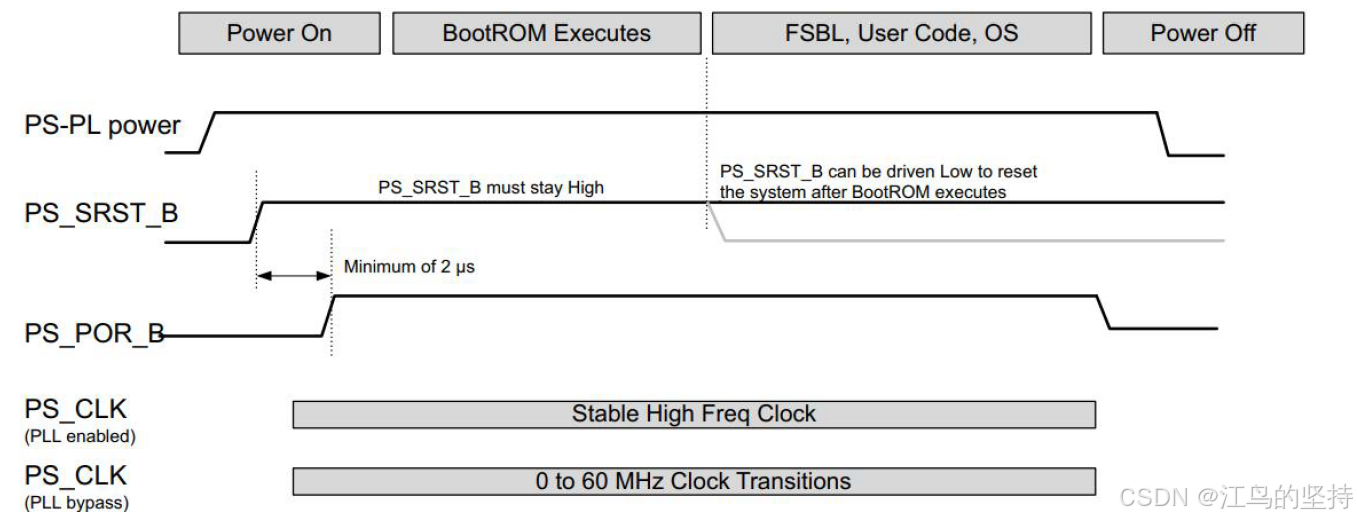

2.2 上电时序要求

上电需要满足 PS_POR_B 应该一直保持低电平,并且在 PS_SRST_B 引脚拉高 2us 后拉高。很多上电启动异常的情况应该排查电源的启动顺序顺序是否满足要求。

图3 启动时序图

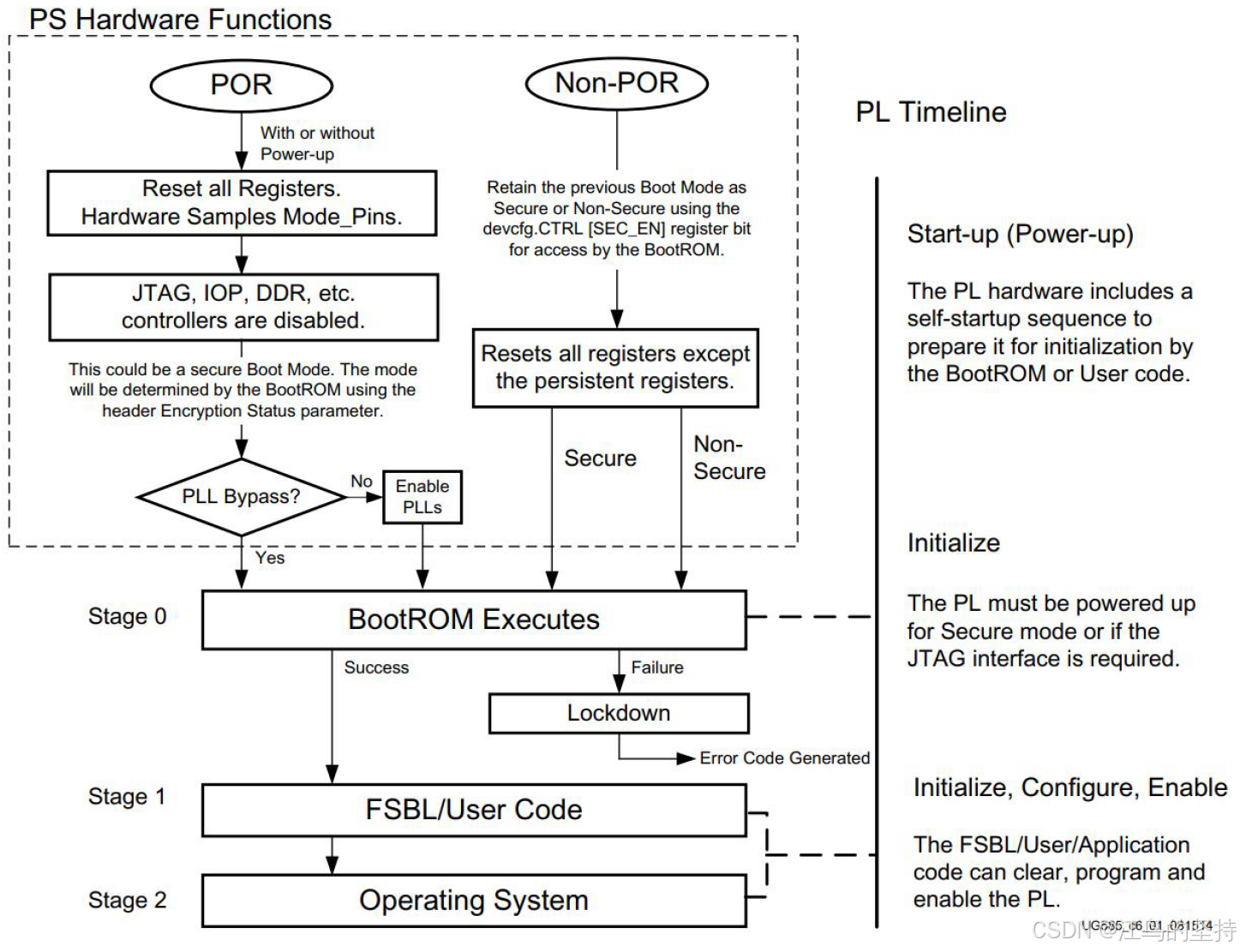

2.3 ZYNQ 的启动流程

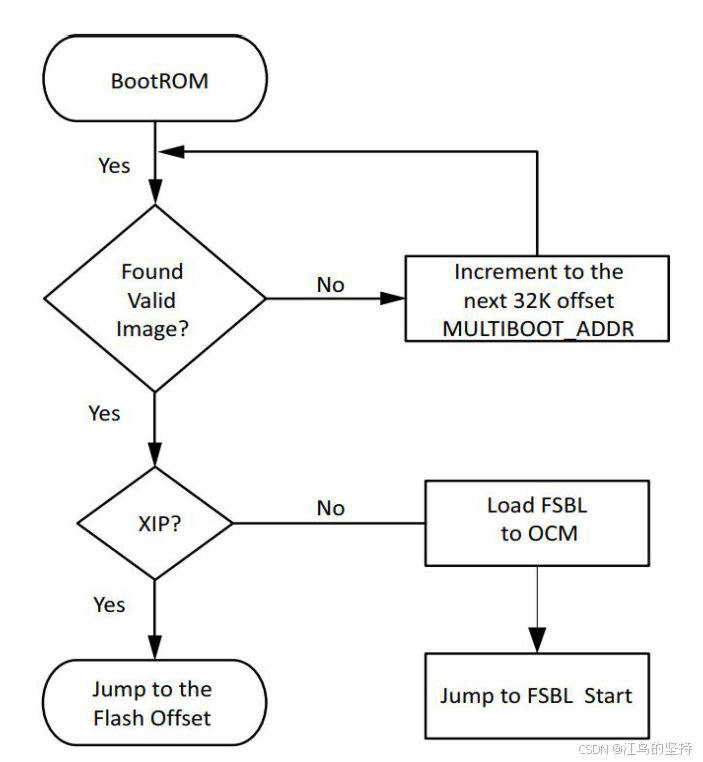

下图展示了 ZYNQ 上电复位或者非上电复位后,进入 BOOTROM 程序执行的状态框图。

图4 zynq启动流程图

-

阶段 0:

BootROM 中包含了一段芯片出厂前就带的启动代码,当上电复位 (POR) 或非 POR 系统复位(PS_SRST_B、调试、看门狗、软件)后, BootROM 程序在主 CPU (CPU 0) 上开始执行。BootROM 程序读取外部存储器中的BOOT.BIN 文件,并且查找其中的 BootROM Heard 参数,以确认程序如何切换到下阶段 1。如果是 QSPI FLASH 中没有找到 BOOT.BIN 文件,BootROM 会跳到下一个 32KB 的位置重新搜索 BOOT.BIN

在以下流程图中,展示了第一个阶段的复制 FSBL 到 OCM 的流程图。其中 XIP 模式我们这里不涉及。

图5 复制 FSBL 到 OCM 的流程图

-

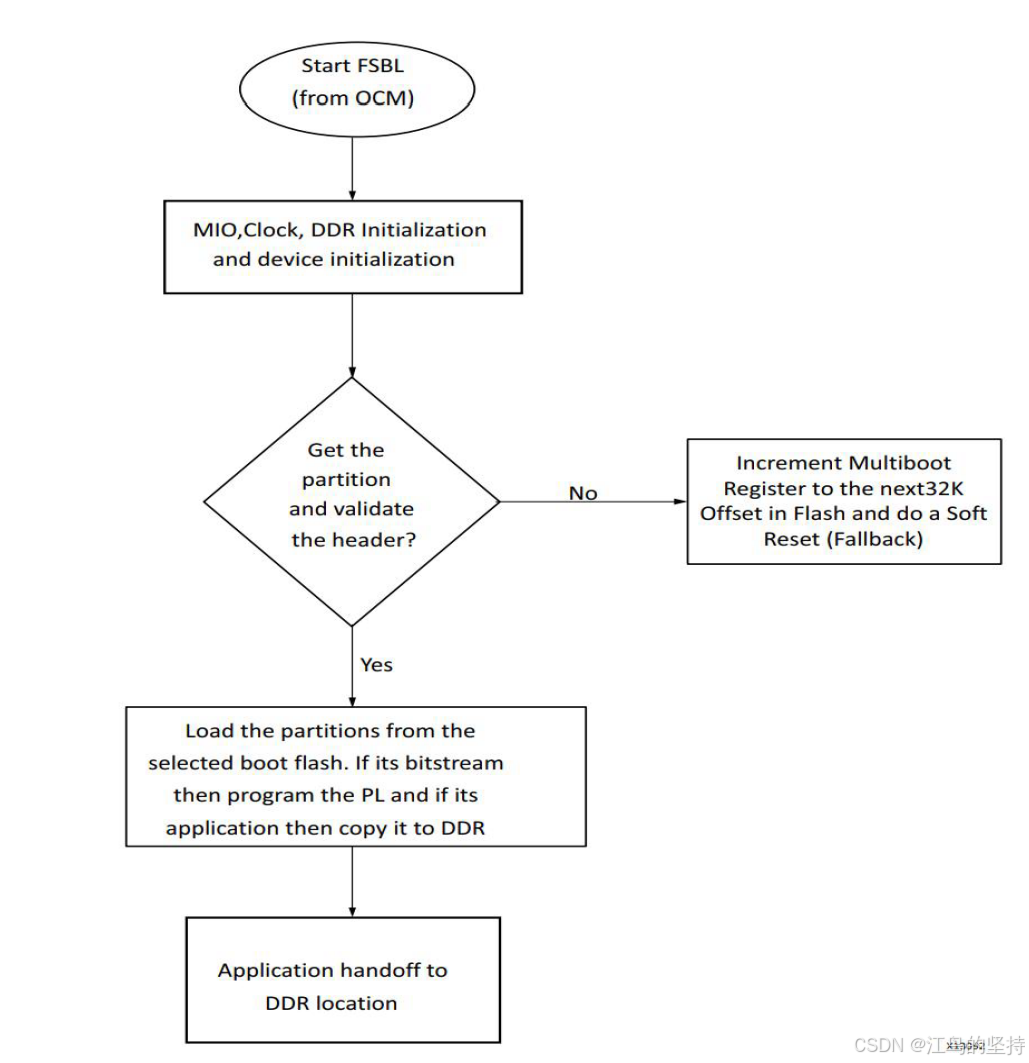

阶段 1:

阶段 0 把 FSBL 拷贝到 OCM(On-chip memory)中后,CPU0 开始从 OCM 运行 FSBL 代码。包括:

1:初始化 PS 的配置参数包括 MIO、DDR 等

2:使用 BIT 流对 PL 进行编程

3:加载第二阶段的引导程序或者裸机程序到 DDR 存储器中

4:阶段到阶段 2

图6 1阶段流程图

阶段 2:

该阶段一般运行的是应用程序比如裸机的应用程序、或者 LINUX 的 boot.elf。也可能是第二阶段引导程序,比如 QSPI+EMMC 模式,从 QSPI 完成 fsbl 加载后可以对 eMMC 分区识别,把剩余的加载项放到 EMMC 中,这样只需要一个很小的 QSPI FLASH 就可以了。当然一般我们开发板都采用了足够达的 QSPI FLASH,一般不需要这么节约使用。等 LINUX 部分我们再探讨这方面的问题。

3 纯 FPGA 工程下载

3.1 直接选择 bit 文件下载

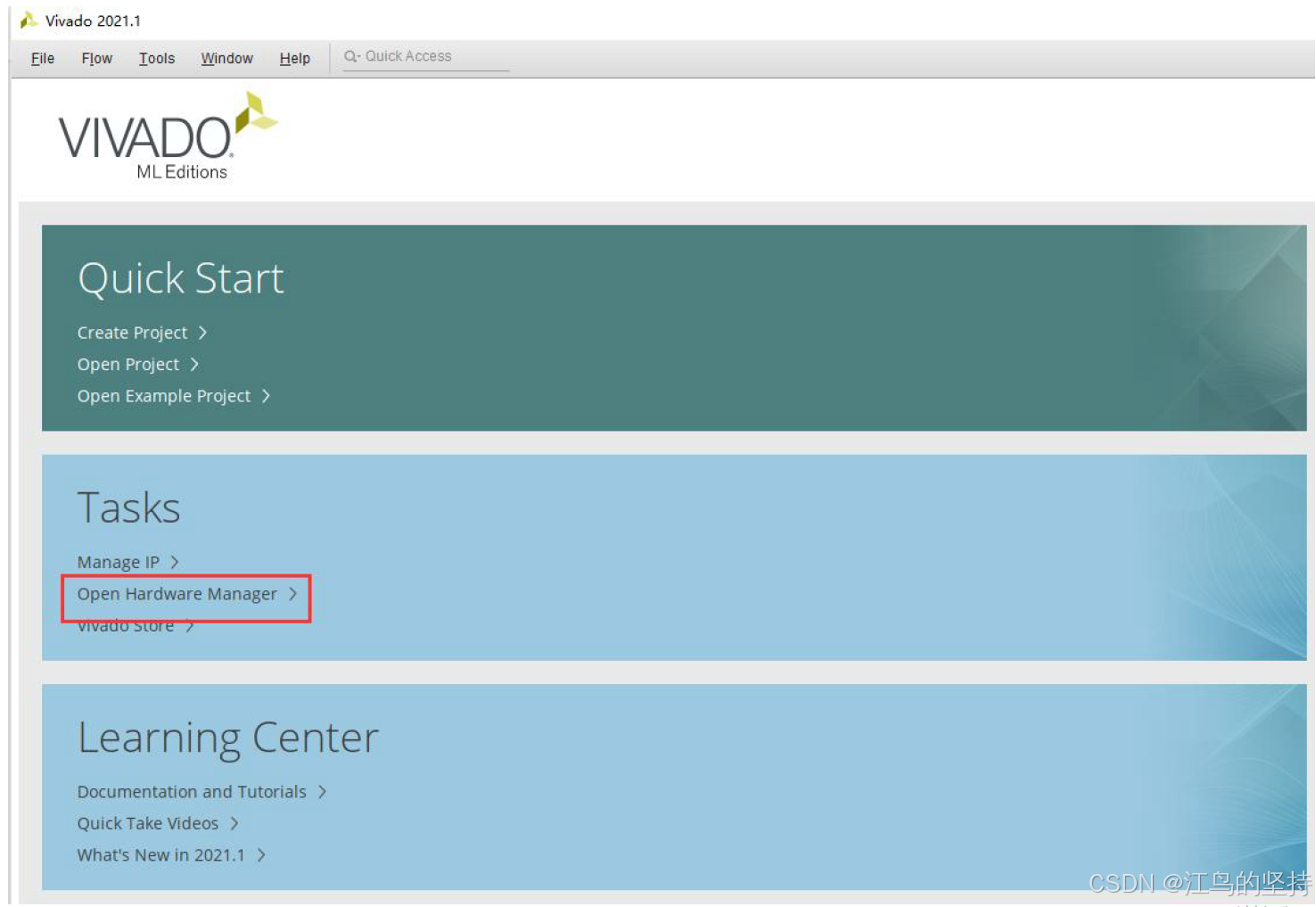

很多时候我们仅仅是想测试一下代码的功能,或者是我们有多个 Bit 文件下载的时候,我们不需要打开相应的工程,仅仅打开我们的 VIVADO 软件便可以下载我们的 Bit 文件。

step1:在打开的VIVADO软件界面,单击Open Hardware Manager。

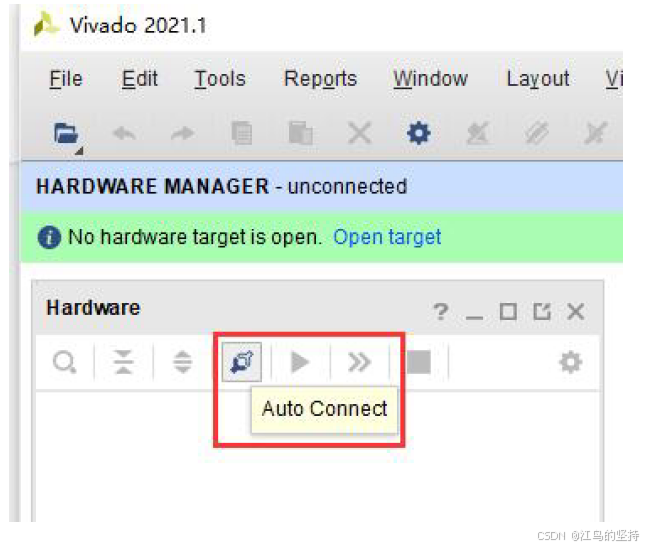

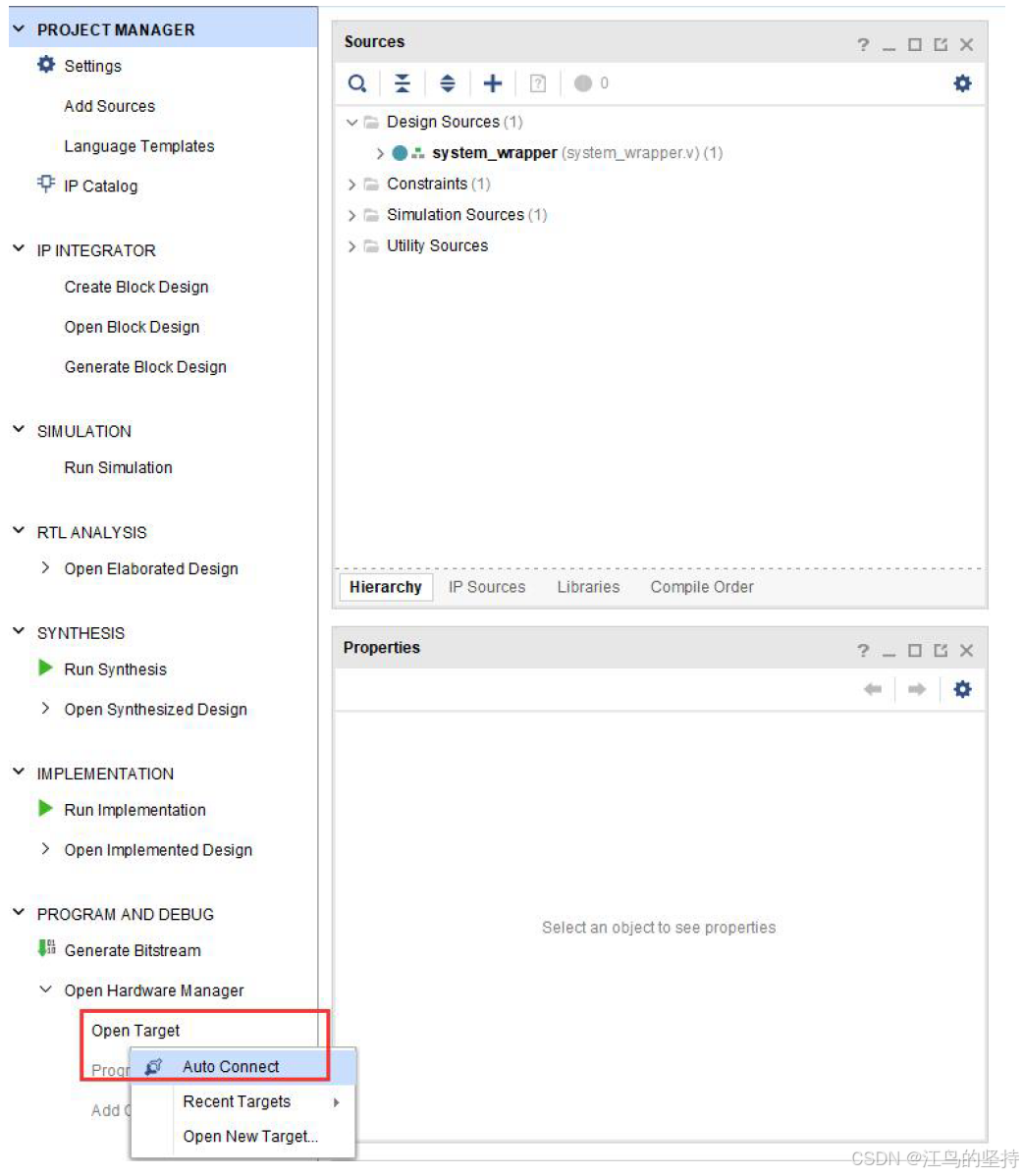

step2:点击Auto Connect

在此之前,请确保开发板拨码开关为JTAG模式,且开发板已上电。

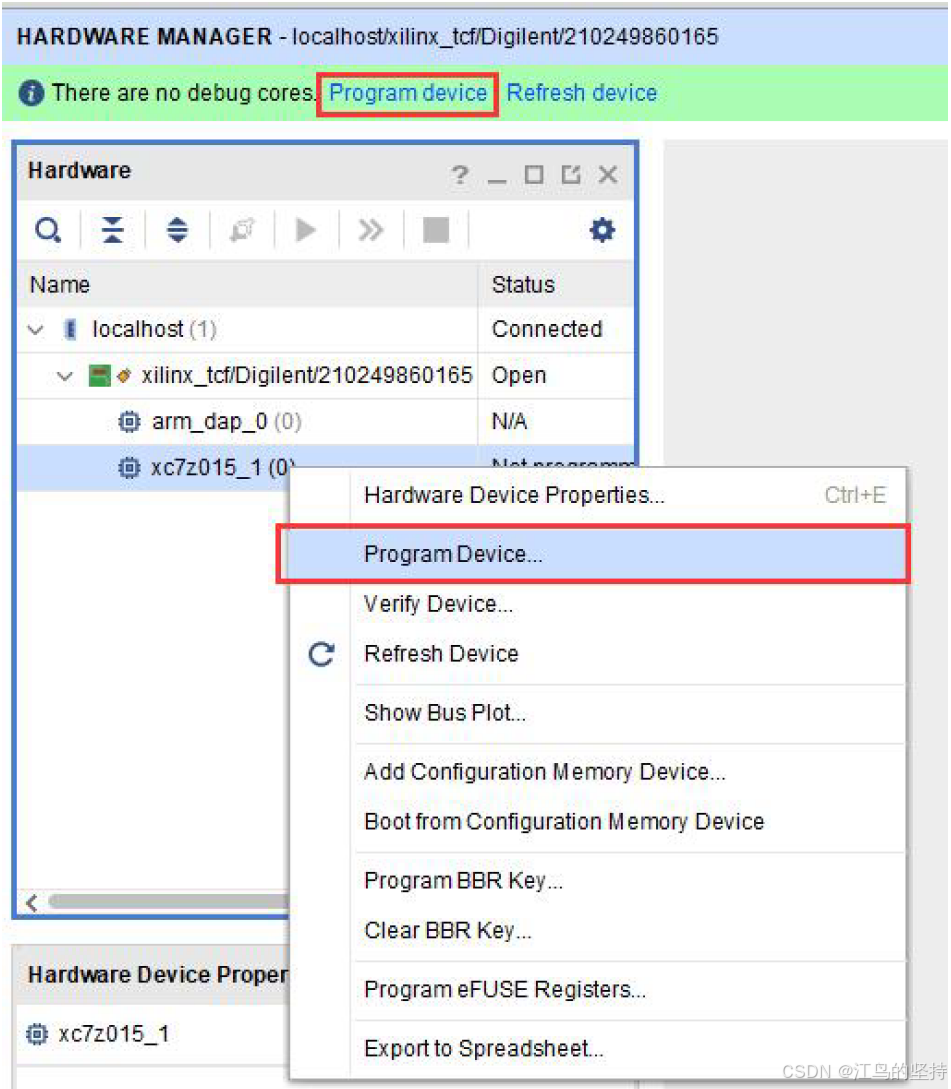

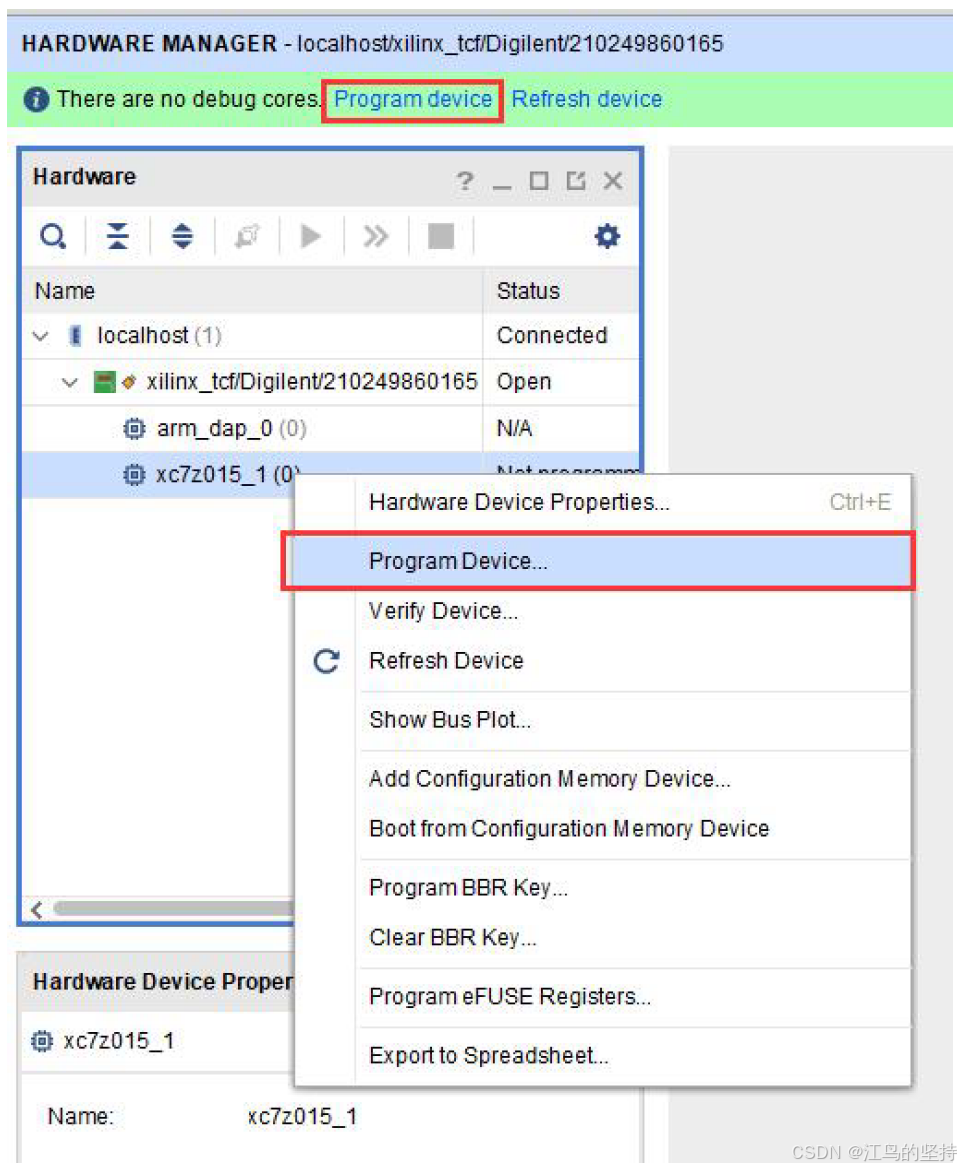

step3:右键 FPGA 芯片信号选择 Program device 或者点击上方的 Program device 按钮

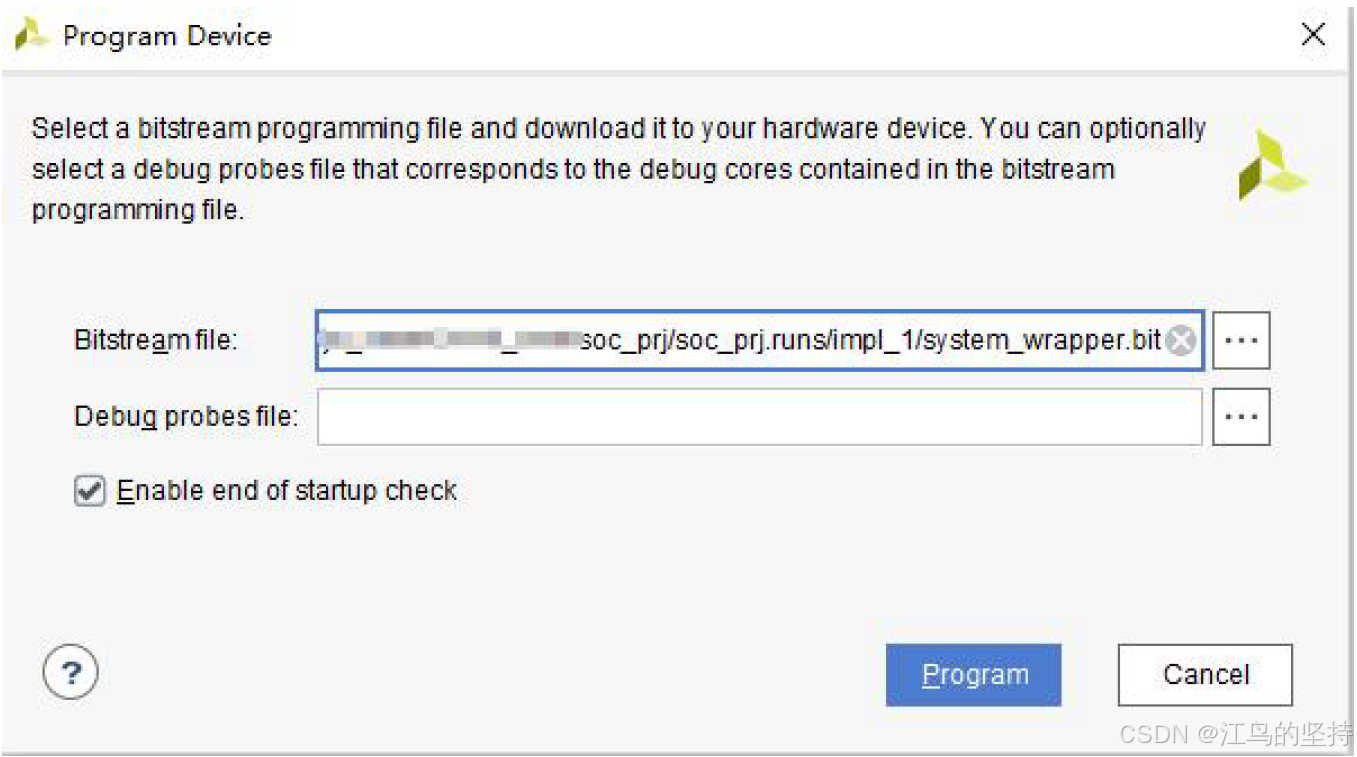

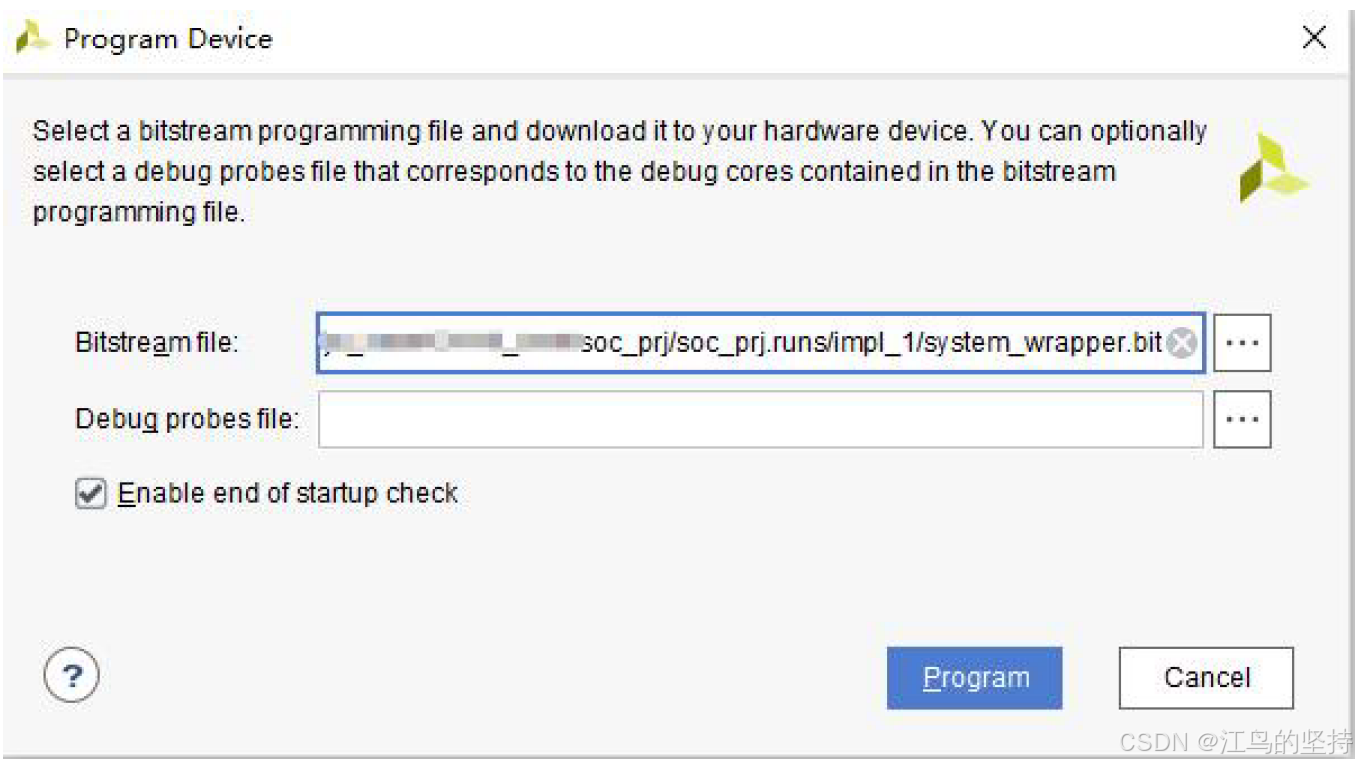

step4:选择对应的 Bit 文件

如果你在工程中有使用在线逻辑分析仪的话,会在下方自动添加.ltx 文件。如果 ltx 文件与 bit 文件不匹配,会报错。

注意图片中的文件目录,一般我们工程默认的Bit文件就是生成在该路径下

step5:点击Program下载完成

3.2 工程中下载对应 BIT 文件

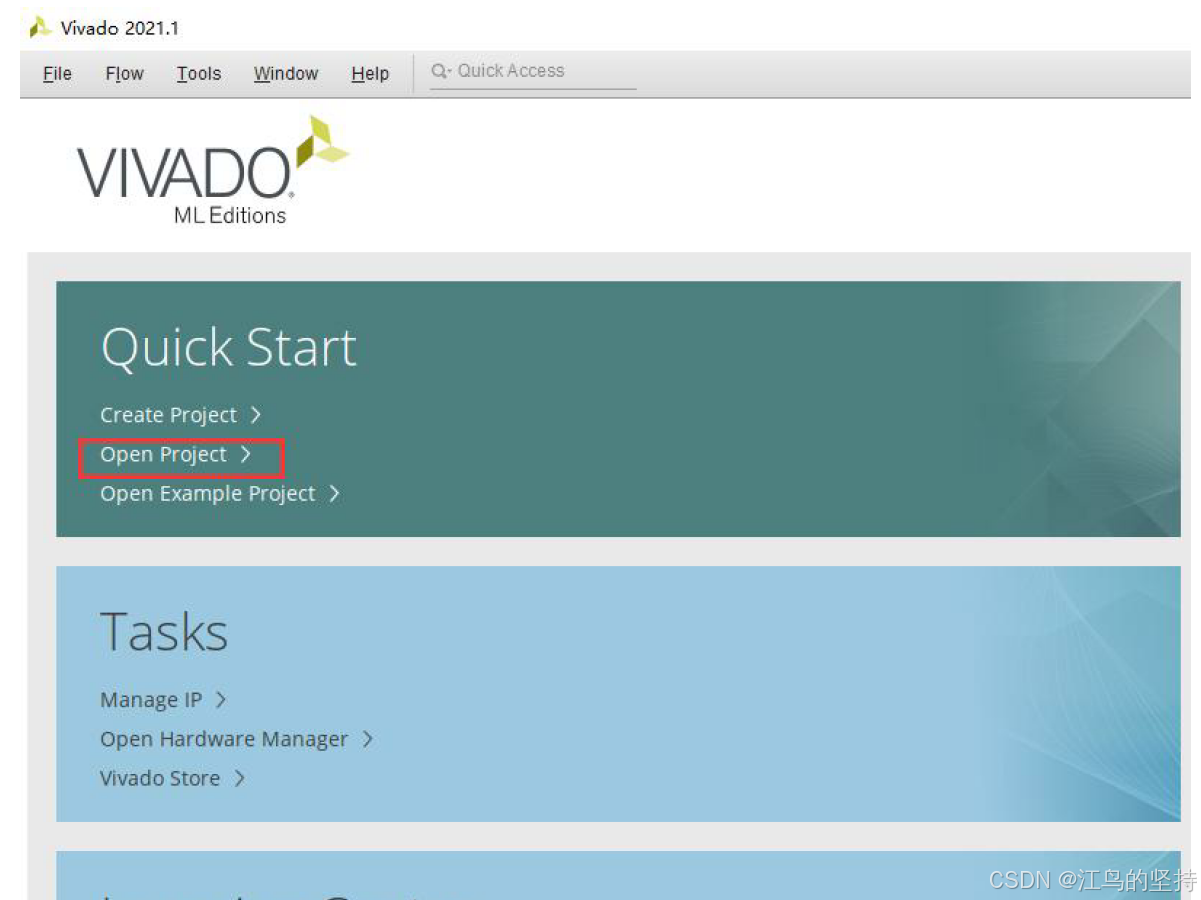

step1:在打开的Vivado软件界面,单击Open Project。

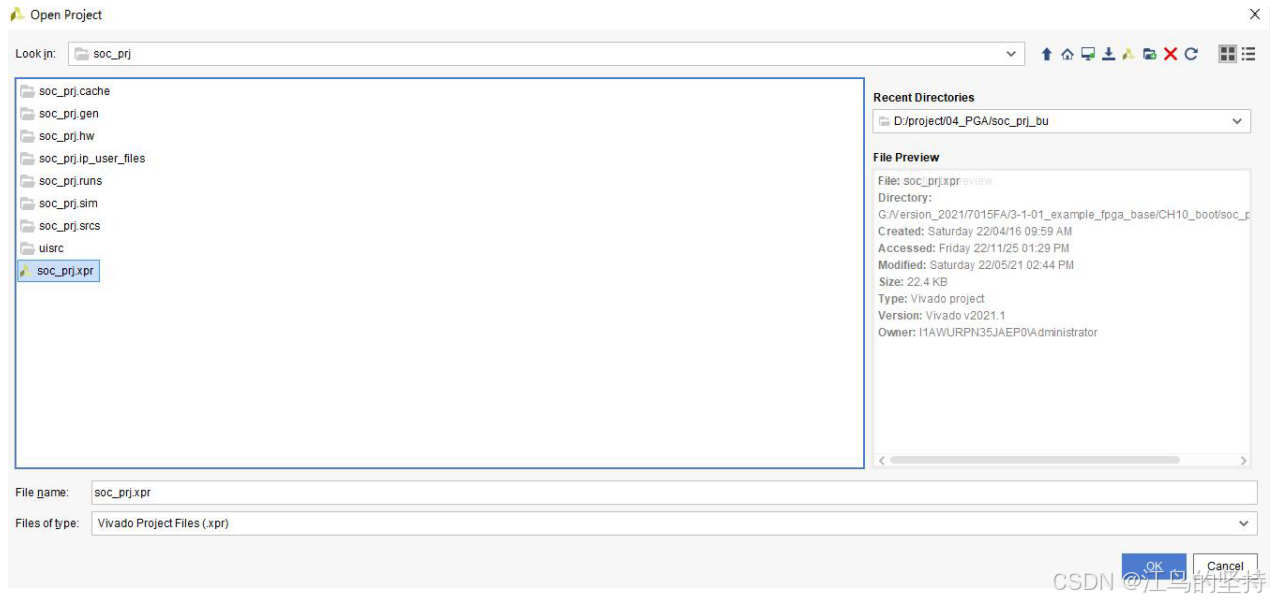

step2:找到我们工程对应的***.xpr 文件

step3:点击 Open Target

选择 Auto Connect,在此之前,请确保开发板拨码开关为 JTAG 模式,且开发板已上电。

step4:右键 FPGA 芯片信号选择 Program device 或者点击上方的 Program device 按钮

step5:选择对应的 Bit 文件

如果你在工程中有使用在线逻辑分析仪的话,会在下方自动添加.ltx 文件。如果 ltx 文件与 bit 文件不匹配,会报错。

注意图片中的文件目录,一般我们工程默认的Bit文件就是生成在该路径下

step6:点击Program下载完成

看上一篇:3、Xilinx USB JTAG 仿真下载器驱动安装

看下一篇:4、程序的固化和下载(二)