从走线到互连:优化高速信号路径设计的快速指南

从物联网网关和边缘设备到数据中心服务器和网络基础设施卡,几乎所有类型设备的设计人员都面临着压力,他们需要更快地将更多数据移入、移出和移出其系统。

如今价格实惠的高速 IC 使设计人员能够轻松扩展系统速度以满足最终用户的需求。在纸面上。在电路板上以及整个系统的互连过程中,共模噪声、串扰以及信号路径阻抗和谐振引起的损耗等影响可能会挑战 Gbit/s 及以上速度下信号的完整性。

这些不良影响的原因包括耦合、外部噪声源和互连的物理特性。尽管这些在较低速度下通常可以忽略不计,但在设计和布置信号路径以处理高速信号时必须更加小心。

高速编码方案的日益普及有望维持数 GB 数据速率的上升趋势。由于熟悉的两级 NRZ(不归零)信令在远高于 28Gbps 的数据速率下会遇到物理限制,而四级 PAM4 信令可处理 56Gbps 或更高速率,是未来 200G 和 400G 以太网速度的关键推动因素。

用于信号完整性的互连设计

差分信号广泛用于高速系统,以消除耦合到信号线上的外部噪声的影响。信号路径对的布局(包括路径长度和间距)可能会对信号完整性产生关键影响。paths 应尽可能短,并且通常需要 trace length matching,但不适用于包含嵌入式 clock 信号的 PCIe 等标准。高速互连(如 USB3.0、HDMI 等)的设计指南通常提供建议的最大走线长度、信号对和其他信号走线之间的间距以及时钟信号的间距等信息。

5S 或 5W 经验法则通常用于计算适当的线对间距,并要求间距至少为走线宽度的五倍。虽然信号对通常间隔很近,但重要的是要确保沿走线全长的间距一致,以防止差分阻抗的变化会损害信号完整性。一致的间距还有助于保持差分对的磁场抵消效果,从而最大限度地减少电磁辐射(辐射 EMI)。

互连设计指南还提供了有关电路板叠层的宝贵信息。将高速信号走线限制在上层,避免使用在信号路径中引入额外电感的过孔。HDMI 指南建议在上部信号平面和相邻接地层之间间隔 125-250 微米。非高速信号应在较低层布线,以最大限度地与高速信号分离。这至少需要一个四层叠层。

还建议在固体接地平面金属上布线,围绕空隙或平面分割等特征进行布线。至少 1.5 倍走线宽度的间隙可以防止高频信号电流与接地层中的不连续性相互作用,否则会导致信号干扰、EMI 增加和传播延迟。高速布线还应避免使用晶体、振荡器和开关电源稳压器等元件,电路板设计人员还应避免将探针或测试点放置在高速走线上。

连接器选择和安装

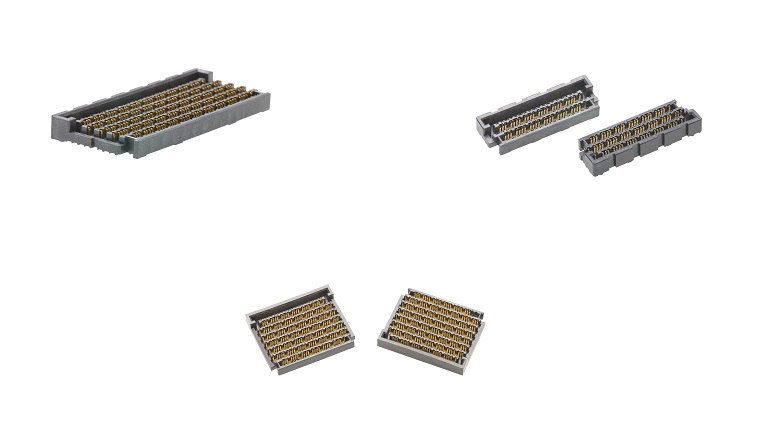

| Molex Mirror Mezz 连接器 |

在高速信号路径中引入元件和连接器时,通常首选表面贴装。当高速信号在上层布线时,可以直接进行连接,无需过孔。如果需要过孔,要从较低层连接,可能需要背钻,以防止未使用的金属充当信号路径中的短截线,这可能会导致信号严重衰减。

如果要将高速信号从电路板上传输到相邻的电路板或通过电缆传输到系统的另一部分,则这些组件将成为信号路径的一部分,必须像电路板设计一样仔细考虑。不适当的连接器选择或设计不佳的电缆组件会导致不匹配、谐振和干扰重新渗透到系统中。

专为高速应用设计的连接器包含有助于保持信号完整性的功能。一个例子是 Molex Mirror Mezz 系列高密度可堆叠板连接器,数据速度高达 56Gbps。这些连接器采用经济高效的球栅阵列 (BGA),用于表面贴装连接,提供接地-信号-信号-接地 (GSSG) 引脚排列,非常适合差分信号。

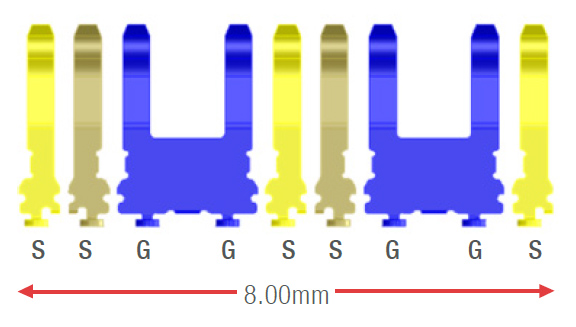

| Molex Mirror Mezz GSSG 引脚序列,具有更宽的接地引脚 |

GSSG 序列通常用于保持高速信号完整性。接地连接的布置是为了将差分对与其他传输线隔离开来。在 Mirror Mezz 连接器中,接地引脚特别宽,以提供增强的屏蔽并有助于平衡电场。某些型号提供开放式引脚字段行,采用偏移 GSSG 引脚布局,在 8.10mm 间距上提供 9 个信号引脚,并支持高达 17GHz 的差分信号。信号引脚经过电气调谐,可实现高信号完整性,其形状可最大限度地减少相邻行之间的串扰。

同时,机械设计旨在确保可靠的电气连续性。端子的设计消除了端子的提升和振动。配接时有两个接触点,仔细管理力和擦拭区域,在受到高振动或连接器部分未配接时保持接合。Mirror Mezz 还提供专用的柔性电缆链路,这些链路具有受控通道和引脚接地功能,可在灵活架构中连接电路板时保持信号完整性。

还值得注意的是,Mirror Mezz 连接器的高密度使设计人员能够在相对较小的电路板区域内连接大量信号对,从而实现较大的总互连带宽。

连接器和电缆系统

| Molex Nano-Pitch 电缆组件 |

电缆互连也容易受到信号衰减的影响。系统解决方案(如 Molex iPass 互连系统)包括用于内部和外部应用的连接器和电缆组件。主机连接器专为高达 14Gbps 的应用而设计,采用表面贴装设计,可放置在 PCB 的任一侧,使工程师能够充分利用电路板。电缆旨在提供严格的偏斜控制和低串扰。该系统非常适合服务器存储应用,具有用于串行连接 SCSI (SAS)、串行 ATA (SATA)、串行快速 I/O (SRIO) 和以太网的标准外部电缆,具有最小化外部插头宽度并协助电缆管理的功能。

Nano-Pitch I/O 连接器系统更小,非常适合移动应用以及存储系统、主机总线适配器 (HBA) 服务器以及网络交换机和路由器。这些插座采用交错的双排触点,可在紧凑的封装内为高速走线连接提供最佳布线。GSSG 引脚排列旨在以较小的外形尺寸最大限度地增加高速通道的数量,包括 4 通道和 8 通道行业标准尺寸。该系统适用于高达 25Gbps 的应用,兼容所有 PCIe、SAS 和 SATA 协议,并支持 PCIe Gen 4 和 SAS 4。

结论

高速系统硬件的设计人员必须采用最佳实践来确保在 Gbps 及以上速度下具有适当的信号完整性。从 PCB 布局开始,需要仔细设计整个信号路径,包括为预期遇到的信号速度选择合适的连接器和电缆。