电路笔记(元器件):并串转换芯片 SN65LV1023A 10:1 LVDS 串行器/解串器变送器 100 至 660Mbps

目录

- LVDS接口芯片SN65LV1023A

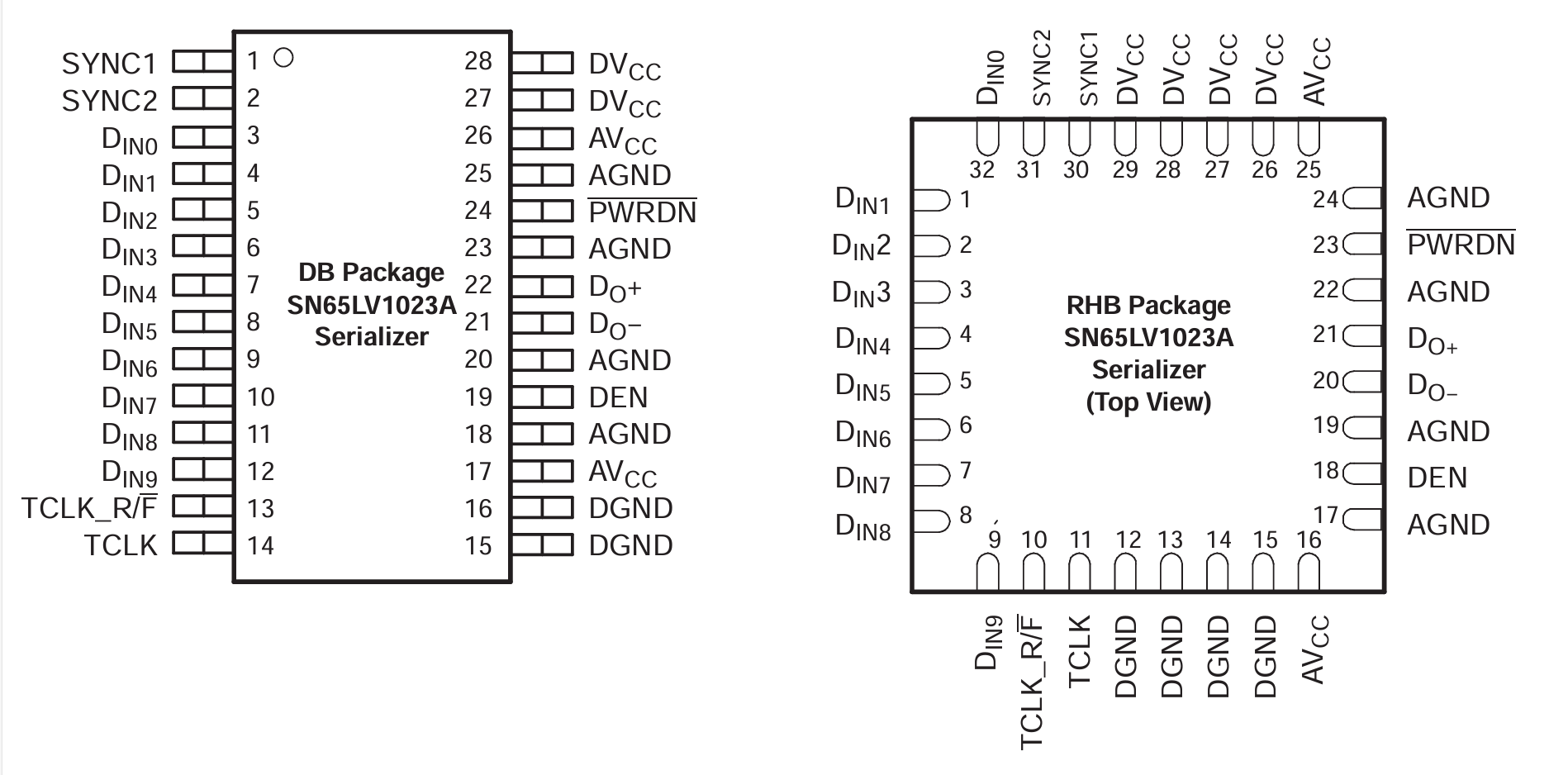

- 封装和引脚说明

- 引脚功能表(PIN FUNCTIONS)

- 串行器(SERIALIZER)芯片

- **解串器(DESERIALIZER)芯片**

- 功能框图

- FUNCTIONAL DESCRIPTION

- INITIALIZATION MODE

- SYNCHRONIZATION MODE

- RMT

- DATA TRANSMISSION MODE

- POWERDOWN

- HIGH-IMPEDANCE MODE

- 故障安全偏置 FAILSAFE BIASING FOR THE SN65LV1224B

- CG

LVDS接口芯片SN65LV1023A

-

SN65LV1023A 串行器和 SN65LV1224B 解串器组成了一个 10 位的 SerDes 芯片组,旨在通过 LVDS 差分背板以等效并行字速率(从 10 MHz 到 66 MHz)传输和接收串行数据。包括开销在内,这对应的串行数据速率为 120 Mbps 到 792 Mbps 的有效编码吞吐量。

-

上电后,芯片组链路可以通过同步模式进行初始化,该模式使用内部生成的 SYNC 模式;或者也可以允许解串器对随机数据进行同步。通过使用同步模式,解串器能够在规定的较短时间内建立锁定。

-

当不需要数据传输时,器件可以进入省电状态。或者,也可通过一种模式将输出引脚置于高阻态,而不会失去 PLL 锁定。SN65LV1023A 和 SN65LV1224B 的工作环境温度范围为 –40°C 到 85°C。

封装和引脚说明

引脚功能表(PIN FUNCTIONS)

串行器(SERIALIZER)芯片

| 引脚号 (DB 封装) | 引脚号 (RHB 封装) | I/O 类型 | 描述 |

|---|---|---|---|

| 18,20,23,25 | 17,19,22,24 | - | AGND:模拟电路地(用于 PLL 和模拟电路) |

| 17,26 | 16,25 | - | AVCC:模拟电路电源(PLL 和模拟电路供电) |

| 19 | 18 | 输入 | DEN:输出使能。高电平使能串行数据输出;低电平使 LVDS 串行输出进入高阻态。 |

| 15,16 | 12,13,14,15 | - | DGND:数字电路地 |

| 3–12 | 32,1–9 | 输入 | DIN0–DIN9:并行 LVTTL 数据输入 |

| 21 | 20 | 输出 | DO−:LVDS 差分输出(反相) |

| 22 | 21 | 输出 | DO+:LVDS 差分输出(非反相) |

| 27,28 | 26,27,28,29 | - | DVCC:数字电路电源 |

| 24 | 23 | 输入 | \bar{PWRDN}:电源关断控制。低电平关闭 PLL 并将输出置于高阻态,使器件进入低功耗模式。 |

| 1,2 | 30,31 | 输入 | SYNC1/SYNC2:同步信号输入(两者逻辑或)。当至少一个引脚在 TCLK 的 6 个周期内为高电平时,串行器开始发送最少 1026 个 SYNC 模式。如果在完成 1026 个模式后仍保持 SYNC 为高,则继续发送直到 SYNC 变低。若 SYNC 保持高超过 6 个周期,则再次启动 1026 个 SYNC 模式的发送。 |

| 13 | 10 | 输入 | TCLK_R/F:时钟边沿选择。低电平选择 TCLK 下降沿作为数据选通信号;高电平选择上升沿。 |

| 14 | 11 | 输入 | TCLK:LVTTL 电平参考时钟输入。SN65LV1023A 支持 10MHz 至 66MHz 的时钟。TCLK 用于锁存并行输入数据,并为 PLL 提供参考频率。 |

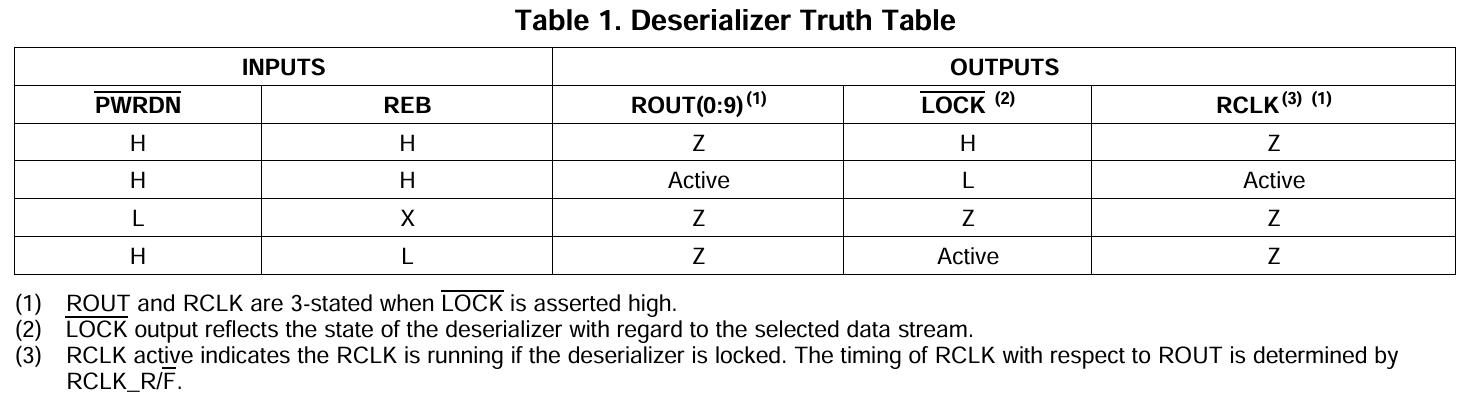

解串器(DESERIALIZER)芯片

| 引脚号 (DB 封装) | 引脚号 (RHB 封装) | I/O 类型 | 描述 |

|---|---|---|---|

| 1,12,13 | 10,11,28,29,30 | - | AGND:模拟电路地(用于 PLL 和模拟电路) |

| 4,11 | 1,8,9 | - | AVCC:模拟电路电源(PLL 和模拟电路供电) |

| 14,20,22 | 12,13,19,21 | - | DGND:数字电路地 |

| 21,23 | 20,22 | - | DVCC:数字电路电源 |

| 10 | 7 | 输出 | LOCK:锁相环锁定指示信号。当解串器 PLL 锁定到嵌入时钟边沿时变为低电平。 |

| 7 | 4 | 输入 | PWRDN:电源关断控制。低电平关闭 PLL 并将输出置于高阻态,使器件进入低功耗模式。要进入关断状态,此引脚需至少保持低电平 16ns。只要 PWRDN 保持低电平,器件就处于关断状态。 |

| 2 | 31 | 输入 | RCLK_R/F:接收时钟边沿选择。低电平选择 RCLK 下降沿作为数据选通信号;高电平选择上升沿。 |

| 9 | 6 | 输出 | RCLK:恢复出的时钟信号。用于锁存 ROUTx 输出数据。 |

| 3 | 32 | 输入 | REFCLK:LVTTL 电平参考时钟输入。用于内部 PLL 频率参考。 |

| 8 | 5 | 输入 | REN:输出使能。低电平使 ROUT0–ROUT9 和 RCLK 进入高阻态。 |

| 5 | 3 | 输入 | RI+:串行数据输入。LVDS 差分输入(非反相) |

| 6 | 2 | 输入 | RI−:串行数据输入。LVDS 差分输入(反相) |

| 28–24,19–15 | 27–23,18–14 | 输出 | ROUT0–ROUT9:并行 LVTTL 数据输出 |

功能框图

FUNCTIONAL DESCRIPTION

- SN65LV1023A 和 SN65LV1224B 是一个 10 位串行器/解串器芯片组,设计用于以 10 MHz 到 66 MHz 的时钟频率,通过差分背板或非屏蔽双绞线(UTP)传输数据。该芯片组具有五种工作状态:初始化模式、同步模式、数据传输模式、省电模式和高阻模式。以下各节将分别介绍每种工作状态。

INITIALIZATION MODE

- 在开始数据传输之前,必须先对这两个器件进行初始化。初始化是指将串行器和解串器的锁相环(PLL)与本地时钟进行同步。

- 当电源电压 VCC 施加到串行器或解串器时,相应的输出进入高阻态,同时片上上电电路会禁用内部电路。当 VCC 达到 2.45 V 时,每个器件中的锁相环(PLL)开始锁定到本地时钟。对于串行器而言,本地时钟是由外部提供的发送时钟(TCLK);对于解串器,则必须在 REFCLK(内部 PLL 频率参考时钟) 引脚上施加一个本地时钟。 在 PLL 锁定到 TCLK 的过程中,串行器的输出仍保持在高阻态。

SYNCHRONIZATION MODE

解串器的锁相环(PLL)必须与串行器同步,才能接收有效数据。同步可以通过以下两种方式之一实现:

- Rapid Synchronization 快速同步:

- 串行器具有发送特定 SYNC 模式的能力,该模式由六个“1”和六个“0”交替组成,以输入时钟频率切换。发送 SYNC 模式可以使解串器在可预测的时间内锁定到串行器的信号。SYNC 模式的发送通过串行器上的 SYNC1 和 SYNC2 输入引脚进行控制。当接收到有效的 SYNC1 或 SYNC2 脉冲(宽度超过 6 个时钟周期)时,串行器会发送 1026 个周期的 SYNC 模式。

- 当解串器在 LVDS 输入端检测到边沿跳变时,它会尝试锁定嵌入在数据中的时钟信息。在其 PLL 正在锁定串行输入中的数据或 SYNC 模式期间,解串器的 LOCK 输出保持为高电平。当解串器成功锁定到 LVDS 数据时,LOCK 输出变为低电平。当 LOCK 为低电平时,解串器的输出即表示接收到的 LVDS 数据。

- 注:一种常用的方法是将解串器的 LOCK 输出直接连接到串行器的 SYNC1 或 SYNC2 引脚(或者直接将两者都置为0)。

- Random-Lock Synchronization 随机锁定同步:

- 解串器可以在无需串行器发送特殊 SYNC 模式的情况下,对数据流实现锁定。这使得 SN65LV1224B 能够应用于开环系统中。同样重要的是,该解串器还具备在运行中的背板系统中支持热插拔的能力。

- 在开环或热插拔的情况下,假设数据流本质上是随机的。因此,由于锁定时间受到数据流特性的影响,无法精确预测锁定所需的时间。随机锁定时间的主要限制因素是解串器上电时接收到的数据与 REFCLK 之间的初始相位关系。

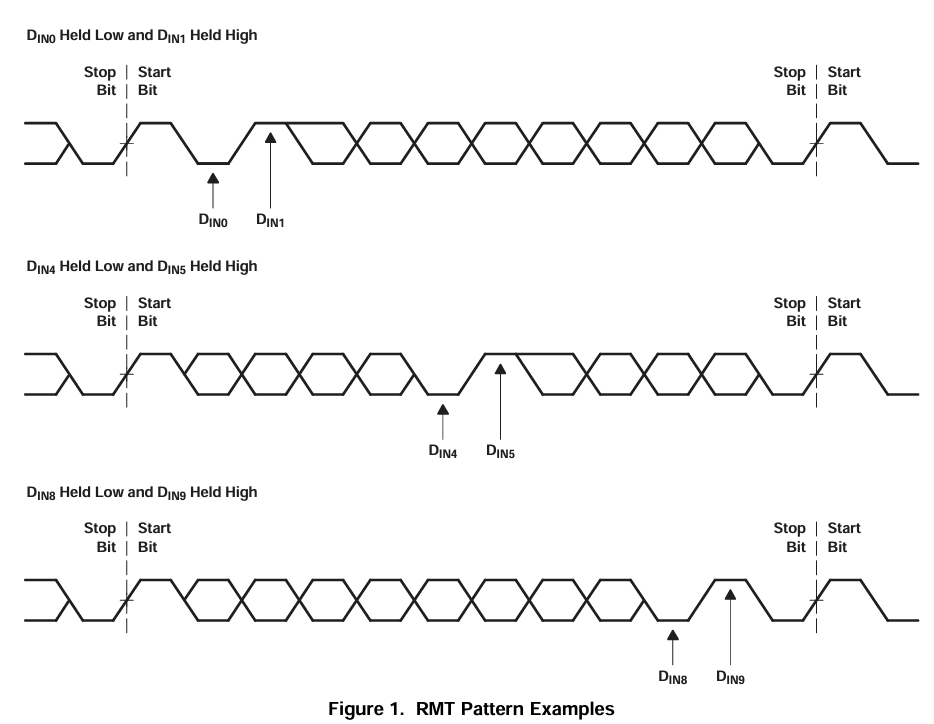

RMT

- 数据流中的内容也会影响锁定时间。如果某个特定的数据模式重复出现,解串器可能会进入错误锁定状态——即错误地将数据模式识别为起始/停止位。这种现象被称为重复多跃迁(RMT);参见图 1 获取 RMT 的示例。RMT 发生在多个连续的时钟周期内,每个周期中存在多个低到高的跳变。

- 在最坏的情况下,解串器可能会锁定在数据模式上,而不是正确的时钟信号。为防止这种情况,解串器内部设计了电路来检测是否存在错误锁定的可能性。一旦检测到该可能性,电路会阻止 LOCK 输出变为有效,直到潜在的错误锁定模式发生改变。需要注意的是,RMT 模式只会影响解串器的锁定时间。一旦解串器成功锁定,只要每个周期中数据边界(起始/停止位)保持一致,RMT 模式就不会影响解串器的工作状态。解串器只有在连续四个周期中在相同位置检测到唯一的数据边界(起始/停止位)后,才会进入锁定状态。

-

解串器会保持锁定状态,直到在连续四个周期内无法检测到相同的数据边界(起始/停止位)为止。此时,解串器会失去锁定状态,并开始重新寻找新的数据边界(起始/停止位)。在发生同步丢失的情况下,LOCK 引脚输出变为高电平,所有输出(包括 RCLK)将进入高阻态。用户系统应监控 LOCK 引脚,以便及时检测同步丢失。一旦检测到失锁,如果需要在特定时间内重新建立锁定,建议通过发送同步模式(SYNC patterns)进行重新同步。不过,如前所述,解串器也可以锁定到随机数据流。

| | | |

|SYNC1 DO+|-------±-------->|RI+ |

|SYNC2 DO−|-------±-------->|RI- LOCK|--------------PLL是否稳定----->

| | | |

| SERIALIZER | | DESERIALIZER |

| P2S | | S2P | [S2PControl]

|DIN | |DIN RCLK|---------DownSig_RClk--------->

|TCLK_R/F | |TCLK_R/F ROUT0–9|=DownSig_ROut=>

|TCLK | |REFCLK |

|| ||

同步帧为1026个时钟周期的同步码

DATA TRANSMISSION MODE

-

在完成初始化和同步之后,串行器开始从 DIN0–DIN9 接收并行数据。串行器使用 TCLK 输入对接收到的数据进行锁存。TCLK_R/F 引脚用于选择串行器采用哪个时钟边沿来采样输入数据。

如果任一 SYNC 输入在连续六个 TCLK 周期内保持为高电平,则无论选用了哪个时钟边沿,DIN0−DIN9 上的数据都会被忽略,串行器将发送 1026 个周期的 SYNC 模式。 -

在确定使用哪个时钟边沿之后,串行器会在寄存器中的数据位前后内部添加起始位和停止位,对数据进行帧定界。起始位始终为高电平,停止位始终为低电平。这两个位作为嵌入式时钟位存在于串行数据流中,用于实现时钟信息的传递。

-

串行器通过串行数据输出端(DO±)以 TCLK 频率的 12 倍速率发送串行化的数据和附加的时钟位(10 + 2 位)。例如,当 TCLK 为 66 MHz 时,串行数据速率为 66 × 12 = 792 Mbps。由于其中只有 10 位是输入的有效数据,因此实际有效数据速率为 TCLK 频率的 10 倍。例如,当 TCLK = 66 MHz 时,有效数据速率为 66 × 10 = 660 Mbps。提供 TCLK 的数据源必须在 10 MHz 到 66 MHz 的频率范围内。

-

串行器的输出端(DO±)可以用于点对点连接,或有限的多点或多路复用背板连接。当使能引脚(DEN)为高电平,PWRDN 为高电平,且 SYNC1 和 SYNC2 为低电平时,输出端会传输数据。

当 DEN 被拉低时,串行器的输出引脚会进入高阻态。 -

一旦解串器与串行器完成同步,LOCK 引脚将转为低电平。此时,解串器锁定到嵌入式时钟,并利用该时钟来恢复串行化的数据。

当 LOCK 为低电平时,ROUT 数据是有效的;否则,ROUT0–ROUT9 为无效数据。ROUT0−ROUT9 的数据由 RCLK 进行输出锁存。RCLK 的具体边沿极性由 RCLK_R/F 引脚选择。ROUT0–ROUT9、LOCK 和 RCLK 输出在 66 MHz 时钟频率下,最多可驱动三个 CMOS 输入门(这三个输出总共负载不超过 15 pF)。

POWERDOWN

- 当不需要进行数据传输时,可以使用掉电模式。串行器和解串器通过进入掉电状态(一种低功耗休眠模式)来降低功耗。

将解串器的 PWRDN 和 REN 引脚同时拉低,可使其进入掉电模式;而将串行器的 PWRDN 引脚拉低,则可使其进入掉电模式。在掉电状态下,锁相环(PLL)停止工作,输出进入高阻态,从而禁用负载电流,并将电源电流降至毫安级别。

若要退出掉电模式,需将 PWRDN 引脚拉高。 - 在串行器和解串器之间重新开始有效数据传输之前,必须对两者进行重新初始化并重新同步。

串行器的初始化过程需要 1026 个 TCLK 周期。

解串器在初始化期间会将 LOCK 引脚拉高,直到成功锁定到 LVDS 时钟信号为止。

HIGH-IMPEDANCE MODE

- 当 DEN 引脚被拉低时,串行器进入高阻模式。这会将两个驱动输出引脚(DO+ 和 DO−)置于高阻态。当 DEN 引脚被拉高时,串行器会恢复到之前的状态,只要其他控制引脚(如 SYNC1、SYNC2、PWRDN、TCLK_R/F)保持不变。

当 REN 引脚被拉低时,解串器进入高阻模式。因此,接收器输出引脚(ROUT0–ROUT9)和 RCLK 会进入高阻态。LOCK 输出仍保持激活状态,反映 PLL 的状态。

故障安全偏置 FAILSAFE BIASING FOR THE SN65LV1224B

- SN65LV1224B 的输入阈值灵敏度为 ±50 mV,这使得 SN65LV1224B 在差分噪声容忍度上具有更大的裕度。然而,在接收器输入未被主动驱动的情况下。SN65LV1224B 的较高灵敏度可能会将噪声误识别为信号,从而导致非预期的锁定。这种情况可能发生在输入电缆断开时。SN65LV1224B 内置有一个故障保护电路,该电路将串行输入和 LOCK 信号拉高。故障保护电路的响应时间取决于互连特性。

CG

- SN65LV1023A

- 基于光缆的深海摄像系统的设计与实现