SDC命令详解:使用set_propagated_clock命令进行约束

相关阅读

SDC命令详解![]() https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

目录

指定端口列表/集合

简单使用

注意事项

传播时钟是在进行了时钟树综合后,使用set_propagated_clock命令可以将一个理想时钟转换为传播时钟(注意,虚拟时钟即无时钟源对象的时钟无法被转换为传播时钟)(设置对象的propagated_clock属性为true),此时的时钟延迟由源延迟和真实网络延迟组成,这里的网络延迟是根据时钟路径上的线延迟和单元延迟真实计算出来的,而不再使用set_clock_latency命令设置网络延时。有关理想时钟和传播时钟的更详细内容,可以参考下面的博客。如果想要移除传播时钟,使用remove_propagated_clock命令。

静态时序分析:ideal_clock、propagated_clock以及generated_clock的关系及其延迟计算规则(一)![]() https://blog.csdn.net/weixin_45791458/article/details/139998035?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522e4f4bf160af3c2b2f079b3291ac96a32%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=e4f4bf160af3c2b2f079b3291ac96a32&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-139998035-null-null.nonecase&utm_term=%E4%BC%A0%E6%92%AD%E6%97%B6%E9%92%9F&spm=1018.2226.3001.4450 本文针对Design Compiler,但该命令同样存在于PrimeTime、IC Compiler等工具中,它们大致相同,略有差别。set_fanout_load命令的BNF范式(有关BNF范式,可以参考以往文章)为:

https://blog.csdn.net/weixin_45791458/article/details/139998035?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522e4f4bf160af3c2b2f079b3291ac96a32%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=e4f4bf160af3c2b2f079b3291ac96a32&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-139998035-null-null.nonecase&utm_term=%E4%BC%A0%E6%92%AD%E6%97%B6%E9%92%9F&spm=1018.2226.3001.4450 本文针对Design Compiler,但该命令同样存在于PrimeTime、IC Compiler等工具中,它们大致相同,略有差别。set_fanout_load命令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_propagated_clockobject_list指定端口列表/集合

指定一个列表/集合,包含时钟对象、端口对象或引脚对象,对于列表而言,如果有多于一个对象,需要使用引号或大括号包围(对使用集合无效),关于列表和集合的区别,可以参考下面的博客。

SDC命令详解:使用集合(Collection)而不是字符串(String)/列表(List)作为命令参数![]() https://chenzhang.blog.csdn.net/article/details/147144571

https://chenzhang.blog.csdn.net/article/details/147144571

简单使用

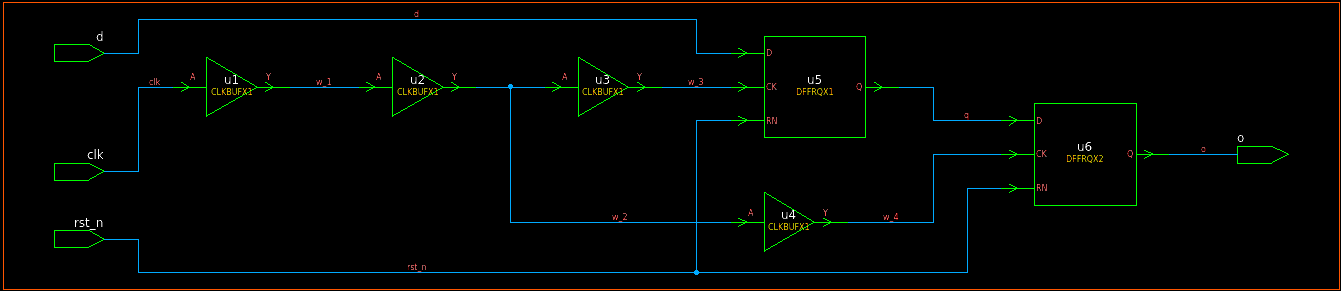

下面用一个简单的例子进行说明,图1是两个D触发器的简单级联,可以看出此时的时钟路径上人为插入了一些缓冲器。

图1 一个简单的例子

下面使用create_clock命令,在clk端口创建了一个理想时钟,周期为10。

dc_shell> create_clock -period 10 [get_ports clk]对于理想时钟而言,它的延迟包括两部分:源延迟(source)和网络延迟(network delay),它们都是使用set_clock_latency命令进行设置的,关于该命令的使用,可以参考之前的文章SDC命令详解:使用set_clock_latency命令进行约束。 注意:理想时钟的网络延迟值是直接设置的,而不会从时钟路径上的线延迟(net delay)和单元延迟(cell delay)中推断出来。

下面的命令设置了时钟clk的源延迟为2ns,网络延迟为0.5ns。

dc_shell> set_clock_latency -source 2 [get_clocks clk]

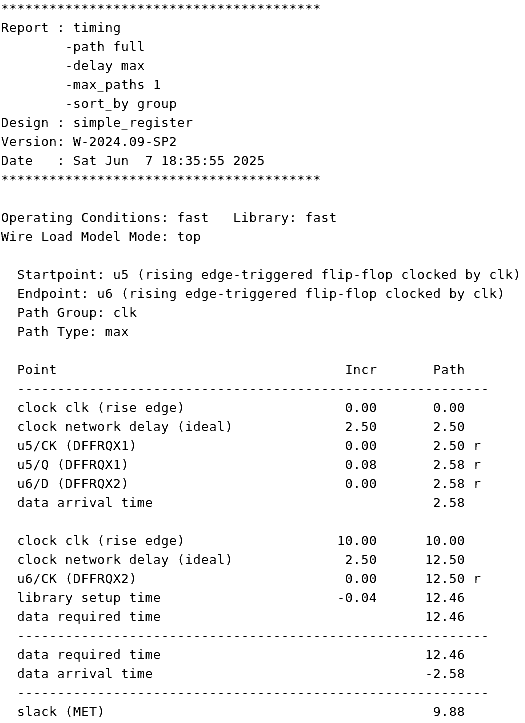

dc_shell> set_clock_latency 0.5 [get_clocks clk]图2所示的建立时间时序报告显示,时钟的总延迟为2.5ns(注意这里的network delay其实指的是总延迟,而不只是网络延迟),括号中的ideal提示了这是一个理想时钟。

图2 建立时间时序报告

下面使用set_propagated_clock命令将理想时钟clk转换成传播时钟,此时会给出警告。

dc_shell> set_propagated_clock [get_clocks clk]

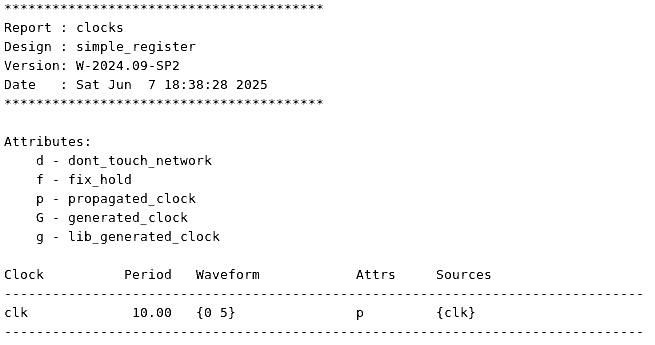

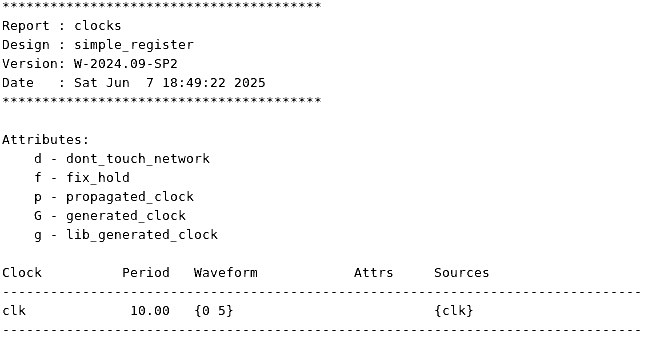

Warning: Converting ideal clock at 'clk' to propagated clock. (UID-477)图3是此时的时钟报告,可以看出此时的时钟clk已经拥有propagated_clock属性了,即是一个传播时钟了。

图3 时钟报告(传播时钟)

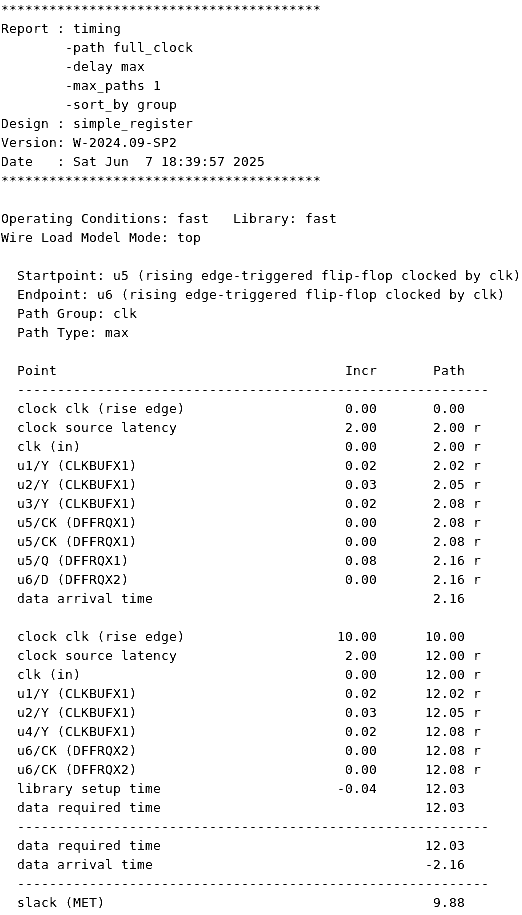

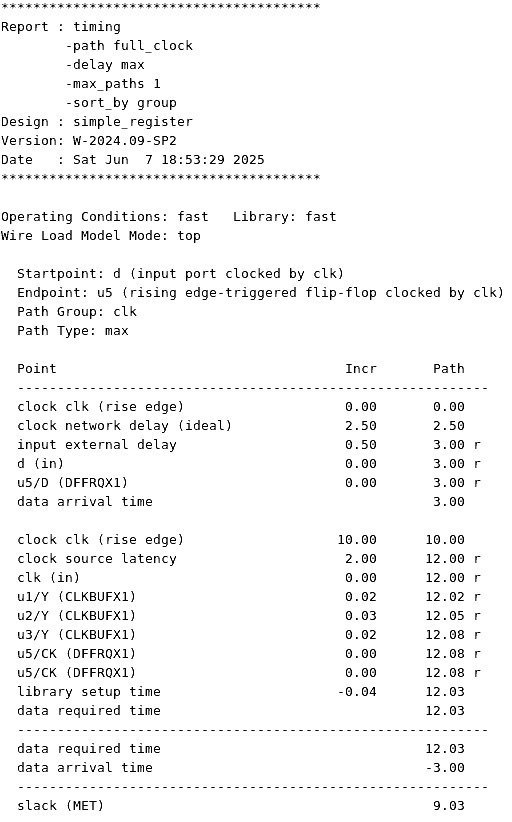

此时的时钟延迟由源延迟和真实网络延迟组成,这里的网络延迟是根据时钟路径上的线延迟和单元延迟真实计算出来的,如图4所示(此时添加了-path full_clock选项以显示出完整的时钟路径)。

图4 展开时钟路径的建立时间报告

注意事项

有些时候,会设置端口对象或引脚对象的传播时钟属性,此时经过这些端口对象或引脚对象的时钟对象将被视为传播时钟(注意,该时钟本身可以是理想时钟)。

下面依旧以图1为例说明这种情况,使用set_propagated_clock命令设置输入端口clk的传播时钟属性。

dc_shell> set_propagated_clock [get_clocks clk]此时时钟对象依旧是理想时钟,如图5所示。

图5 时钟报告(理想时钟)

下面使用set_input_delay命令设置输入端口d的输入延迟。

dc_shell> set_input_delay 0.5 -clock [get_clocks clk] [get_ports d]此时经过输入端口d的建立时间时序报告如图6所示(此时添加了-path full_clock选项以显示出完整的时钟路径)。

图6 展开时钟路径的建立时间报告

可以看出,即使是同一个时钟对象clk,对于发射路径其被视为理想时钟(使用设置网络延迟), 对于捕获路径其被视为传播时钟(使用真实网络延迟)。

如果将时钟本身设置为传播时钟,发射路径将只包含源延迟,而不含网络延迟(在不使用-reference_pin选项的情况下)。