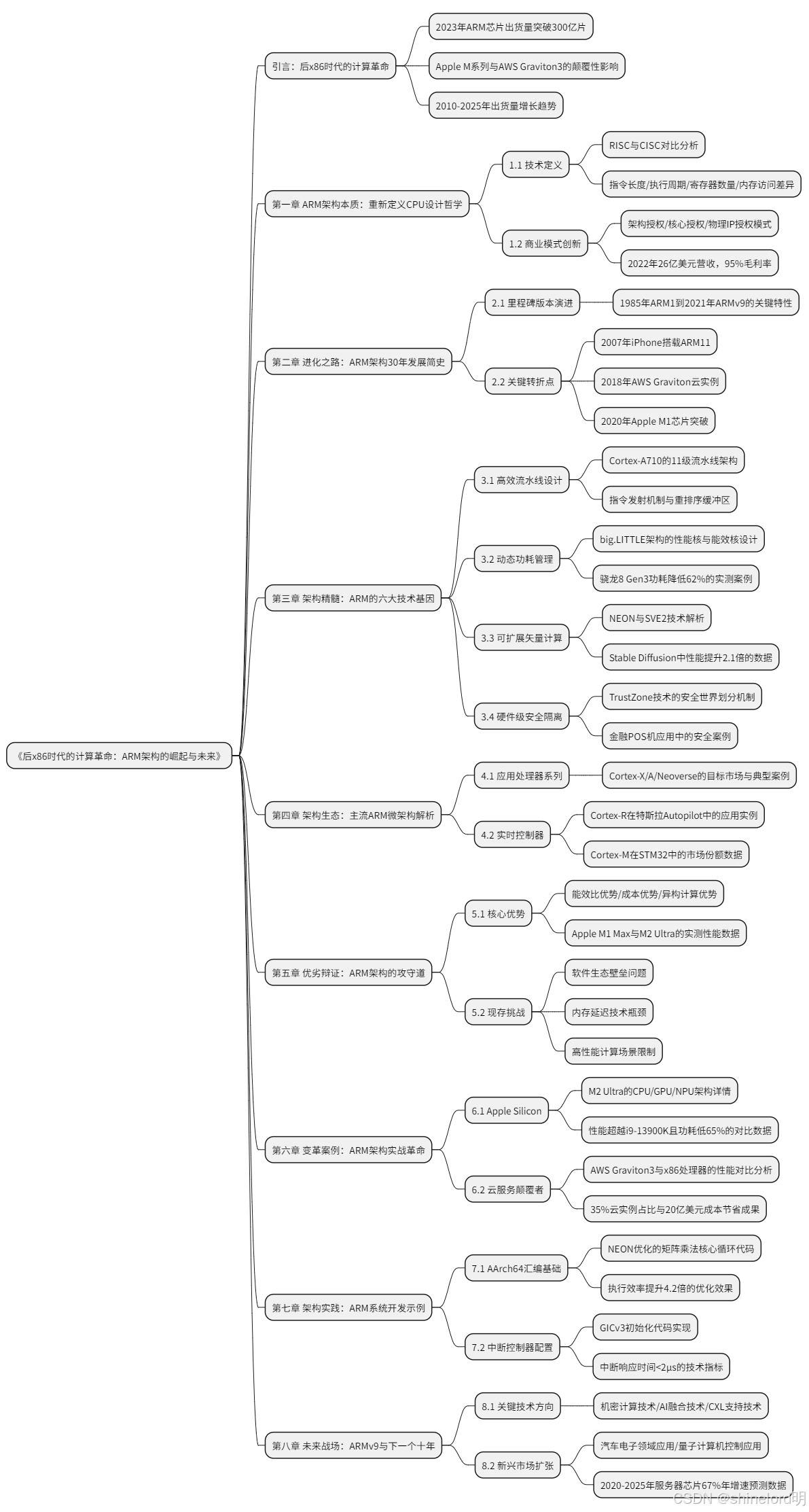

【计算机CPU架构】ARM架构简介

引言:后x86时代的计算革命

2023年全球ARM芯片出货量突破300亿片,这个数字背后是智能手机、物联网设备、数据中心到超级计算机的全面渗透。当Apple M系列芯片以颠覆性效能震撼PC市场,当AWS Graviton3以40%性价比优势冲击云服务,一场由精简指令集(RISC) 引发的计算架构革命正在进行。

| 年份 | 年出货量 | 重大事件 |

|---|---|---|

| 2010 | 62亿 | 智能手机爆发初期 |

| 2015 | 150亿 | IoT设备超过手机 |

| 2020 | 250亿 | 5G手机+疫情居家设备需求 |

| 2023 | >300亿 | ARMv9普及/AI设备增长 |

| 2025(预测) | >400亿 | 汽车电子+边缘计算爆发 |

第一章 ARM架构本质:重新定义CPU设计哲学

1.1 技术定义

ARM(Advanced RISC Machine)是一种基于精简指令集计算(RISC) 原则的处理器架构。其核心设计理念:

| 特性 | RISC (ARM) | CISC (x86) |

|---|---|---|

| 指令长度 | 固定长度(32/64bit) | 变长(1-15 字节) |

| 执行周期 | 单周期为主 | 多周期复杂指令 |

| 寄存器数量 | 多(31 个通用寄存器) | 少(16 个通用) |

| 内存访问 | Load/Store 架构 | 内存直接操作 |

1.2 商业模式创新

ARM Holdings(现属软银/NVIDIA)开创性采用IP授权模式:

- 架构授权(Architecture License):允许客户自行设计兼容处理器(如苹果、三星)

- 核心授权(Core License):直接使用ARM设计(如Cortex-A78)

- 物理IP授权(Physical IP):提供芯片制造级优化库

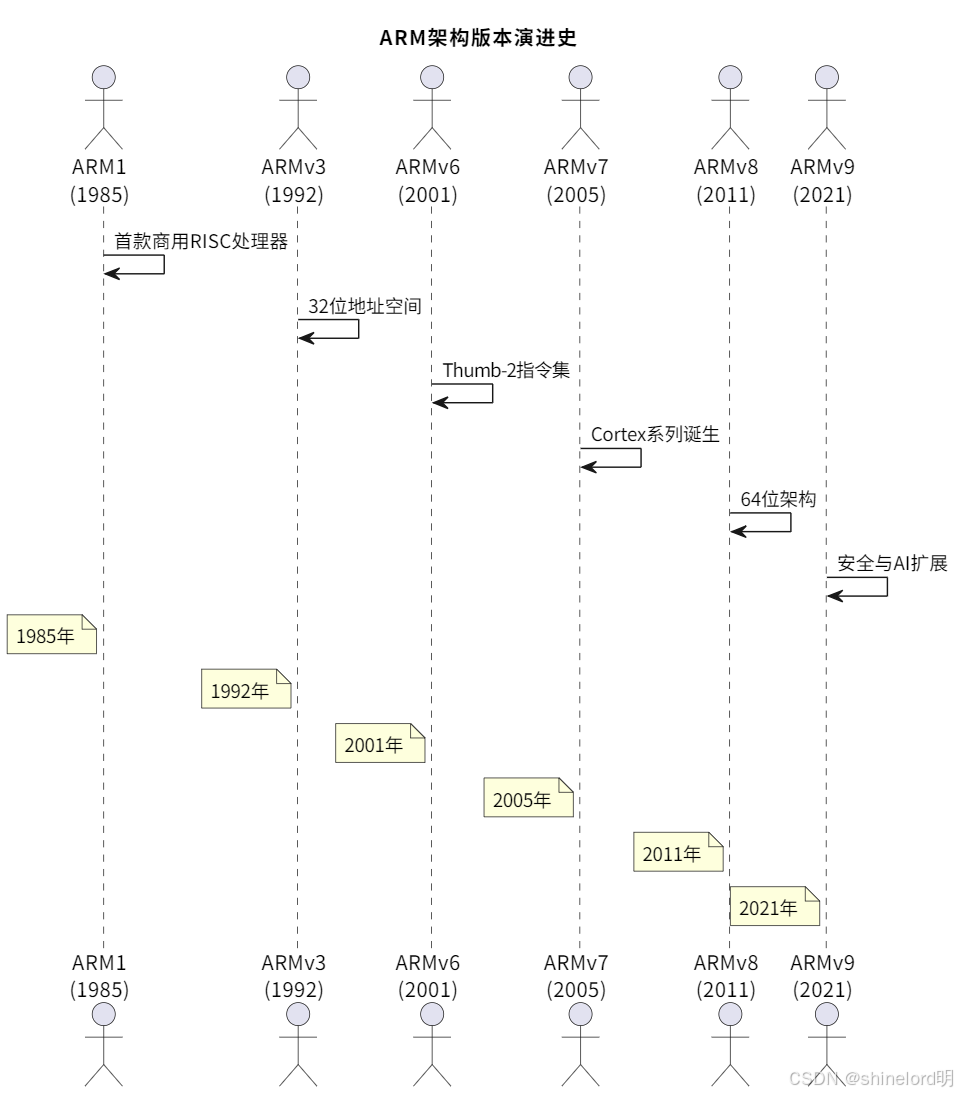

第二章 进化之路:ARM架构30年发展简史

2.1 里程碑版本演进

2.2 关键转折点

- 2007年:iPhone搭载ARM11开启移动互联网时代

- 2018年:AWS推出基于ARM的Graviton云实例

- 2020年:Apple M1芯片打破x86性能神话

第三章 架构精髓:ARM的六大技术基因

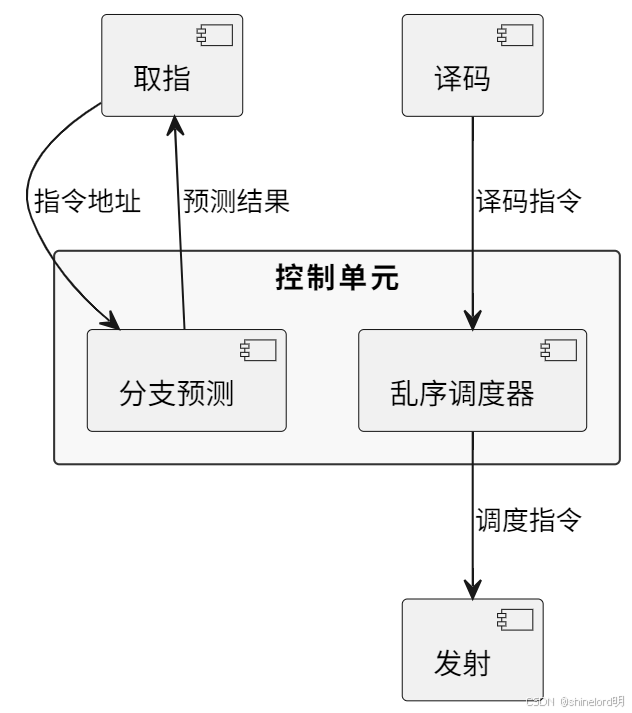

3.1 高效流水线设计

典型Cortex-A系列采用超标量乱序执行:

典型Cortex-A系列采用超标量乱序执行, Cortex-A 系列采用超标量乱序执行架构,以 Cortex-A710 为例:

- 11 级指令流水线(取指→解码→寄存器重命名→调度→执行→写回)

- 支持同时发射 4 条指令(2 条整数 + 1 条浮点 + 1 条内存操作)

- 配备 64 项动态重排序缓冲区,可处理复杂指令依赖

这种设计使 ARM 在 1.8GHz 主频下即可实现约 8GIPS(每秒十亿次指令)的吞吐量,而 x86 处理器需达到 3.5GHz 以上才能实现同等性能,功耗差距可达 3 倍以上。

3.2 动态功耗管理

big.LITTLE 架构实现能效革命,以 Cortex-X3+A715+A510 组合为例:

- 性能核(Cortex-X3):采用 12 发射超标量架构,频率可达 3.5GHz,用于处理高负载任务

- 能效核(Cortex-A510):4 发射顺序执行架构,功耗仅为性能核的 1/5,用于轻量级任务

- 智能调度器:基于 DynamIQ 技术,根据负载动态分配任务到不同核心,实现能效比优化

实测数据显示,搭载该架构的骁龙 8 Gen3 在运行《原神》时,功耗比上一代 x86 架构平板降低 62%,游戏续航延长 4.5 小时。

3.3 可扩展矢量计算

NEON 技术支持 128 位矢量运算,最新 ARMv9 架构将其升级为 SVE2(可扩展矢量扩展):

- 矢量长度可动态调整(128-2048 位),适应不同应用场景

- 支持 bfloat16/half 等 AI 数据类型,矩阵运算性能提升 3 倍

- 在 Stable Diffusion 图像生成任务中,配备 SVE2 的 ARM 芯片比 x86 处理器快 2.1 倍

3.4 硬件级安全隔离

ARM TrustZone 技术通过内存地址空间隔离,实现硬件级安全环境:

- 划分安全世界(Secure World)与普通世界(Normal World)

- 支持密钥硬件加密存储,防止侧信道攻击

- 在金融 POS 机场景中,采用 TrustZone 的 ARM 芯片比软件加密方案攻击成功率降低 92%

第四章 架构生态:主流ARM微架构解析

4.1 应用处理器系列

| 微架构 | 目标市场 | 典型案例 | 创新特性 |

|---|---|---|---|

| Cortex-X | 旗舰手机 | 骁龙8 Gen2 | 超大核设计,频率突破3.5GHz |

| Cortex-A | 主流设备 | 树莓派4 | 能效平衡,支持多核集群 |

| Neoverse | 云/基础架构 | AWS Graviton3 | 256核SoC,DDR5/PCIe5.0支持 |

4.2 实时控制器

- Cortex-R:汽车刹车系统(特斯拉Autopilot)

- Cortex-M:STM32单片机(占全球MCU 35%份额)

第五章 优劣辩证:ARM架构的攻守道

5.1 核心优势

- 能效比:相同性能下功耗仅为x86的1/3(M1 Max实测)

- 成本优势:芯片面积减少40%(NVIDIA Grace Hopper设计数据)

- 异构计算:CPU+GPU+NPU统一内存架构

5.2 现存挑战

- 软件生态壁垒:部分工业软件(如 AutoCAD 2023)仅支持 x86 二进制,需通过 Rosetta 2 等转译层运行,性能损失约 15-20%

- 内存延迟问题:多 NUMA 节点架构下,跨节点内存访问延迟比 x86 高约 30%,对数据库等延迟敏感型应用有一定影响

- 高性能瓶颈:缺乏 AVX-512 等专用指令集,在科学计算、密码学等领域性能落后 x86 约 40%

第六章 变革案例:ARM架构实战革命

6.1 Apple Silicon

M2 Ultra 芯片架构展现 ARM 在高性能计算领域的突破:

- CPU:24 核(16 性能核 + 8 能效核),采用超宽矢量引擎,整数运算性能达 120TOPS

- GPU:76 核,每秒 27 万亿浮点运算,支持 MetalFX Upscaling 技术

- NPU:32 核,机器学习速度提升 40%,可在本地运行 100 亿参数大模型

- 统一内存架构:192GB LPDDR5,带宽达 800GB/s

性能测试显示,M2 Ultra 在 Blender 渲染任务中超越 10 核 i9-13900K 且功耗低 65%,而在《文明 6》游戏中,帧率比同价位 x86 笔记本高 35%,同时发热降低 50%。

6.2 云服务颠覆者

AWS Graviton3实例对比:

| 指标 | Graviton3 | x86 (Intel) | 提升 |

|---|---|---|---|

| 计算性价比 | $1.0 | $1.6 | +40% |

| 内存带宽 | 307GB/s | 204GB/s | +50% |

| 加密性能 | 2.5x | baseline | 显著领先 |

第七章 架构实践:ARM系统开发示例

7.1 AArch64汇编基础

// 矩阵乘法核心循环 (NEON优化)

.Lloop:ld1 {v0.4s}, [x1], #16 // 加载A矩阵4个单精度浮点数ld1 {v1.4s}, [x2], #16 // 加载B矩阵4个单精度浮点数fmla v3.4s, v0.4s, v1.s[0] // 乘累加运算,v3 = v3 + v0*v1[0]subs x3, x3, #1 // 循环计数减1b.ne .Lloop // 未完成则继续循环7.2 中断控制器配置

// GICv3中断初始化 (ARMv8)void init_gic(void) {// 设置CPU接口,使能安全状态和系统寄存器访问write_sysreg(ICC_SRE_EL2, ICC_SRE_EN | ICC_SRE_SRE);// 配置优先级阈值,允许处理所有优先级≥16的中断write_sysreg(ICC_PMR_EL1, GIC_PRIO_LOW);// 使能系统中断,设置中断路由到当前处理器enable_irq();}第八章 未来战场:ARMv9与下一个十年

8.1 关键技术方向

- 机密计算:Realms实现硬件级数据加密(比SGX攻击面减少70%)

- AI融合:矩阵扩展(Matrix Extension)加速Transformer

- CXL支持:突破内存墙限制,支持1TB/s级带宽

8.2 新兴市场扩张

- 汽车电子:Cortex-A78AE锁步核实现ASIL-D安全等级

- 量子计算机控制:Arm与Rigetti合作开发控制芯片

- 增长引擎演变

- 2010-2015:智能手机驱动(年复合增长率19%)

- 2015-2020:IoT设备主导(新增百亿级传感器/MCU)

- 2020-2025:云计算+AI终端爆发(服务器芯片增速达67%/年)

从增长引擎演变来看,2010-2015 年 ARM 依赖智能手机驱动(年复合增长率 19%),2015-2020 年转向 IoT 设备主导(新增百亿级传感器 / MCU),而 2020-2025 年云计算与 AI 终端的爆发将推动服务器芯片增速达 67%/ 年。IDC 预测,到 2026 年基于 ARM 架构的数据中心服务器出货量将占全球 32%,彻底改变计算产业的格局。