SAR ADC 比较器噪声分析(二)

SAR ADC的比较器是非常重要的模块,需要仔细设计。主要考虑比较器的以下指标:

1)失调电压

2)输入共模范围

3)比较器精度

4)传输延时

5)噪声

6)功耗

这里主要讲一下动态比较器的noise。

动态比较器一般用于高速SAR ADC中,且精度不会超过12bit。在《SAR ADC比较器噪声分析(一)》描述的回踢噪声在动态比较器显的更严重,因为latch把输出分的很开,达到电源和地的地步,所以ΔV变化非常大,回踢噪声就很大。

动态比较器noise的仿真

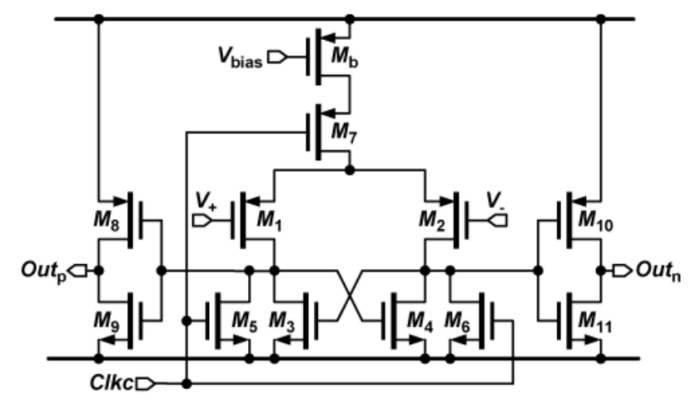

上面是比较常见的动态比较器,比较器clk从高到低时,比较器开始regeneration,在输出端电压差不超过50mV时,可以认为这个阶段还未产生很强的非线性,还处于可以小信号分析的阶段。所以做仿真时,需要把input的dc 偏差设置的较小,使M1和M2工作时产生的非线性较小。同时dc偏差设置的过小,因为有offset,这样输出的电压差包含offset和信号放大的值,会使偏差较大,需设置一个合适值。

在设置好一个合适的DC电压差值后,可以用tran noise和pss+pnoise的两种方法去做noise仿真分析。具体操作可以查看网上https://zhuanlan.zhihu.com/p/279111199《Comparator动态噪声的仿真》这篇文章,里面做了step to step的仿真指导。

Tran noise 仿真需要有一定的编程能力,写个veriloga代码,有点象一个试错的过程。等计算到84%的点,就算是输入noise的值。Tran noise 仿真比较慢,效率不高,但容易上手。

Pss+pnoise方法效率挺高的,但就是仿真设置要求比较高。各有优缺点,但做设计的最好两者都尝试下,看看用两种方法是否可以比对的上。

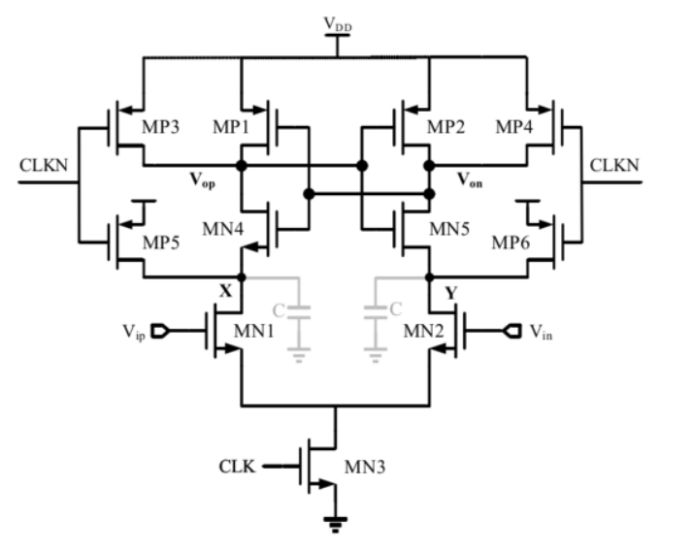

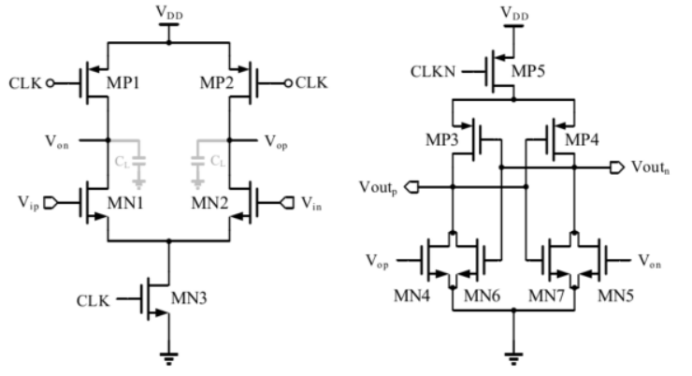

常见的动态比较器有strong-arm 结构和double -tail 结构,

Strong-arm 结构简单,无静态功耗,速度快,广泛应用于各种类型的adc中,缺点是电源和地之间堆叠了很多mos管,不适合低压设计。为了解决单级结构的strong-arm比较器存在回踢噪声和不适合低压设计的缺点,两级结构的double tail 比较器被提出。

上图是strong-arm 结构的动态比较器。

上图是double tail结构的比较器

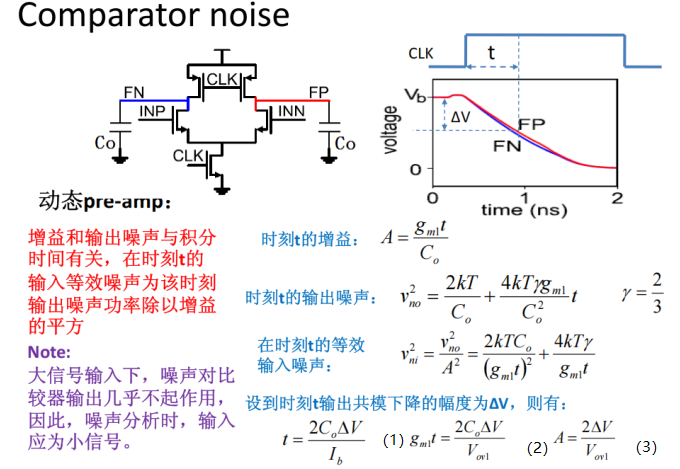

分析一下简单动态比较器的噪声:

在比较阶段,FP-FN因为输入电压差而产生输出电压差,式子(1)乘以gm1得到式子(2),式子(2)除以C0,得到式子(3)。式子(3)正是增益。

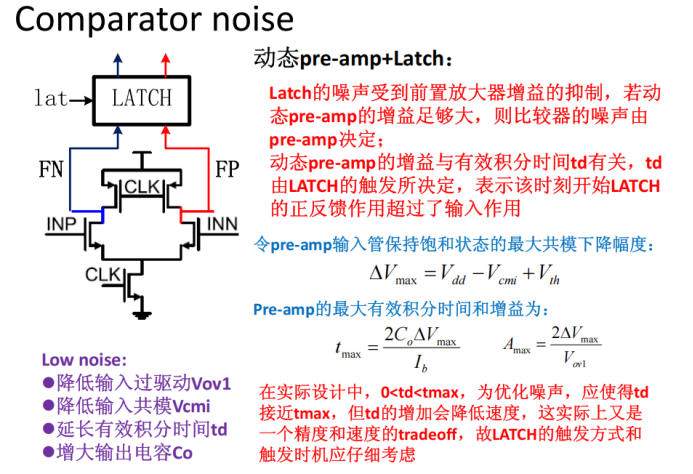

当FP-FN因为输入电压差而产生输出电压差,当电压差足够大时,latch的正反馈起作用,把输出拉到电源和地。这个电压差足够大的时刻点就是td。当latch起作用时,preamp的噪声就不重要了。所以在0~td这个阶段,如果需要降低噪声,根据贴图,可以通过降低输入过驱动Vov1,降低输入共模Vcmi,延长有效积分时间td,增加输出电容C0的手段实现。具体原因根据前后两张贴图,不难看出。

动态比较器还有个问题是会出现亚稳态

当FP-FN因为输入电压差足够小而产生输出电压差小,这样会导致latch无法触发,使比较结果出错,从而使整个SAR ADC 性能下降。通常需要一个亚稳态的监测电路。加入前置放大或加强latch能力也是减小亚稳态发生概率的方法