实验四 ——序列检测器和序列发生器

010 重叠的序列检测器(Mealy型和Moore型)

Mealy 型:

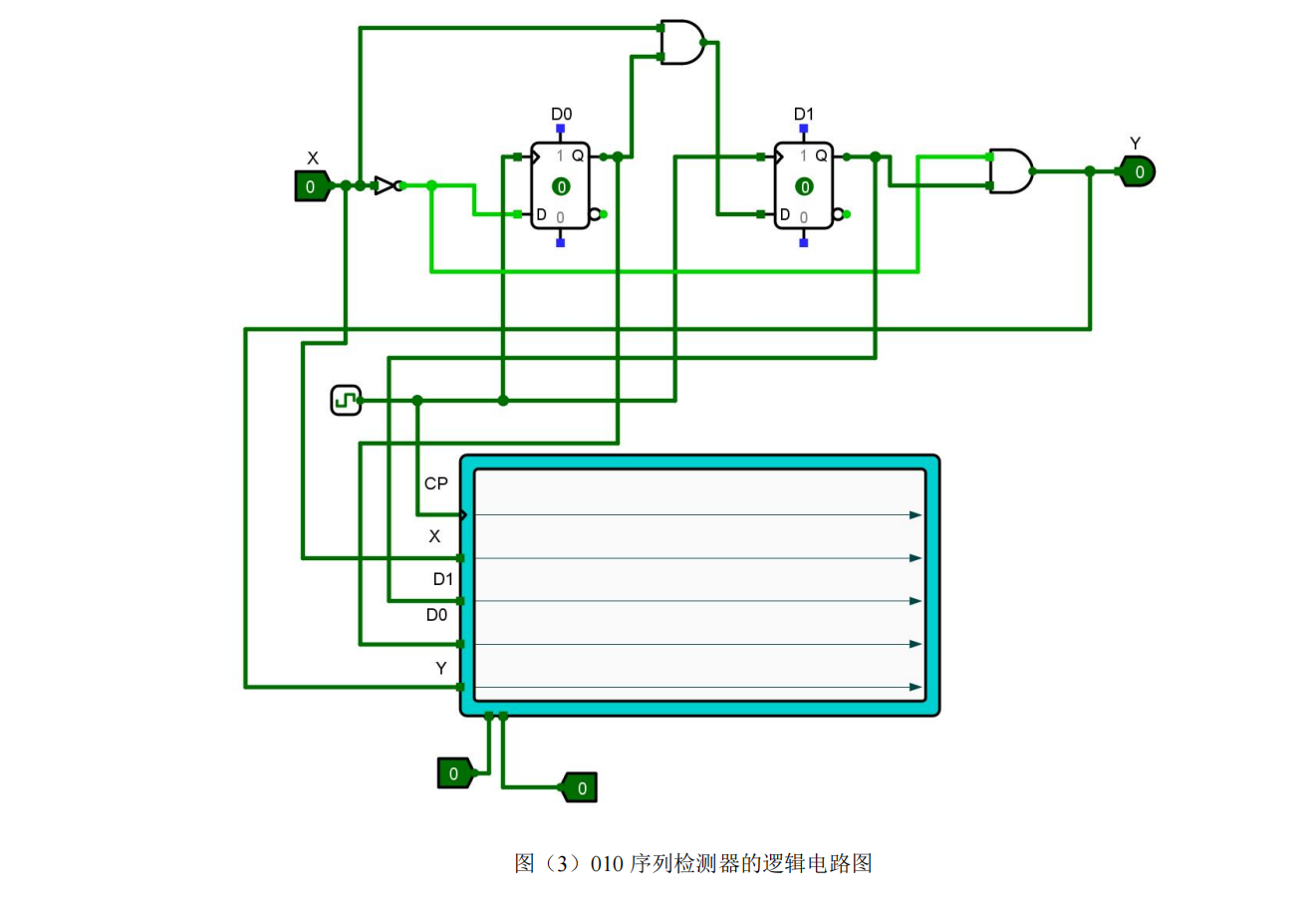

一、状态转换图

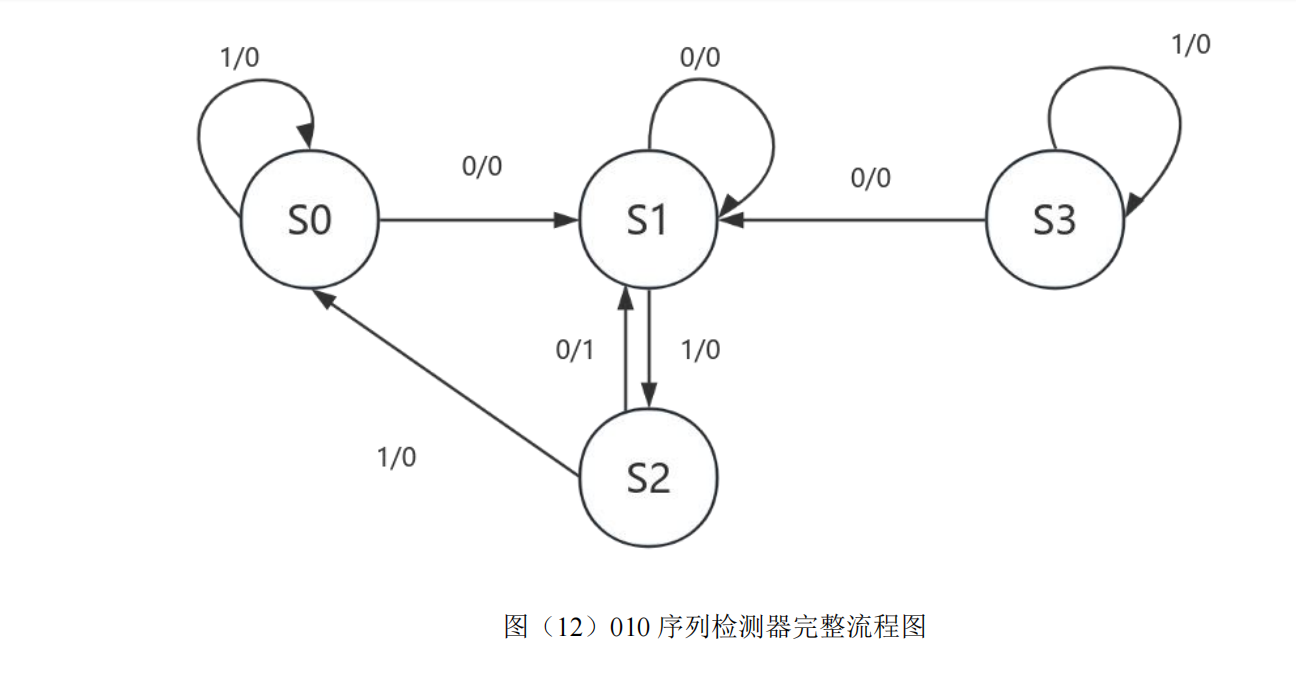

010 重叠的序列检测器是指当输入端连续输入 010 时输出端输出为 1,因此可以用三个 状态分别表示第一个输入为 0,第二个输入为 1,第三个状态输入为 0,只有当输入与要求 对应时才会跳转到下一状态,因此状态转换图如下图所示:

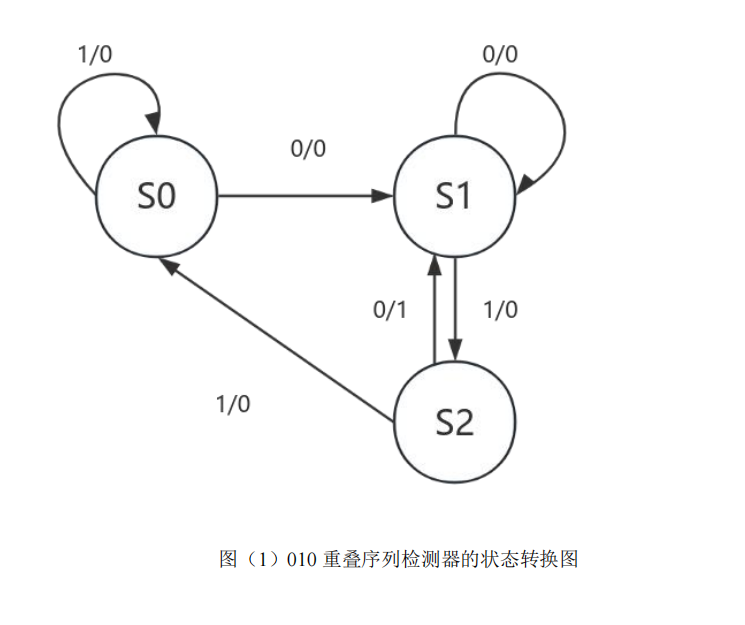

二、状态转换真值表

三、确定触发器的类型

由上述真值表可知要设计一个 010 重叠的序列检测器只需使用到三个状态,因此用到的 触发器的个数为 2 个,为了方便计算所选用的触发器为 D 触发器。

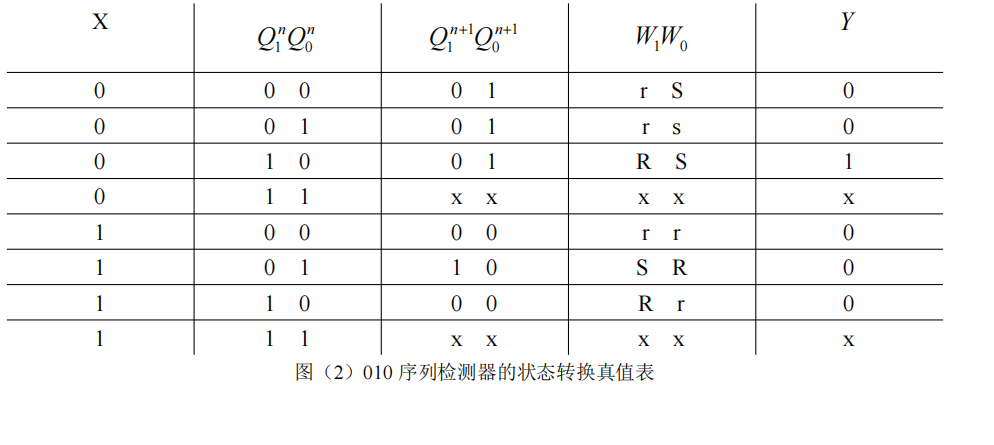

四、求激励函数和输出函数

1、通过卡诺图求得 D1,D0 的结果:

因此求得的激励函数分别为:,

。

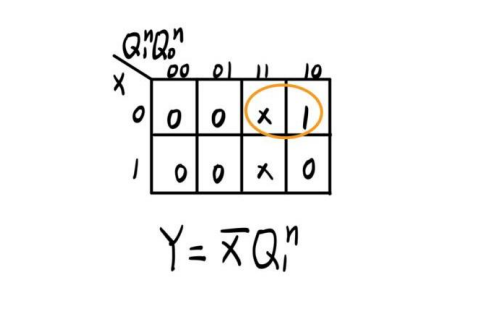

2、通过卡诺图求得输出 Y 的结果:

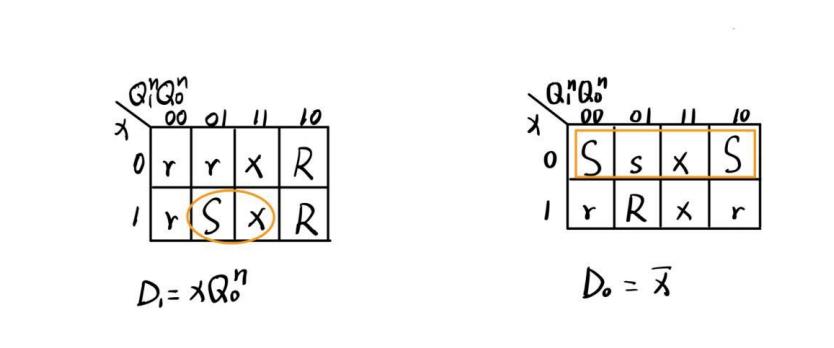

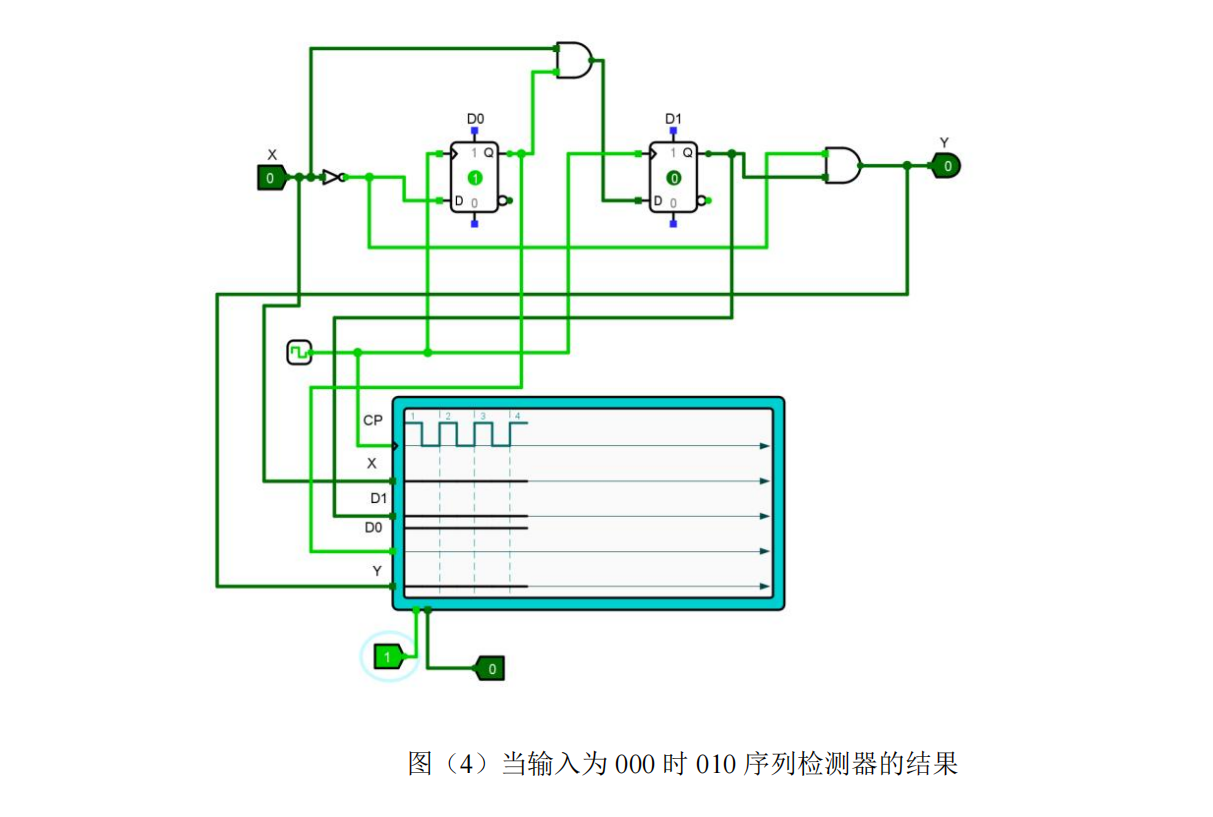

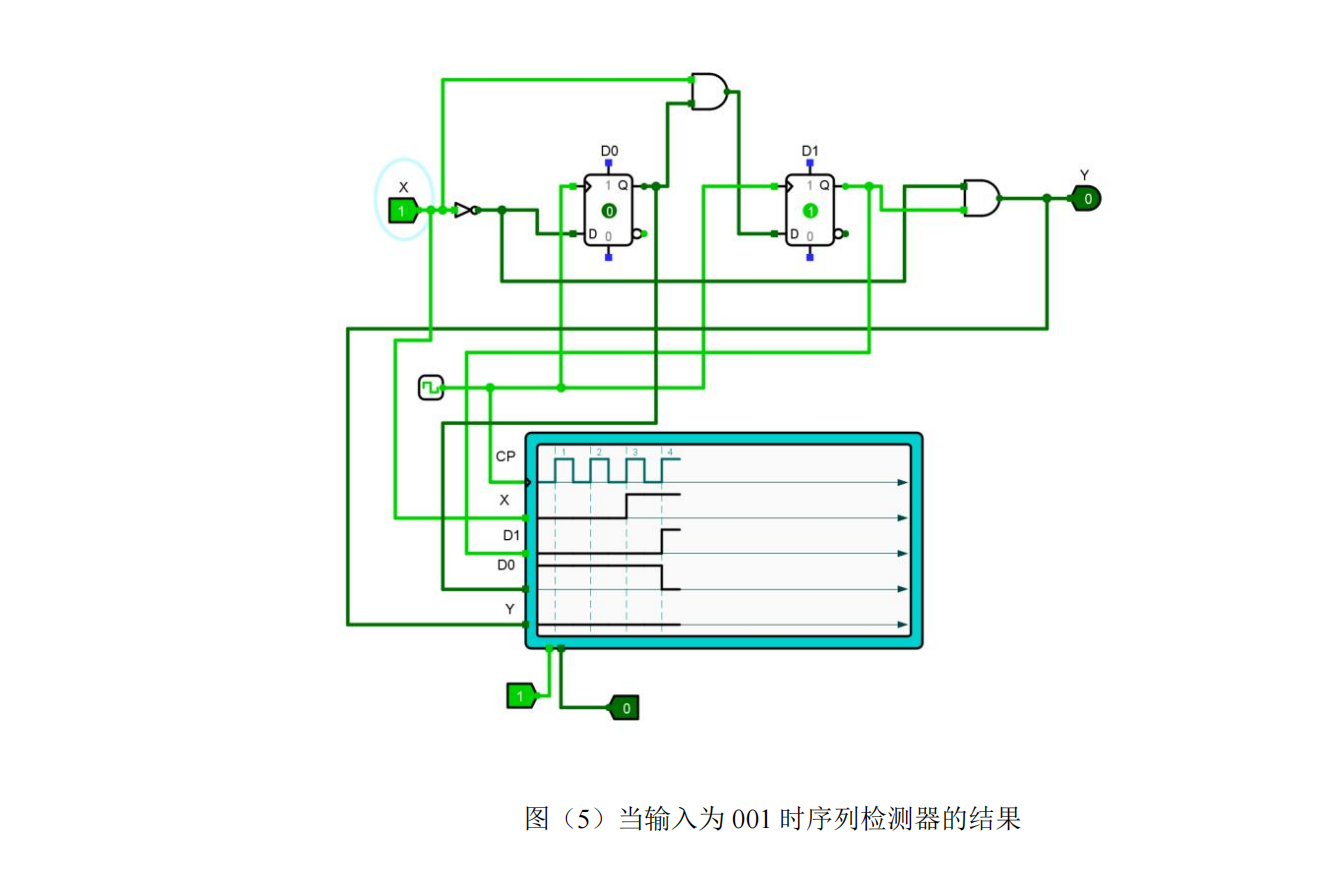

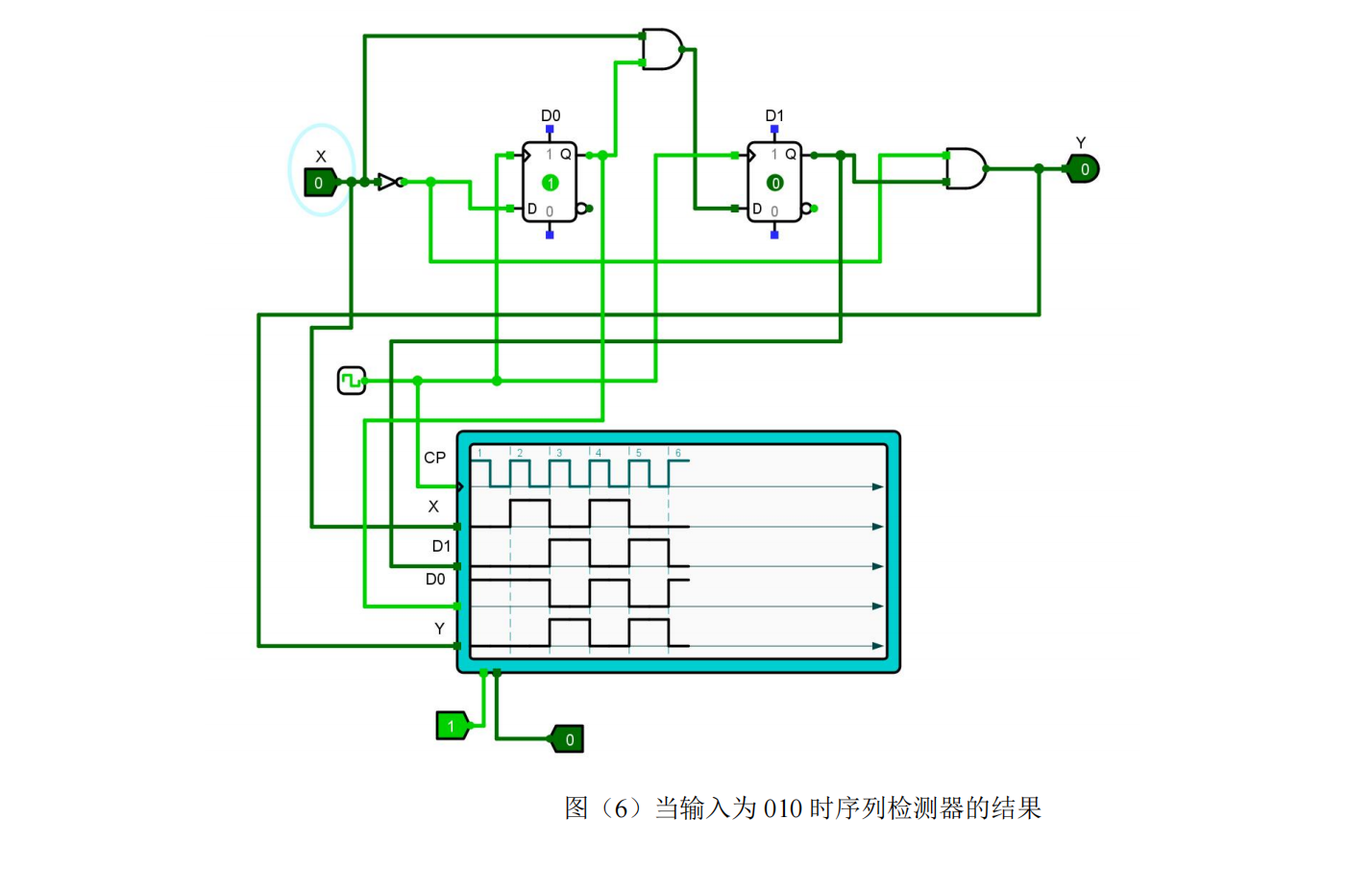

五、逻辑电路图

六、结果分析

1、当输入为 000 时,Y 输出为 0。

2、当输入为 001 时,输出 Y 为 0。

3、当输入为 010 时,输出 Y 为 1。

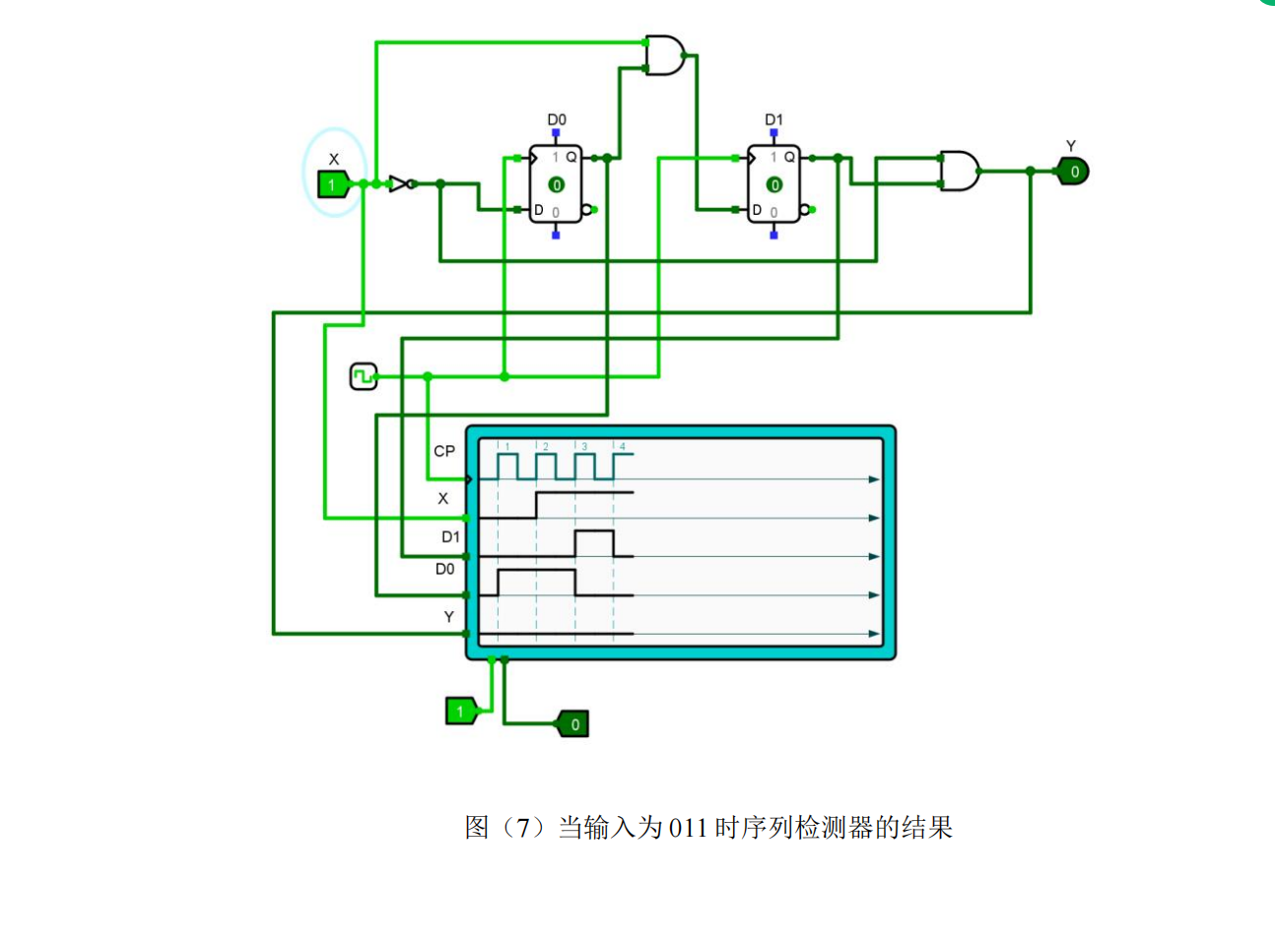

4、当输入为 011 时,输出 Y 为 0。

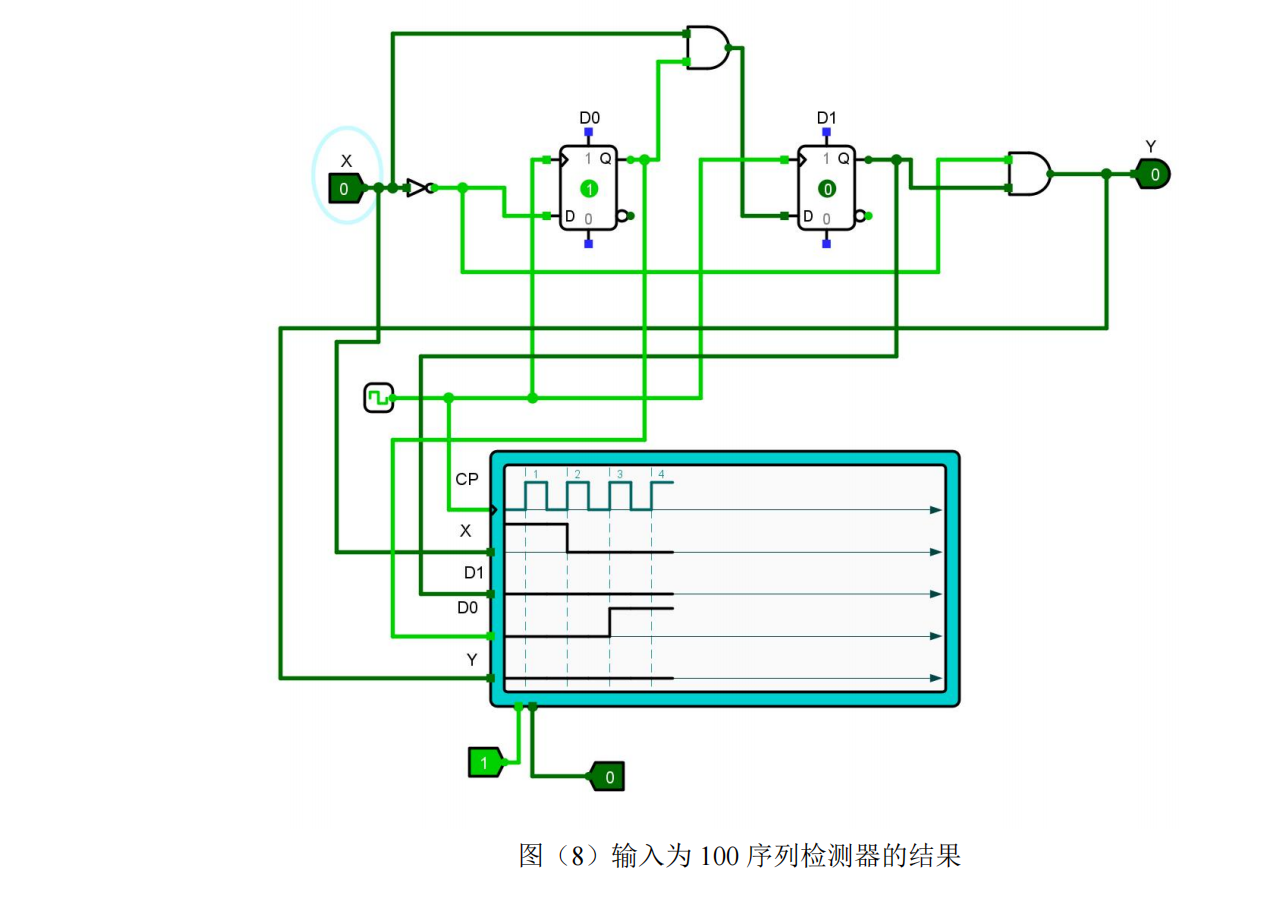

5、当输入为 100 时,输出为 0。

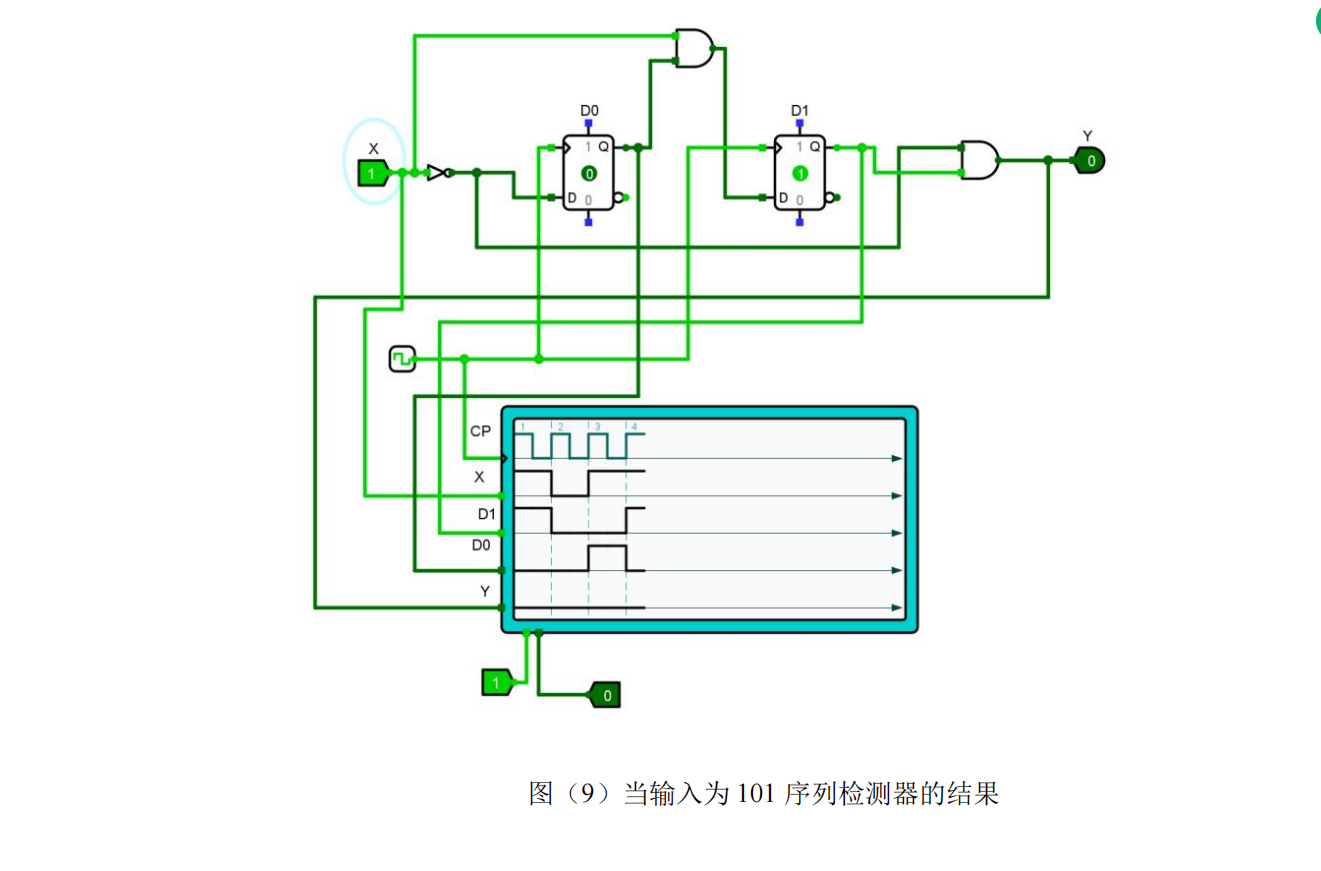

6、当输入为 101 时,输出 Y 为 0。

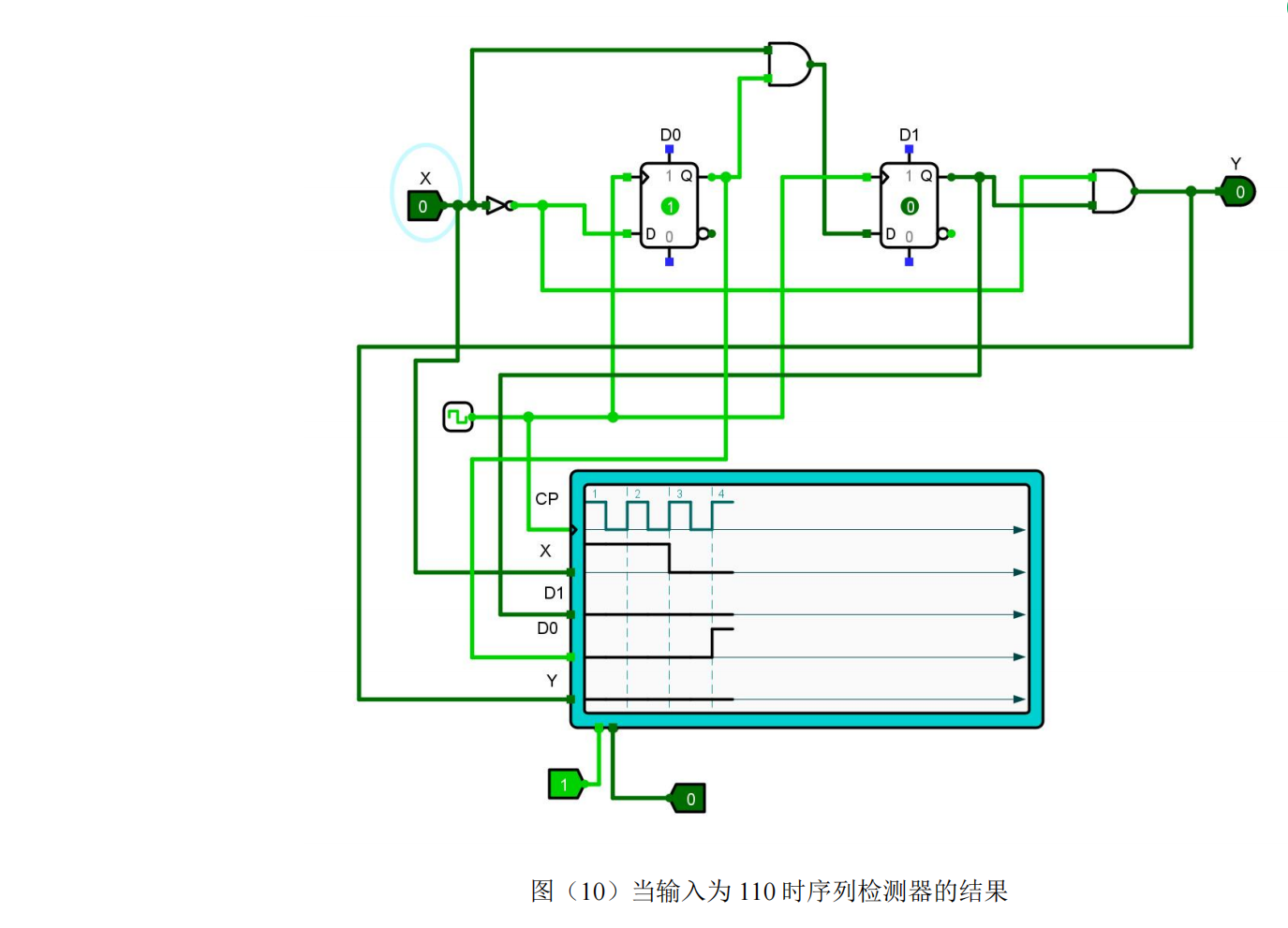

7、当输入为 110 时,输出 Y 为 0。

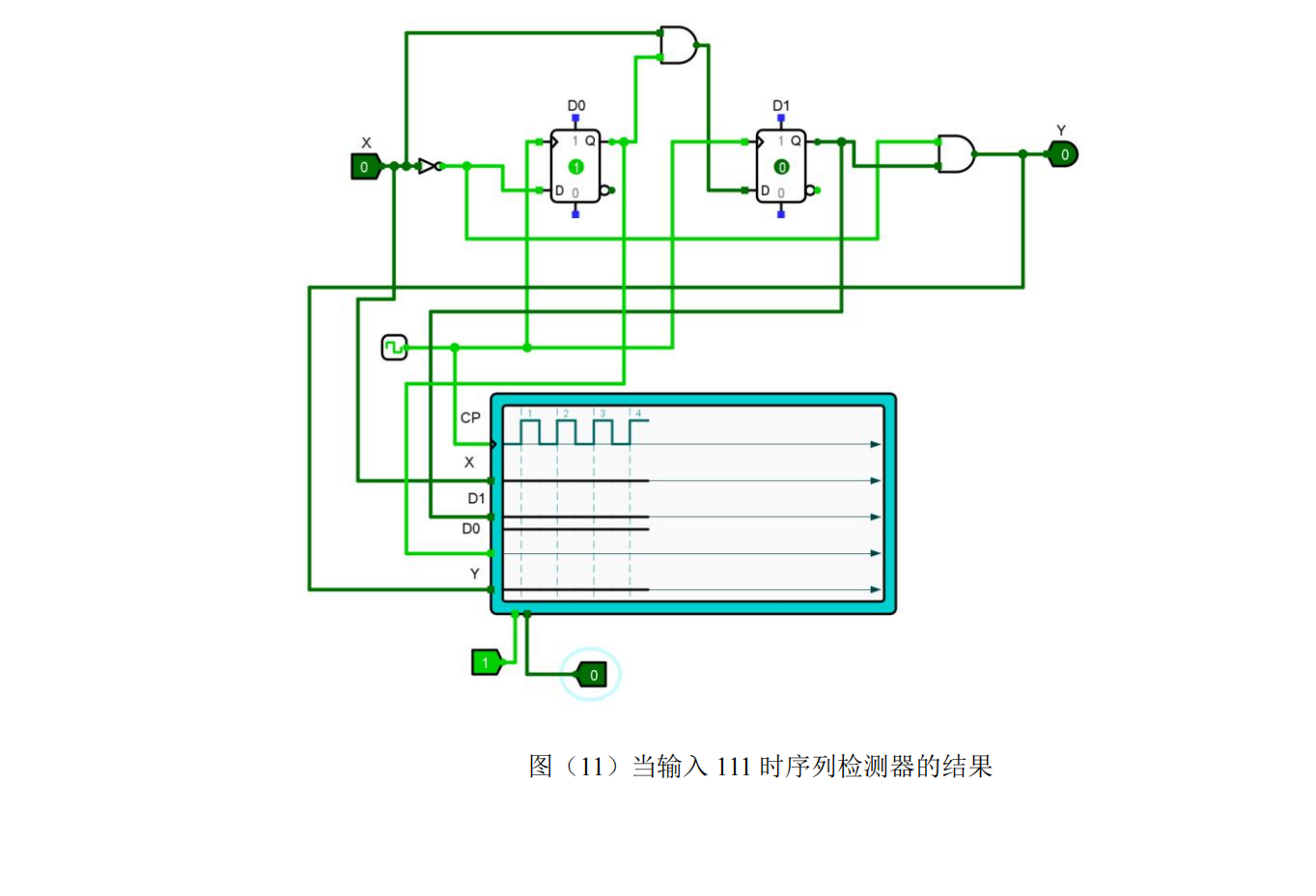

8、当输入为 111 时,输出 Y 为 0。

由上图示波器中结果显示当输入端 X 连续输入 010 时输出端 Y 输出为 1,然后紧 接着再输入连续的 10 时输出端 Y 输出为一,由此可知该电路实现了检测 010 可重叠序 列的功能。

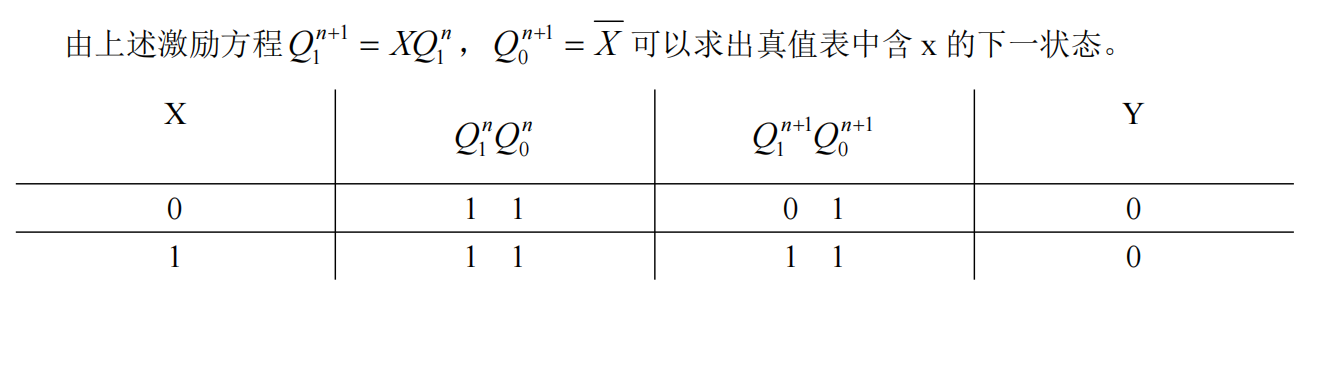

七、判断自启动

由此可画出完整的流程图为:

Moore 型不重叠 010 序列检测器

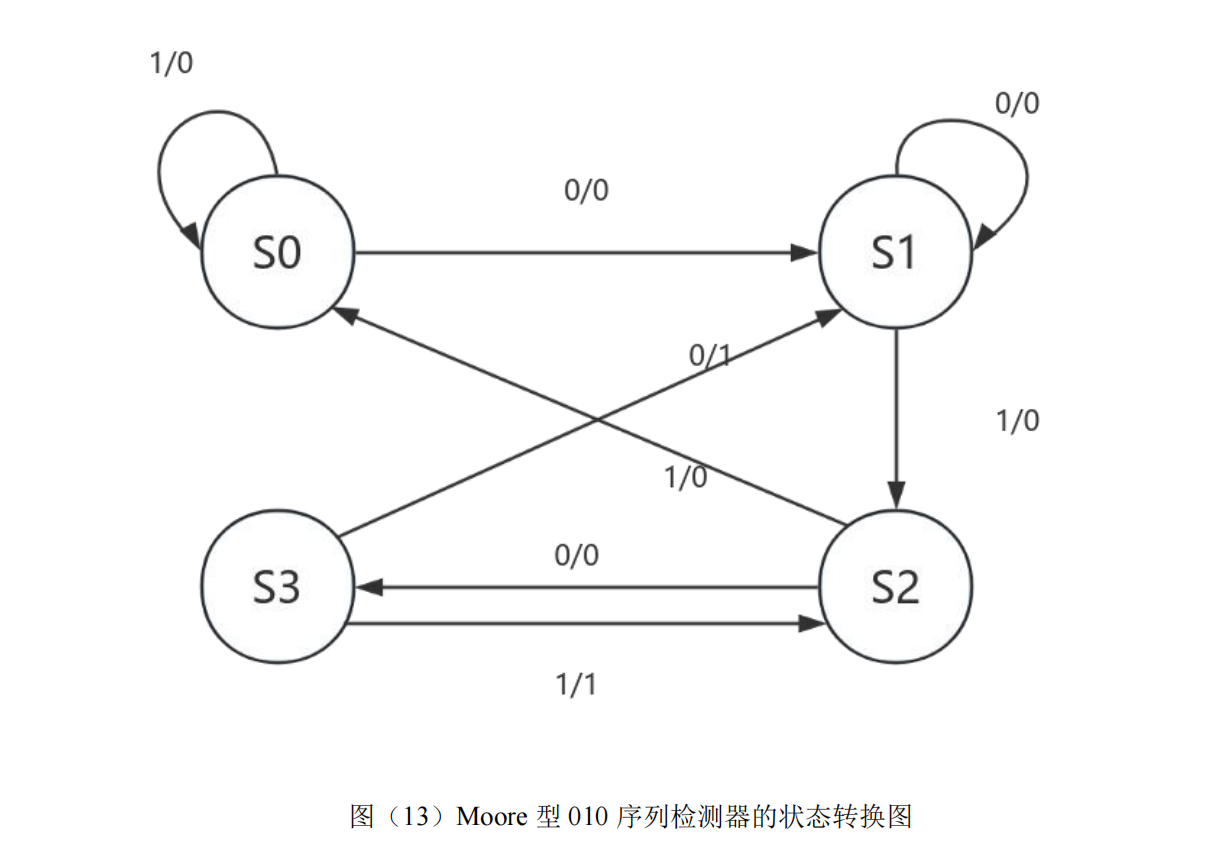

一、状态转换图

由于 Moore 型电路的输出 Y 不含输入 X,用 S0,S1,S2,S3 分别表示初始状态,检

测到 0 的状态,检测到 01 的状态以及检测到 010 的状态,因此只有当状态为 S3 时表示检

测到完整的序列 010,此时输出 Y 等于 1。

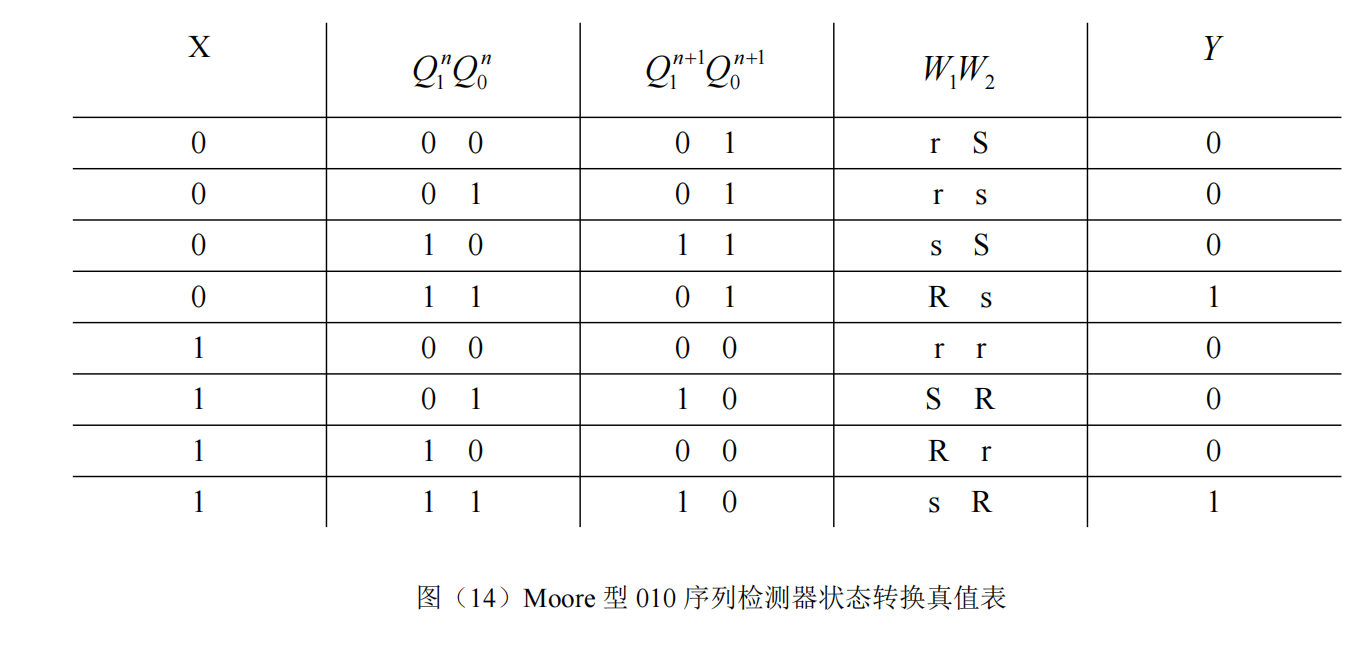

二、状态转换真值表

三、确定触发器的数量和类型

由于 Moore 型的 010 序列检测器一共需要四个状态,因此选用两个触发器,为了方便 计算本次实验选用 D 触发器。

四、求激励函数和输出函数

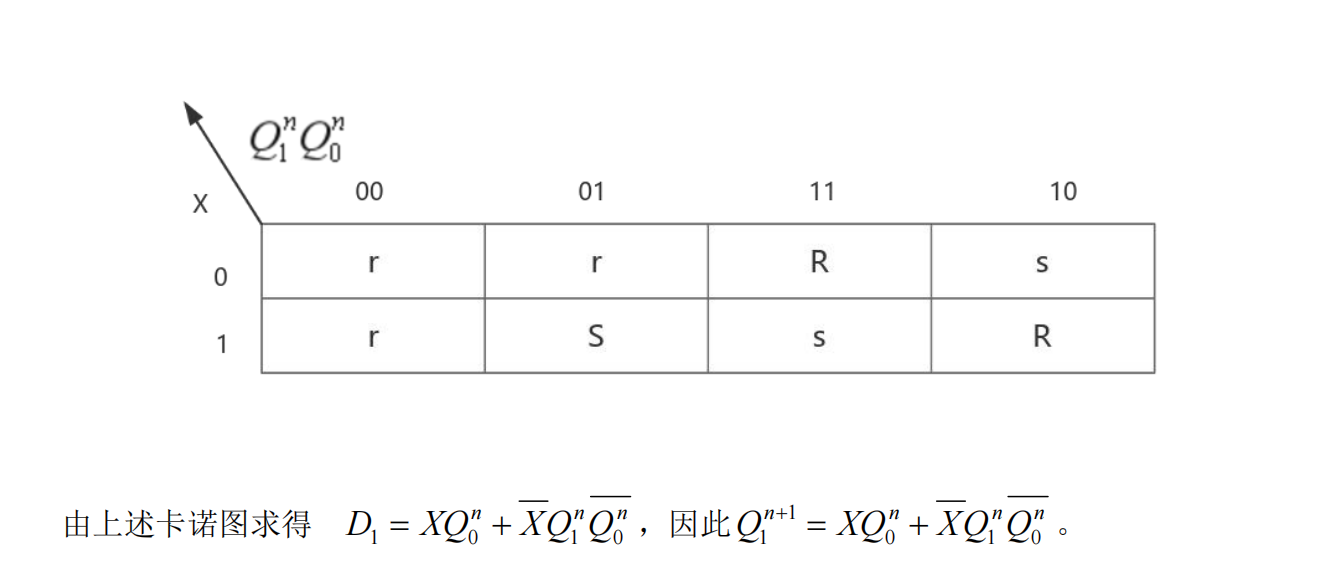

1、求  的激励方程:

的激励方程:

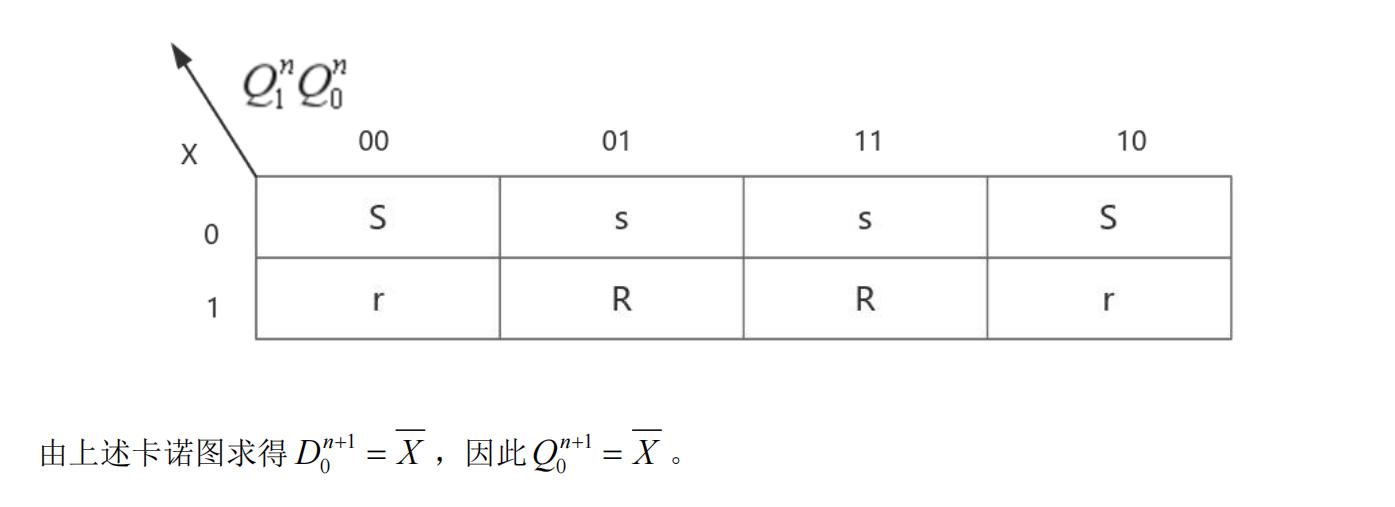

2、求  的激励方程:

的激励方程:

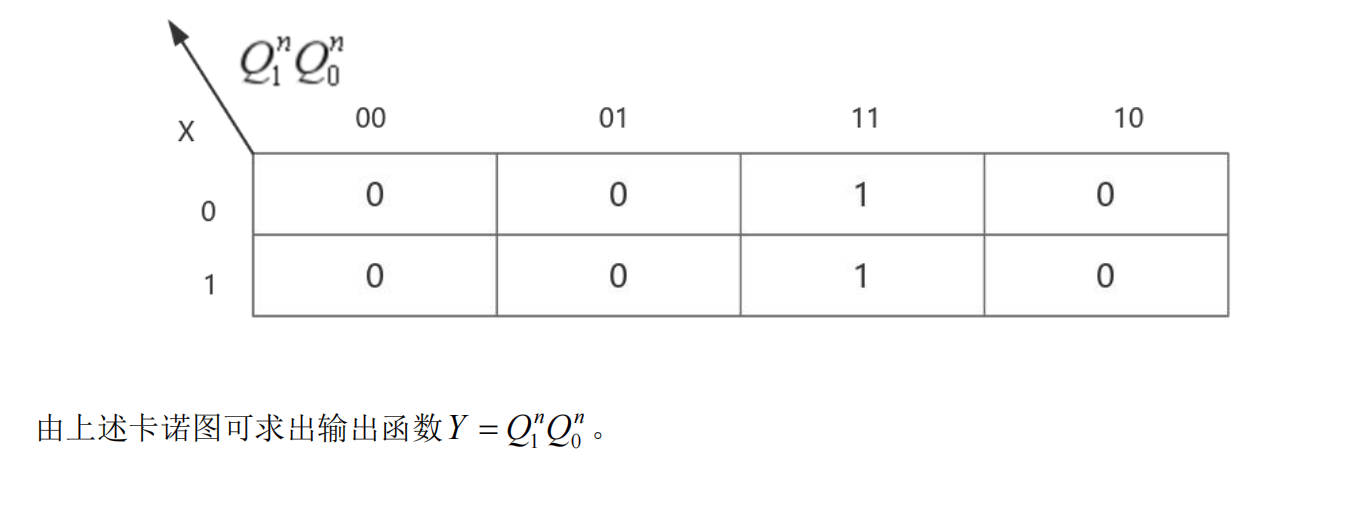

3、求输出函数

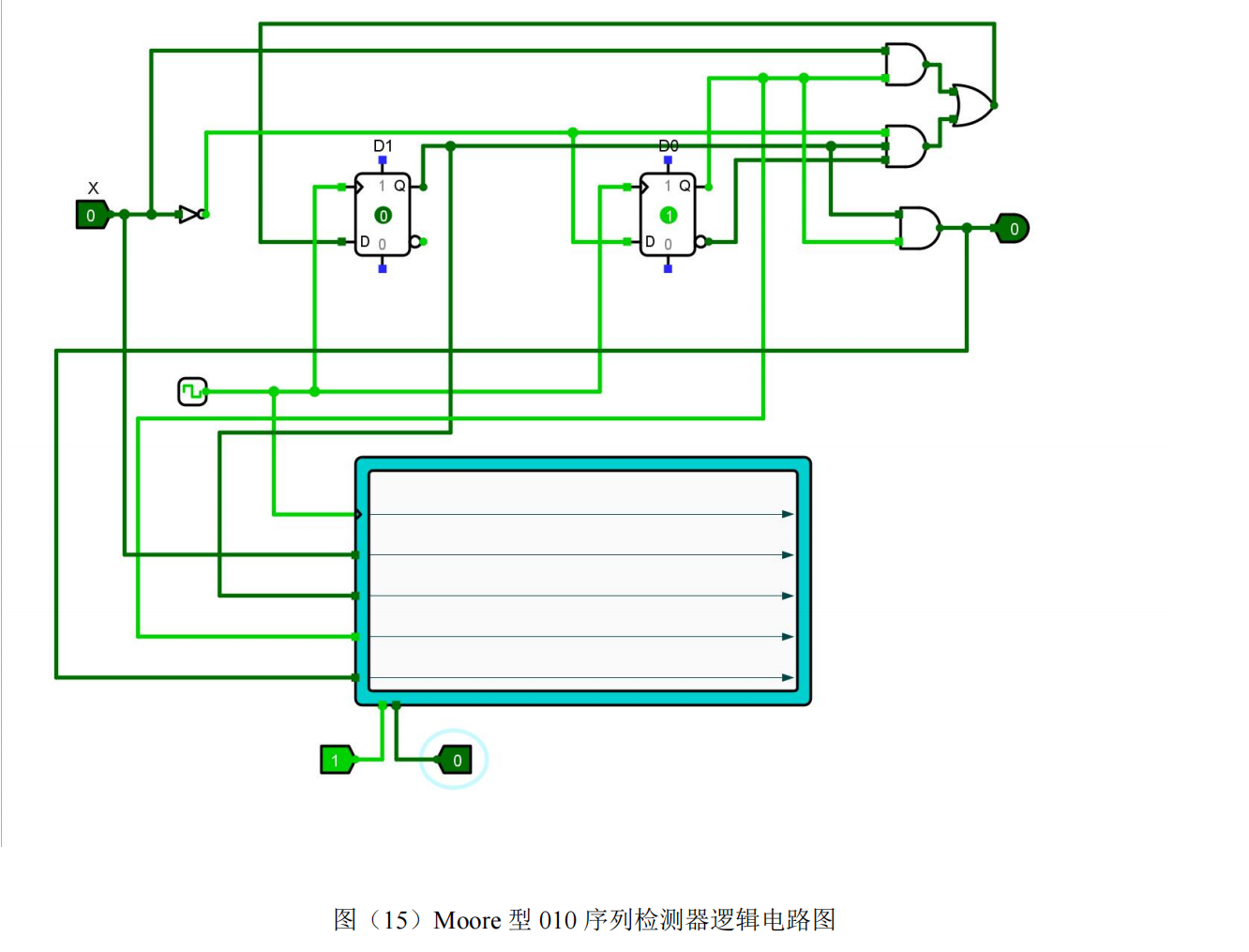

五、逻辑电路图

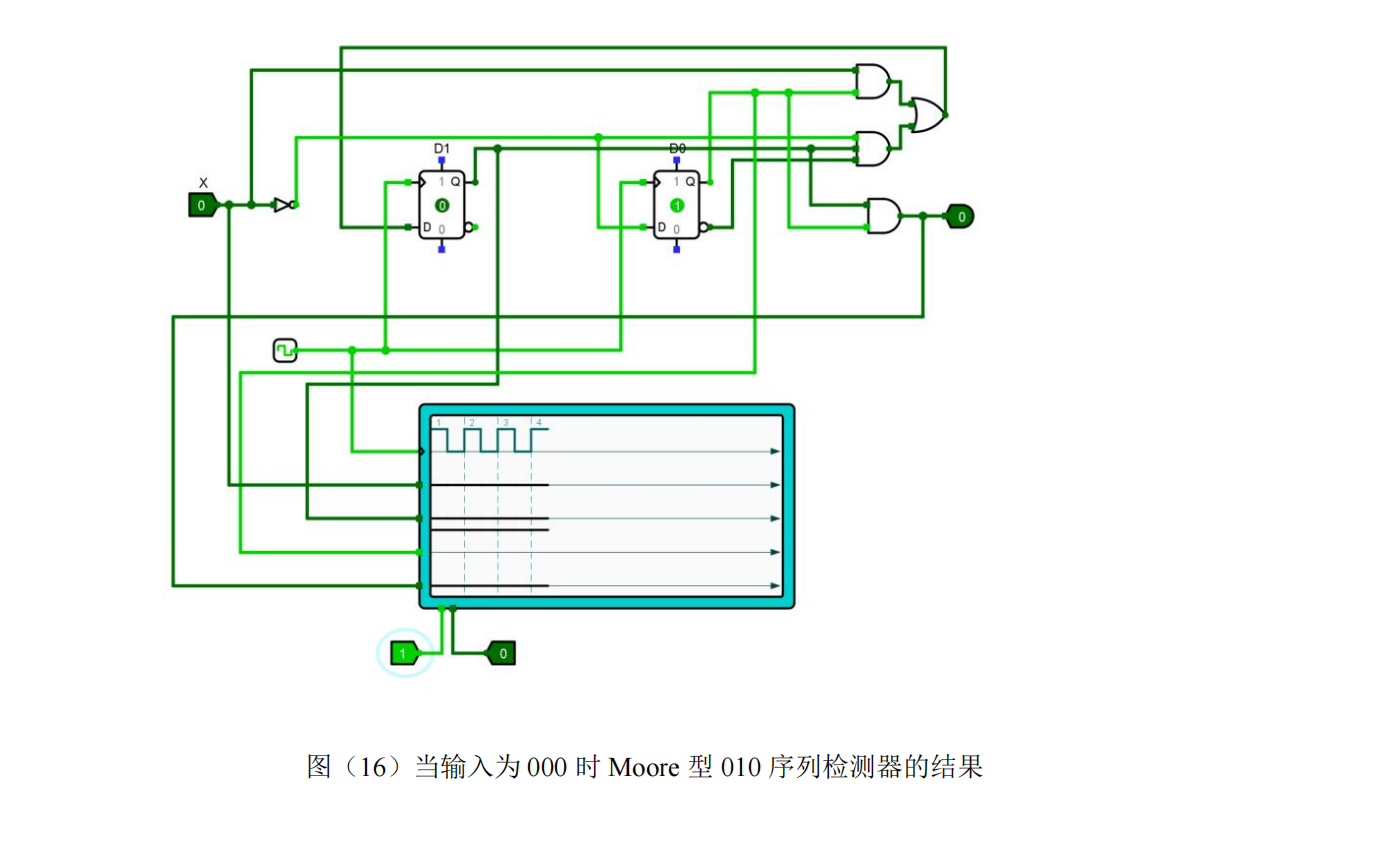

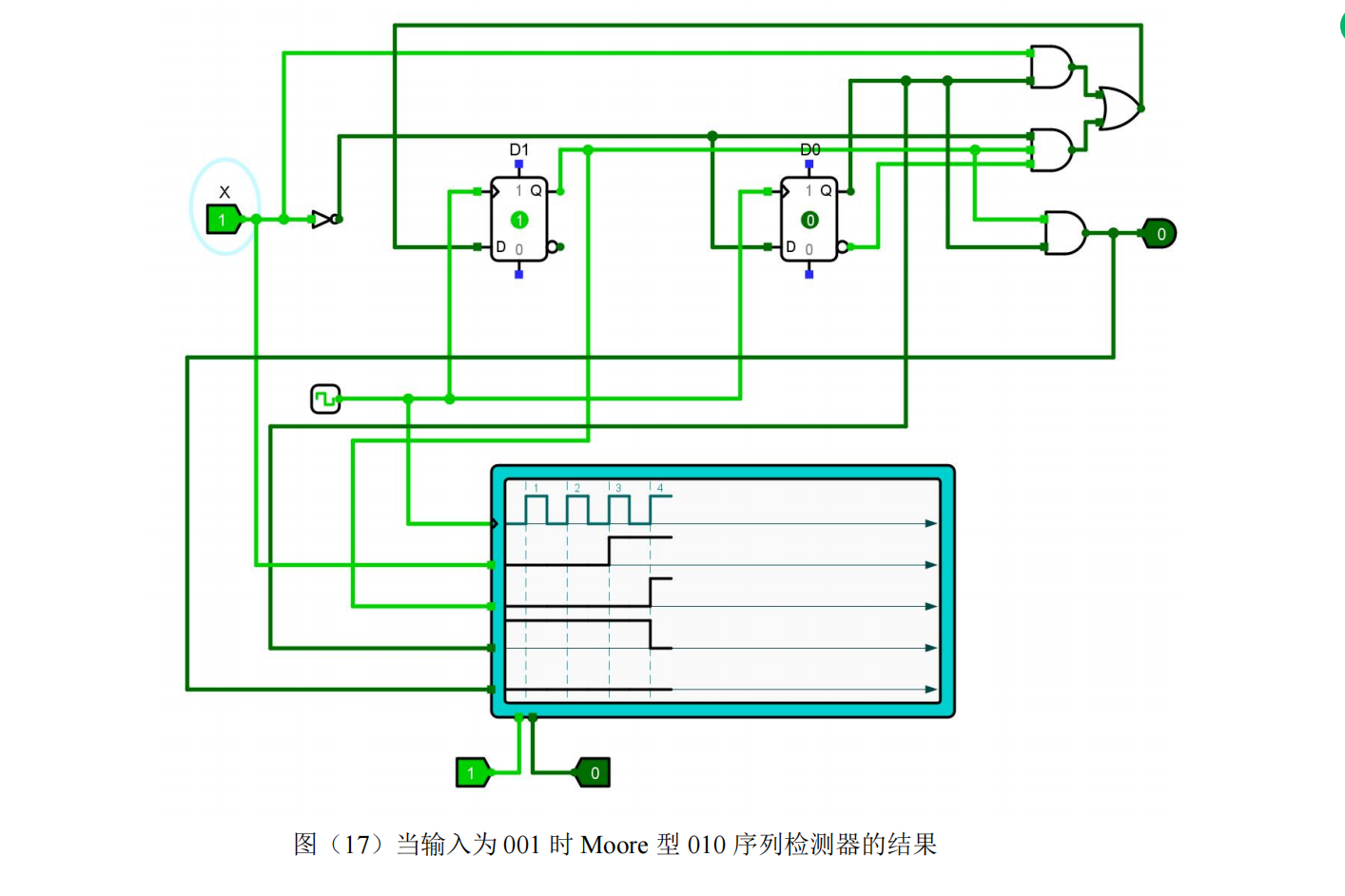

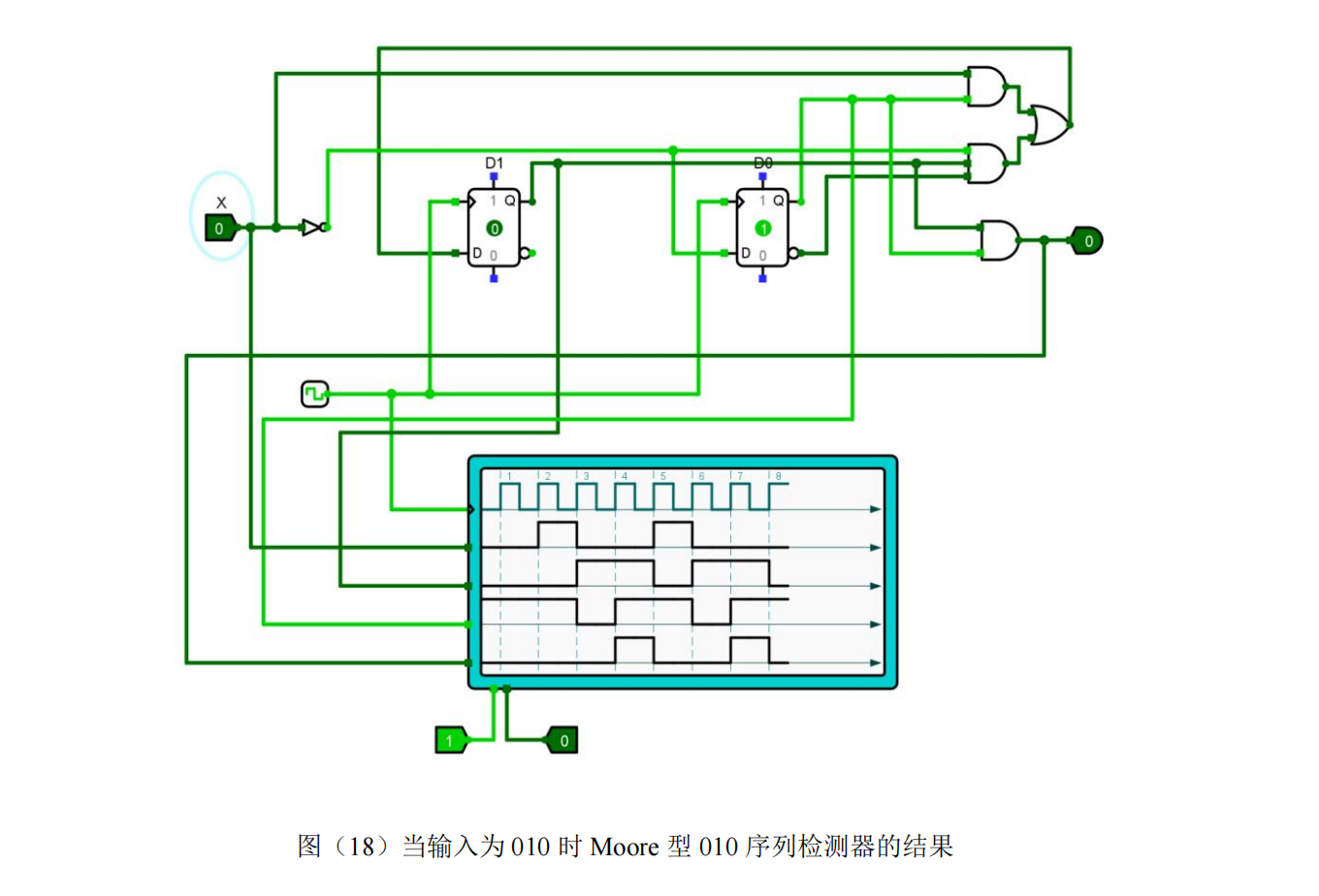

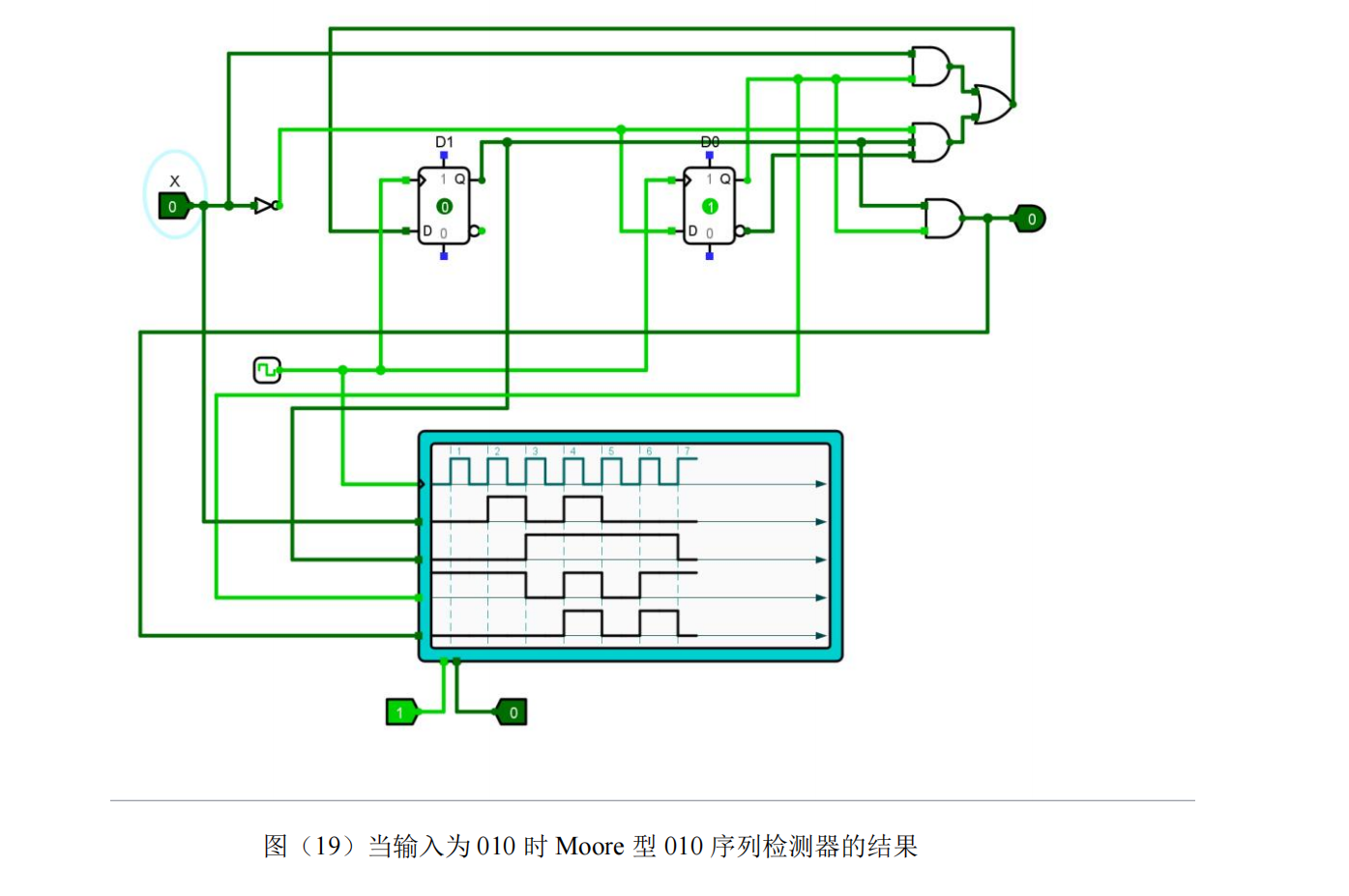

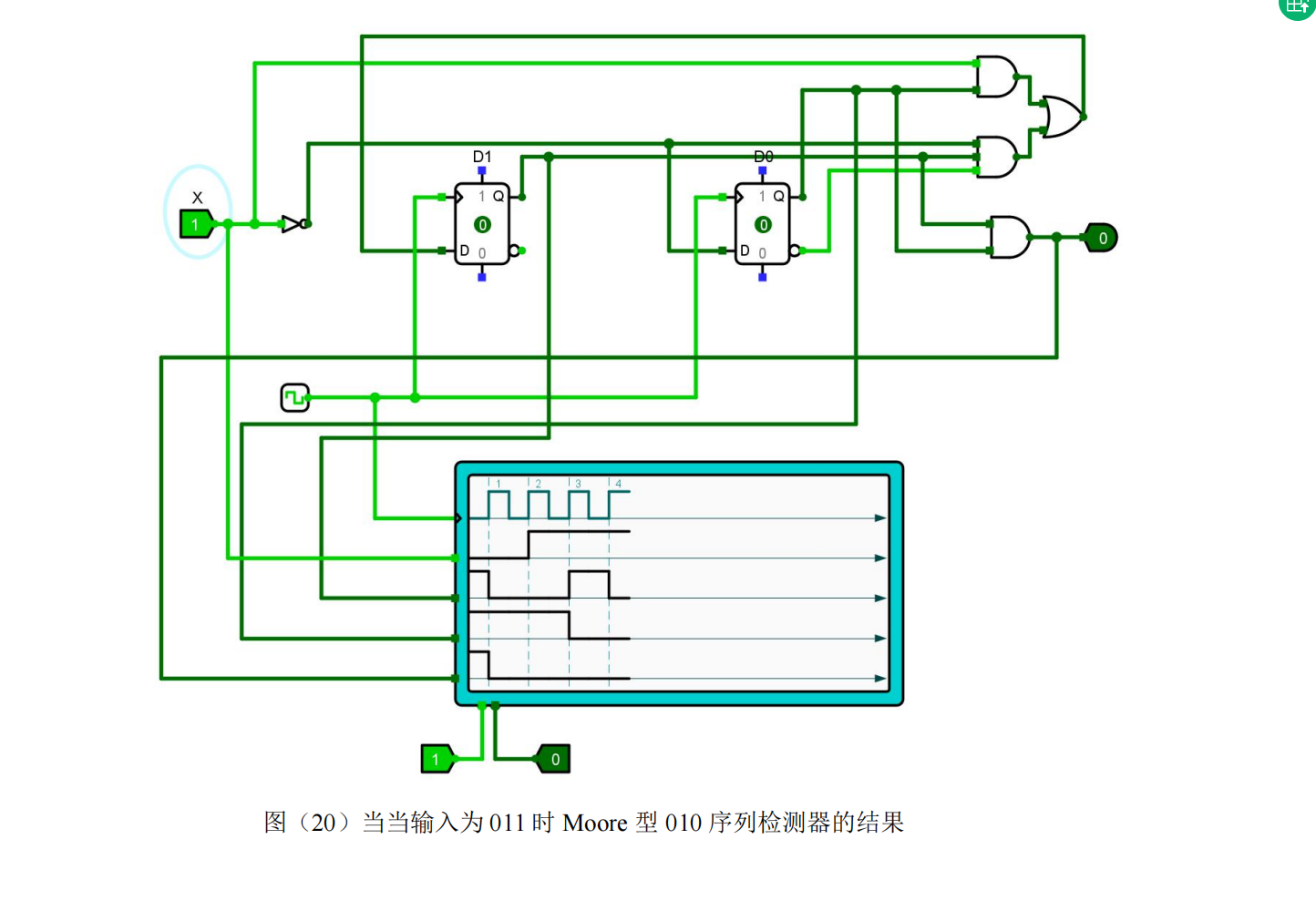

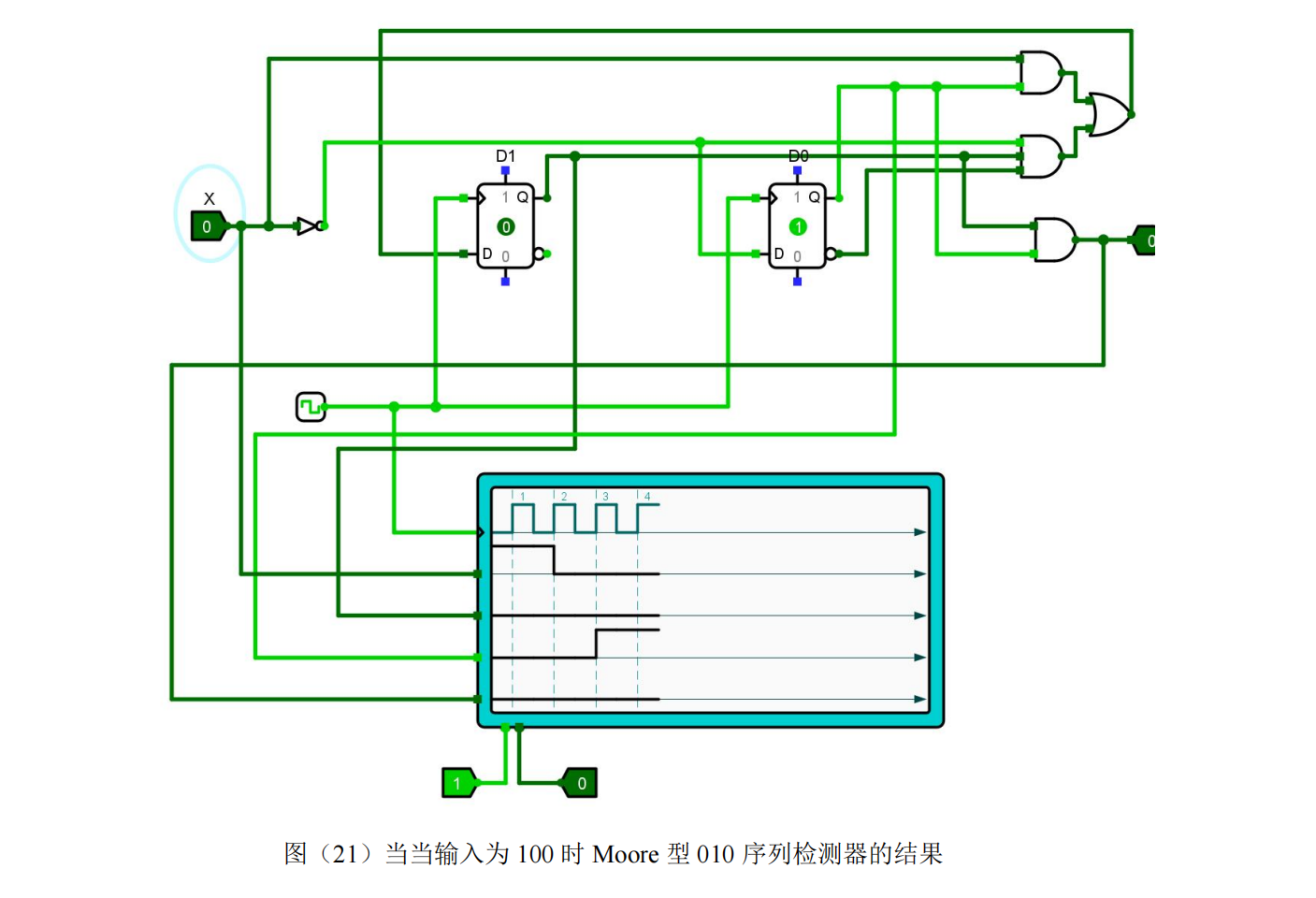

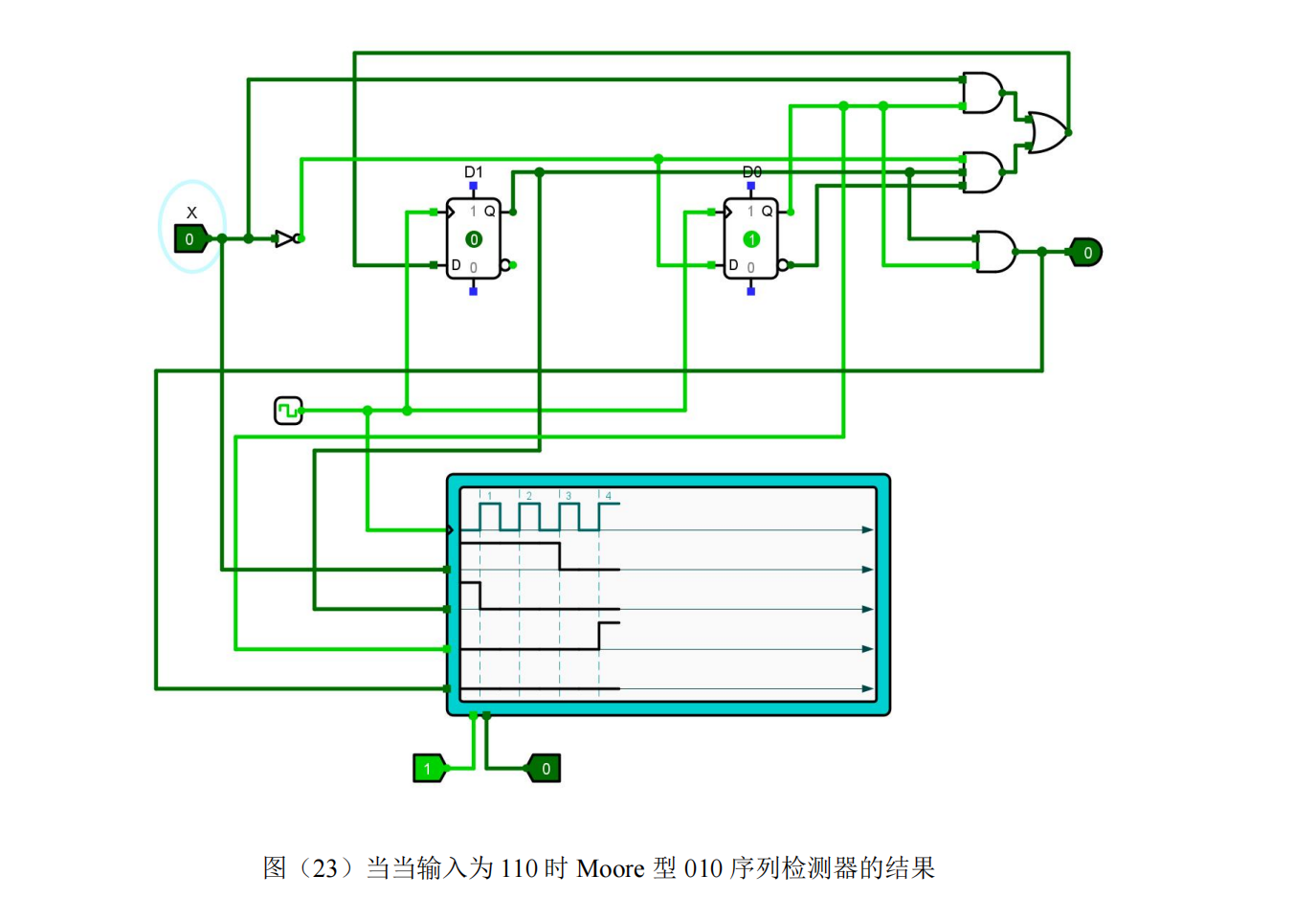

六、结果分析

1、当输入为 000 时输出 Y 为 0。

2、当输入为 001 时,输出 Y 为 0。

3、当输入为 010 时,输出 Y 为 1。

4、当输入为 011 时输出 Y 为 0。

5、当输入为 100 时输出 Y 为 0。

6、当输入为 101 时输出 Y 为 0。

7、当输入为 110 时输出 Y 为 0。

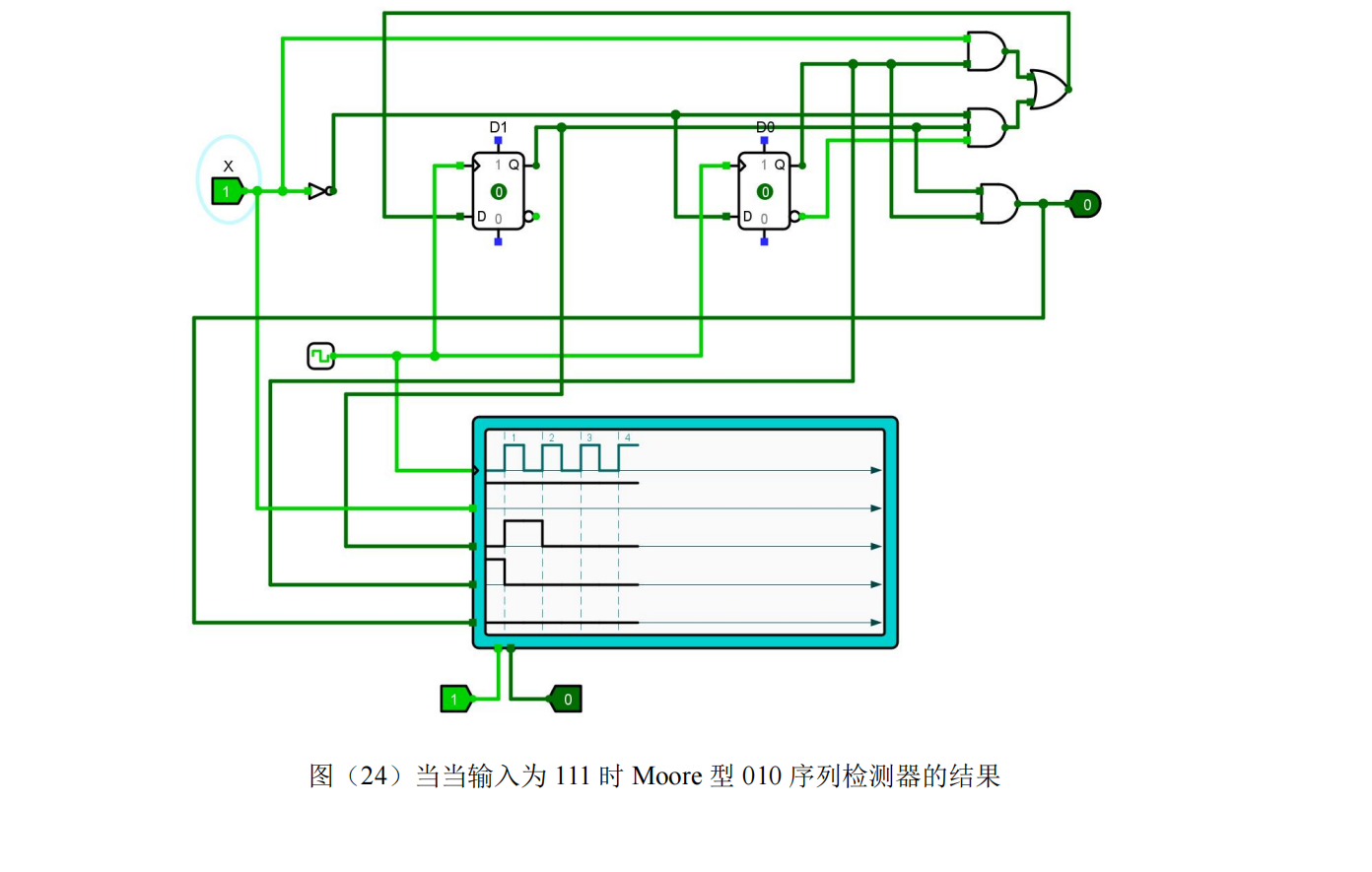

8、当输入为 111 时输出 Y 为 0。

由上图中示波器结果可知,当连续输入 010 后在输入 0,此时 D1 n D0 n 11而 Y 输出为 1。

当输入连续的 010 后紧接着在输入 10,此时 Y 输出任为 1,因此可以判断该电路是 010 重

叠的序列检测器。

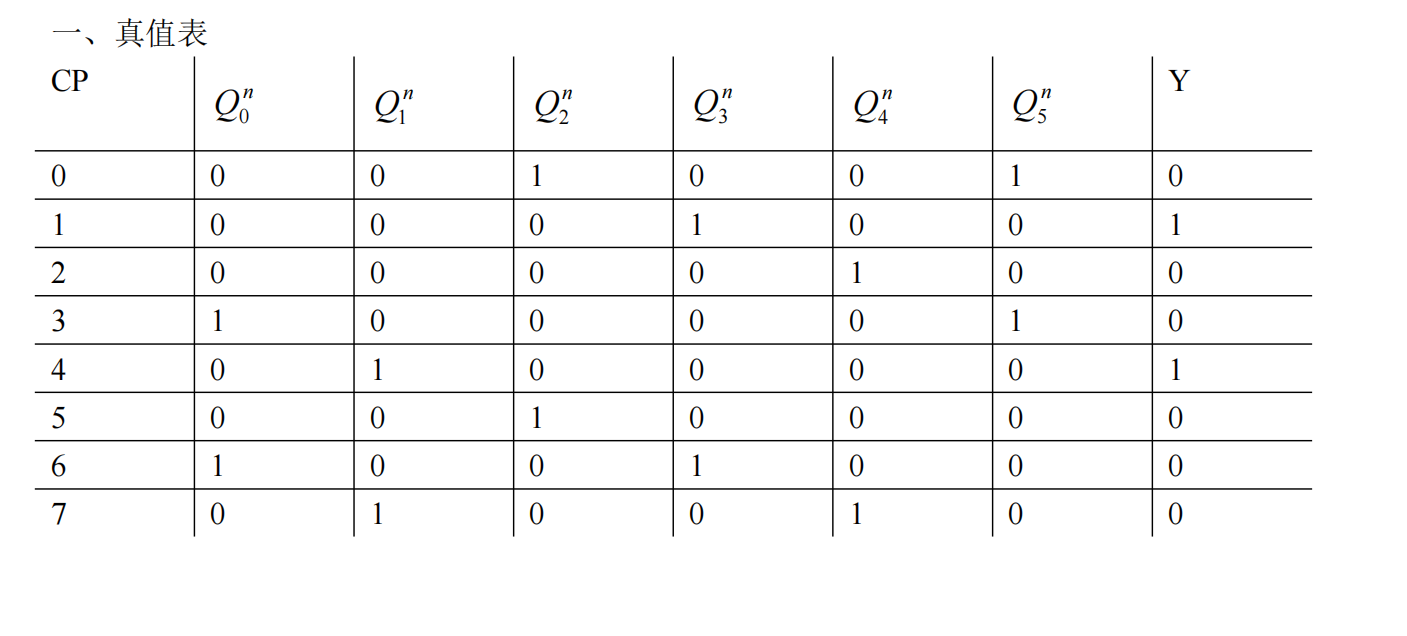

用移位寄存器设计 01001000 序列发生器

由上述真值表可知设计01001000序列发生器所需要的触发器个数超过4个所以这里不做讨论。

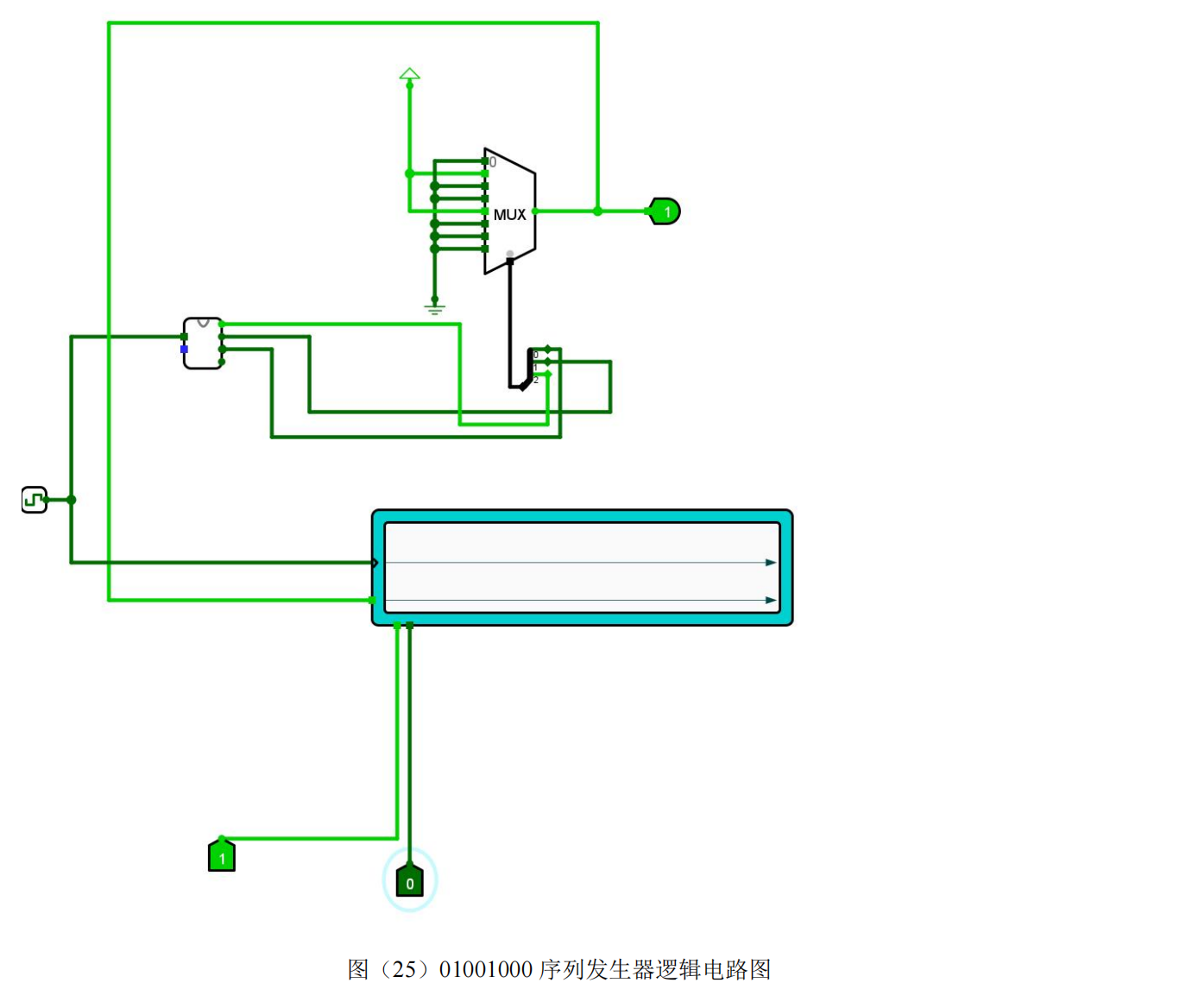

用加法器和选择器设计 01001000 序列发生器

一、设计思路

要产生“01001000”这样的 8 为序列,需要一个模为 8 的计数器,将计数器的初值设为 000,每来一个时钟脉冲,计数器加一,因此加法器可以实现 000 到 111 的状态变化,把加 法器的状态作为输出,将计数器的 3 为输出连接到八选一选择器的三个地址输入端,八选一 的数据输入端  按照“01001000”的顺序连接相应的电平,即

按照“01001000”的顺序连接相应的电平,即  接低电平,

接低电平,  接高 电平,

接高 电平,  ,,

,,  接低电平,

接低电平,  接高电平,

接高电平,  ,

,  ,

,  接低电平。

接低电平。

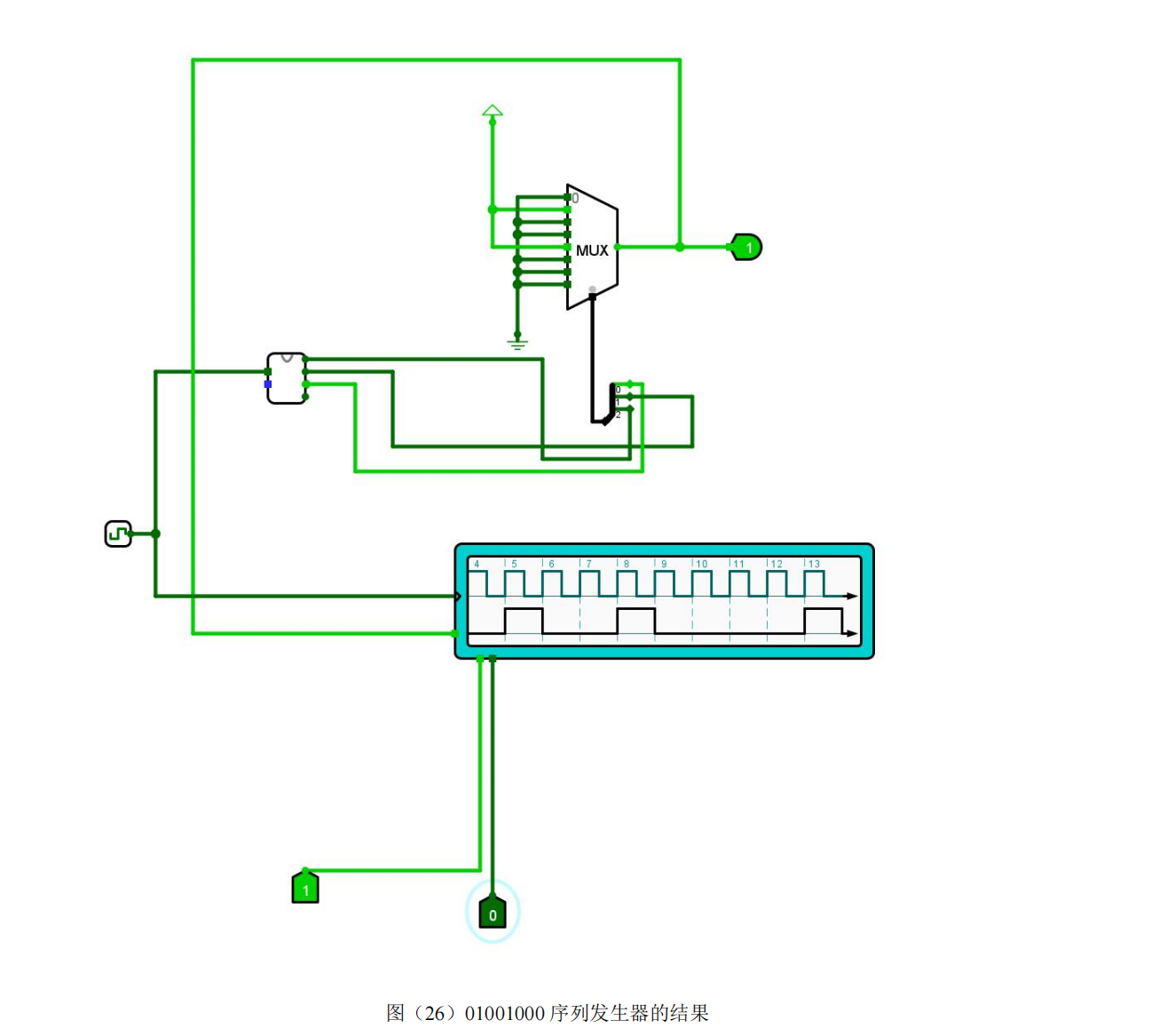

二、逻辑电路图

三、结果分析

当时钟脉冲到来时,计数器的值会不断变化,其输出作为八选一选择器的地址信号。根 据计数器的不同取值,八选一选择器会从 D0 D7 中选择相应的数据输出,从而依次输出 “01001000”序列,如上图所示。

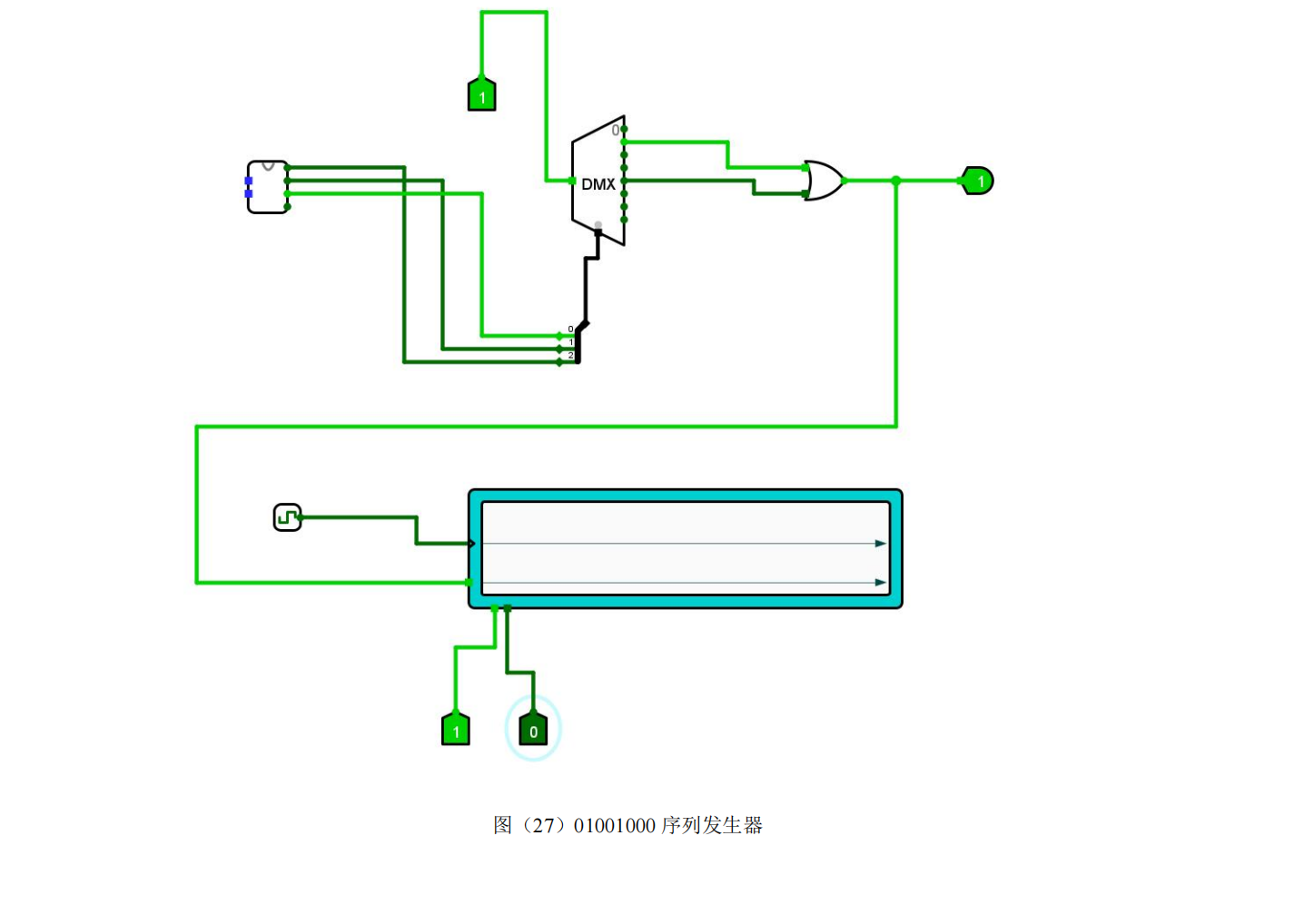

用计数器和译码器制作 01001000 序列发生器

一.设计思路

要产生“01001000”这样的 8 为序列,需要一个模为 8 的计数器,将计数器的初值设为 000,每来一个时钟脉冲,计数器加一,因此加法器可以实现 000 到 111 的状态变化,把加 法器的状态作为输出。由于译码器有三个输入端 A,B,C,八个输出端 Y0 Y7 ,当输入端 输入不同的二进制编码时,对应的输出端为高电平有效,其余输出为低电平,因此将计数器 的三位输出连接到译码器的 A,B,C 输入端,这样当当计数器变化时,译码器会根据二进 制码使相应的输出端有效,然后将译码器的 Y1, Y4 连接到一个或们上,当输入为 000 时 Y0 输 出高电平其余输出低电平,因此或门输出低电平,当输入为 001 时 Y1 输出高电平其余输出 低电平因此或门输出高电平,依次类推。

二、逻辑电路图

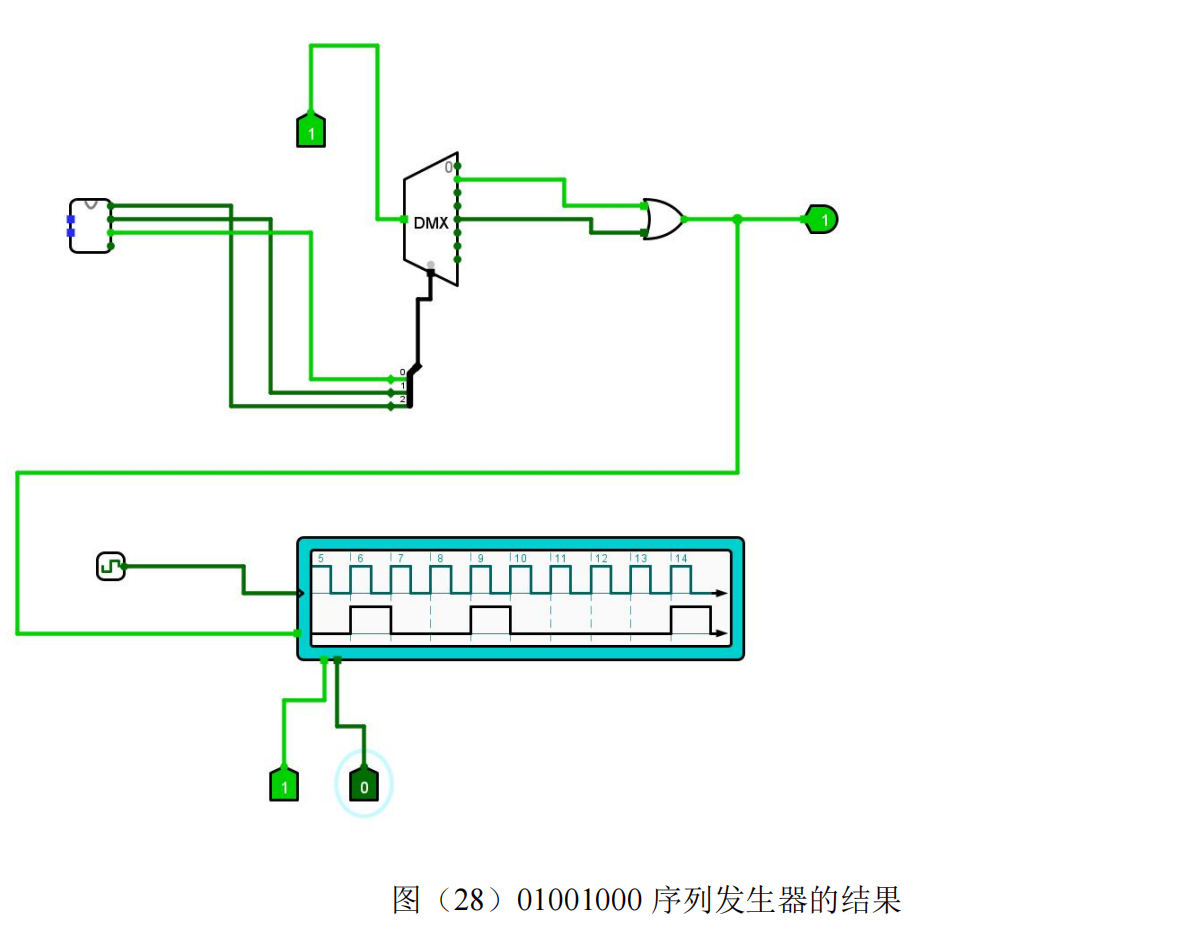

三、结果分析

当时钟脉冲到来时,计数器的值会不断变化,其输出作为八选一选择器的地址信号。根 据计数器的不同取值,译码器器会输出  中相应的数据,当输入为 000 时

中相应的数据,当输入为 000 时  输出高电 平其余输出低电平,因此或门输出低电平,当输入为 001 时

输出高电 平其余输出低电平,因此或门输出低电平,当输入为 001 时  输出高电平其余输出低电平 因此或门输出高电平,依次类推,从而依次输出“01001000”序列,如上图所示。

输出高电平其余输出低电平 因此或门输出高电平,依次类推,从而依次输出“01001000”序列,如上图所示。

总结:

本次实验分别实现了 Mealy 型的 010 序列检测器,Moore 型的 010 序列检测器,用计数 器和八选一选择器设计 01001000 序列发生器,用计数器和译码器设计了 01001000 序列发生 器,使我对序列检测器状态的转换,激励方程输出函数以及电路的设计都有了更加深入的认 识,在设计序列发生器时,也对计数器和选择器的结合,计数器和译码器的结合有了新的认 识。