FPGA开发全流程

FPGA开发全流程

FPGA(现场可编程门阵列)开发是一个涉及硬件设计、软件编程和系统调试的复杂流程,通常需要结合硬件描述语言(HDL)、开发工具和硬件平台。以下是 FPGA 开发的全流程详解,涵盖从需求分析到硬件调试的各个关键环节。

一、需求分析与架构设计

1. 明确设计目标

- 功能需求:确定 FPGA 需要实现的具体功能(如数字信号处理、图像处理、接口控制等)。

- 性能指标:定义时序要求(如时钟频率、建立 / 保持时间)、资源限制(如逻辑单元(LE)、存储块(BRAM)、DSP 单元数量)、功耗预算等。

- 接口规范:确定与外部设备的接口协议(如 UART、SPI、Ethernet、PCIe 等)。

2. 系统架构设计

- 模块化划分:将系统分解为多个子模块(如控制模块、数据处理模块、接口模块),明确模块间的数据流和控制逻辑。

- 算法选型:对于信号处理等场景,选择适合 FPGA 实现的算法(如并行计算、流水线设计)。

- 硬件 / 软件划分:确定哪些功能由 FPGA 硬件实现,哪些由嵌入式软件(如 FPGA 内的软核 CPU,如 Xilinx MicroBlaze、Altera Nios II)实现。

二、设计输入

设计输入是将架构转化为 FPGA 可识别的描述形式,主要包括以下方式:

1. 硬件描述语言(HDL)

- Verilog/VHDL:最常用的硬件描述语言,用于编写 RTL(寄存器传输级)代码。

- 注意事项:确保代码可综合(避免使用不可综合的语句,如延时函数),遵循模块化设计原则。

module adder (input [31:0] a,input [31:0] b,output reg [31:0] sum,input clk,input en

);always @(posedge clk) beginif (en) sum <= a + b;end

endmodule2. 原理图输入

- 通过图形化界面连接元件符号(如门电路、IP 核),适合简单电路或快速原型设计,但大规模设计中较少使用。

3. IP 核复用

- 调用厂商或第三方提供的预验证 IP 核(如 DSP 核、PCIe 控制器、存储器控制器),缩短开发周期。

- 主流 FPGA 厂商(Xilinx、Intel/Altera)提供丰富的 IP 库,支持参数化配置。

4.RTL级代码讲解

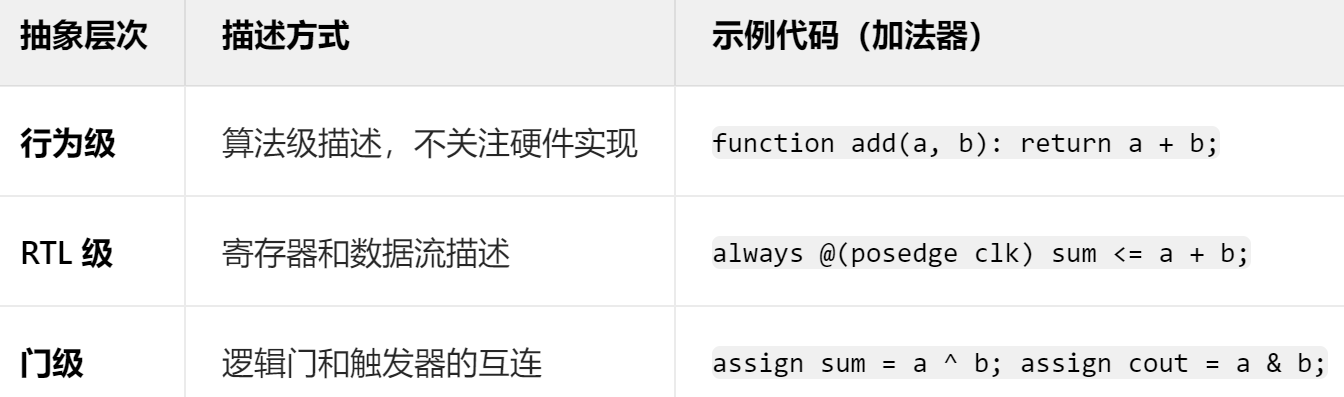

RTL(寄存器传输级)代码是硬件描述语言(HDL,如 Verilog 或 VHDL)编写的一种抽象层次,用于描述数字电路的行为和结构。它介于行为级描述(更抽象)和门级网表(更具体)之间,是 FPGA/ASIC 设计中最常用的实现方式。

RTL 代码的特点

-

可综合(Synthesizable):RTL 代码必须能被综合工具转换为物理电路(门级网表),因此需遵循可综合编码规范(如避免不可综合的延时语句

#10)。 -

时序明确:同步逻辑使用

always @(posedge clk)(Verilog)或process(clk)(VHDL)描述,确保时序可预测。 -

模块化:将系统分解为多个独立模块,通过端口连接,便于复用和验证。

三、逻辑综合(Synthesis)

1. 综合的目标

- 将 RTL 代码转换为门级网表(Netlist),映射到 FPGA 的基本逻辑单元(如查找表 LUT、触发器 FF)。

- 工具:Xilinx Vivado、Intel Quartus Prime、Synopsys Design Compiler 等。

2. 关键步骤

- 约束文件编写:使用 SDC(Synopsys Design Constraints)文件定义时序约束(如时钟频率、输入输出延迟)、面积 / 功耗优化目标。

create_clock -name clk -period 10 [get_ports clk] # 100MHz时钟约束

set_input_delay -clock clk -max 5 [get_ports a] # 输入延迟约束- 综合优化:工具根据约束自动优化电路结构,如寄存器重定时(Retiming)、资源共享(Resource Sharing)。

四、功能仿真(前仿真)

1. 仿真目的

- 在综合前验证 RTL 代码的逻辑正确性,不考虑 FPGA 的物理延迟。

2. 仿真流程

- 测试用例编写:使用 HDL 或工具自带语言(如 SystemVerilog)编写测试平台(Testbench),模拟输入激励并捕获输出结果。

- 工具:ModelSim、Vivado Simulator、Questasim 等。

module tb_adder;reg [31:0] a, b;reg clk, en;wire [31:0] sum;adder uut (.a(a), .b(b), .sum(sum), .clk(clk), .en(en));initial beginclk = 0; forever #5 clk = ~clk; // 生成100MHz时钟endinitial begina = 32'd1; b = 32'd2; en = 1; #20;a = 32'd3; b = 32'd4; en = 1; #20;en = 0; #20;$finish;endinitial $monitor("Time=%t, Sum=%d", $time, sum);

endmodule五、布局布线(Place & Route)

1. 目标

- 将综合后的网表映射到 FPGA 的物理资源上,完成逻辑单元的布局(Placement)和信号连线(Routing)。

- 工具:Vivado、Quartus Prime 等厂商专用工具。

2. 关键步骤

- 物理约束:通过 UCF/XDC 文件指定引脚分配(如 FPGA 引脚与外部器件的连接)、区域约束(将特定模块固定到 FPGA 的某个区域)。

- 时序收敛:工具自动调整布局布线以满足时序约束,可能需要多次迭代优化(如调整时钟分频、插入流水线寄存器)。

六、时序仿真(后仿真)

1. 仿真目的

- 验证布局布线后的电路时序是否满足要求,包含 FPGA 内部的实际延迟(如 LUT 延迟、布线延迟)。

2. 特点

- 仿真速度较慢,但结果更接近实际硬件行为。

- 需从布局布线结果中提取延迟信息(如 SDF 文件),反标到仿真模型中。

七、生成编程文件

1. 比特流生成

- 工具生成 FPGA 可识别的编程文件,如 Xilinx 的

.bit文件、Intel 的.sof(实时调试)或.pof(固化到 Flash)文件。 - 支持多种配置模式:

- 主动模式:FPGA 主动从外部存储器(如 QSPI Flash)加载配置数据。

- 被动模式:通过主机(如 MCU)或下载器将数据写入 FPGA。

2. 固化配置

- 将

.bit文件转换为适合外部存储器的格式(如 Xilinx 的.mcs文件),实现上电自动加载。

八、硬件编程与调试

1. 下载到 FPGA

- 通过 JTAG 接口(如 Xilinx Platform Cable、Intel USB-Blaster)将编程文件写入 FPGA。

- 工具:Vivado Hardware Manager、Quartus Programmer。

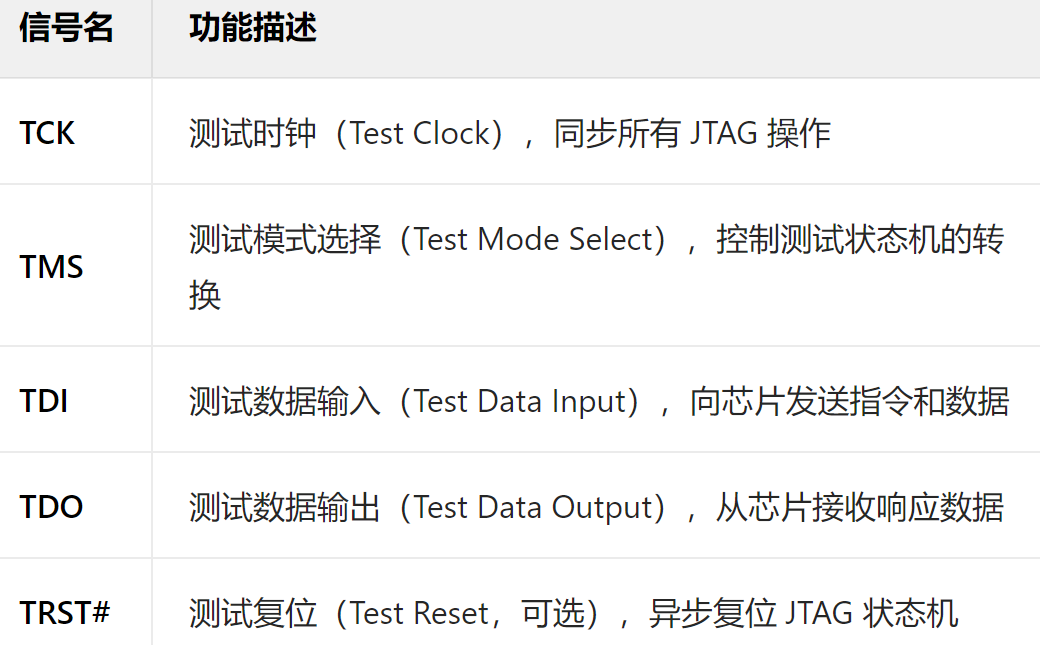

2. JTAG接口详解

JTAG 接口通常包含以下 5 个基本信号:

JTAG 的工作原理

JTAG 通过一个状态机(TAP,Test Access Port)控制测试流程,主要包含以下组件:

-

测试访问端口(TAP)控制器:由 TMS 信号驱动,根据 TMS 的时序组合切换不同状态(如 Run-Test/Idle、Select-DR-Scan 等)。

-

指令寄存器(IR):存储当前执行的指令(如 BYPASS、EXTEST、SAMPLE/PRELOAD)。

-

数据寄存器(DR):包含边界扫描寄存器、IDCODE 寄存器等,用于数据传输。

典型操作流程:

- 通过 TCK 和 TMS 将指令写入 IR(如选择边界扫描测试)。

- 将测试数据通过 TDI 写入 DR(如向某个引脚输出高电平)。

- 执行测试并通过 TDO 读取结果(如检测该引脚实际电平是否正确)。

3. 在线调试

- 逻辑分析仪:使用 Xilinx ChipScope、Intel SignalTap II 等工具捕获 FPGA 内部信号,验证实时行为。

- 串口 / LED 调试:通过 UART 输出状态信息,或利用 LED 指示灯监控关键信号。

- 时序分析:使用工具内置的时序分析器检查时序裕量(Slack),定位时序违规路径。

九、系统集成与验证

1. 联合调试

- 将 FPGA 与周边电路(如 CPU、传感器、存储器)组合,验证整个系统的功能和性能。

- 测试内容:接口兼容性、数据吞吐率、抗干扰能力等。

2. 优化与迭代

- 若发现功能错误或性能不达标,需回溯到设计输入、综合或布局布线阶段调整(如修改代码、优化约束、更换 IP 核)。

十、开发工具链