79、modelsim单独仿真altera带IP核的文件

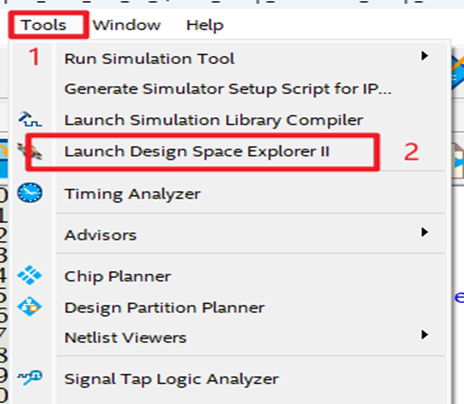

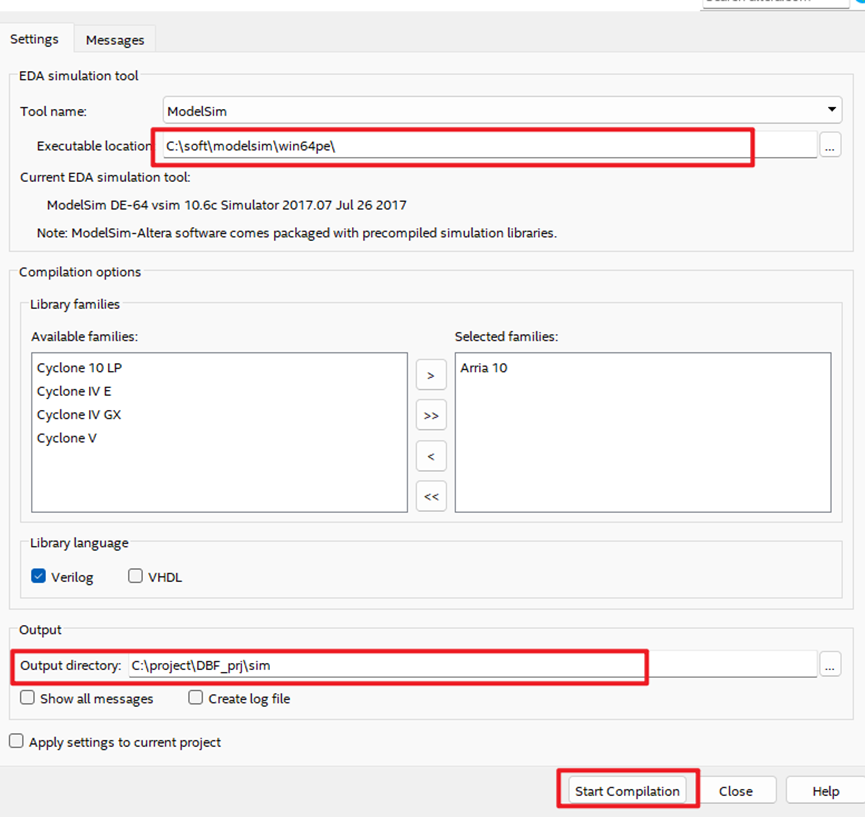

1.编译 quartus 仿真库(如果有就不用编译了)

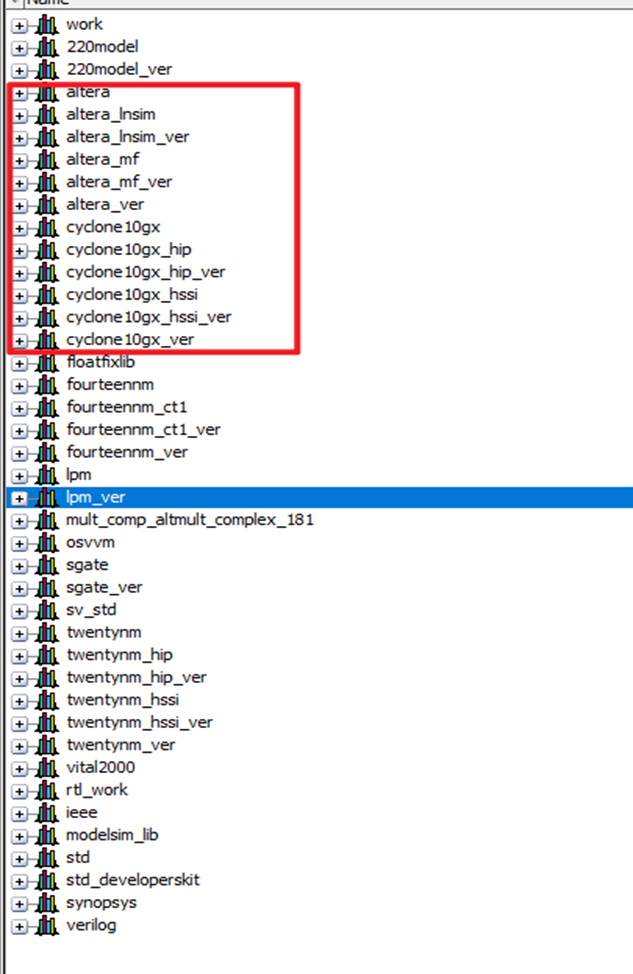

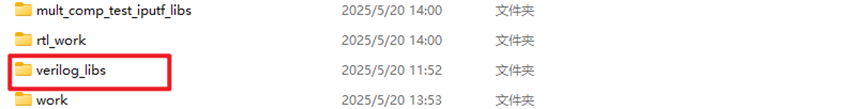

编译完成后 sim 文件夹中产生一个 verilog_libs 文件夹,打开文件夹

以上便是编译产生的库,将库添加到 modelsim 中也就是观察此文件中的 modelsim.ini 与 modelsim 安装目录下此文件的差异,将没有的部分复制粘贴进去就行。然后打开 modelsim 就会有以上的库。

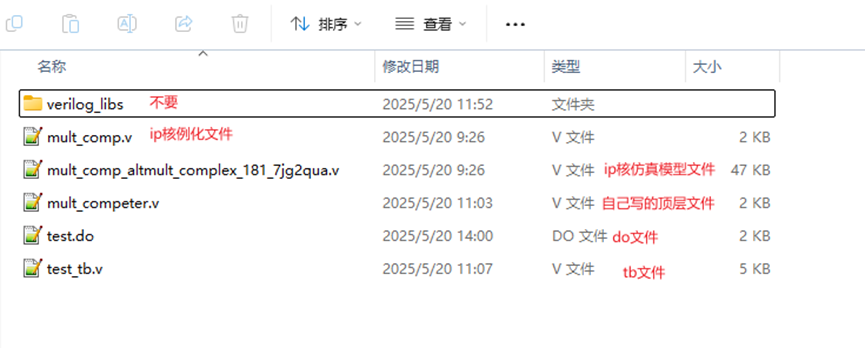

2.新建仿真文件夹中放入以下文件

当然也可以不放入同一文件夹下,此时 do 文件需要用目录去搜索。

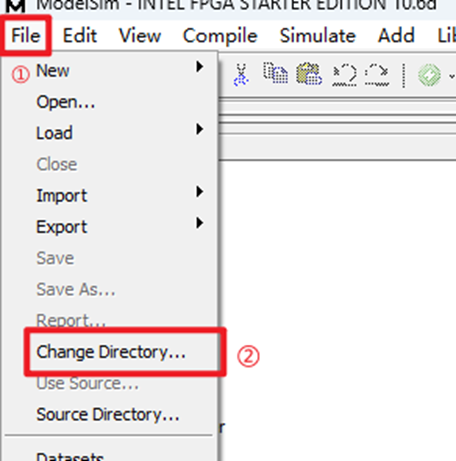

3.打开 modelsim 新建工程添加代码编译

选择到前面新建的仿真目录下,添加代码编译。

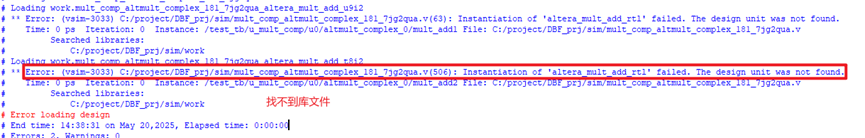

在 work 库下直接仿真出现如下错误

直接采用 test.do 文件仿真即可

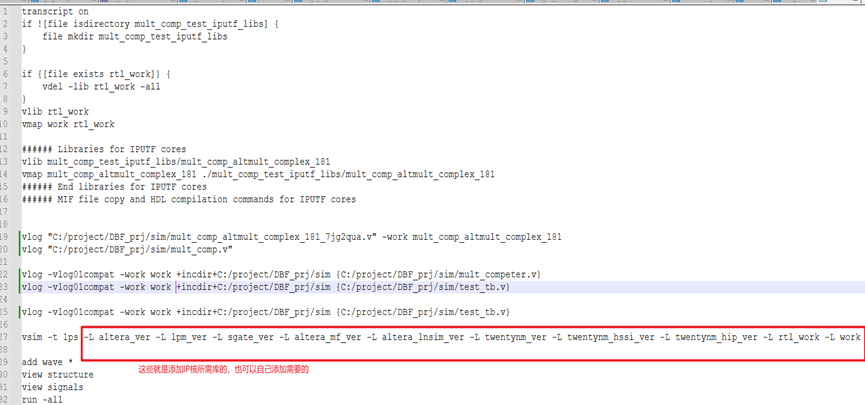

transcript on

if ![file isdirectory mult_comp_test_iputf_libs] {file mkdir mult_comp_test_iputf_libs

}if {[file exists rtl_work]} {vdel -lib rtl_work -all

}

vlib rtl_work

vmap work rtl_work###### Libraries for IPUTF cores

vlib mult_comp_test_iputf_libs/mult_comp_altmult_complex_181

vmap mult_comp_altmult_complex_181 ./mult_comp_test_iputf_libs/mult_comp_altmult_complex_181

###### End libraries for IPUTF cores

###### MIF file copy and HDL compilation commands for IPUTF cores vlog "C:/project/DBF_prj/sim/mult_comp_altmult_complex_181_7jg2qua.v" -work mult_comp_altmult_complex_181

vlog "C:/project/DBF_prj/sim/mult_comp.v" vlog -vlog01compat -work work +incdir+C:/project/DBF_prj/sim {C:/project/DBF_prj/sim/mult_competer.v}

vlog -vlog01compat -work work +incdir+C:/project/DBF_prj/sim {C:/project/DBF_prj/sim/test_tb.v}vlog -vlog01compat -work work +incdir+C:/project/DBF_prj/sim {C:/project/DBF_prj/sim/test_tb.v}vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -L rtl_work -L work -L mult_comp_altmult_complex_181 -voptargs="+acc" test_tbadd wave *

view structure

view signals

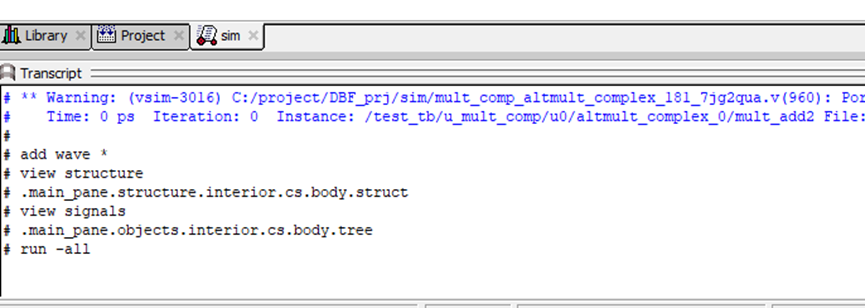

run -all然后在命令窗口输入 do test.do 即可运行仿真

仿真成功。

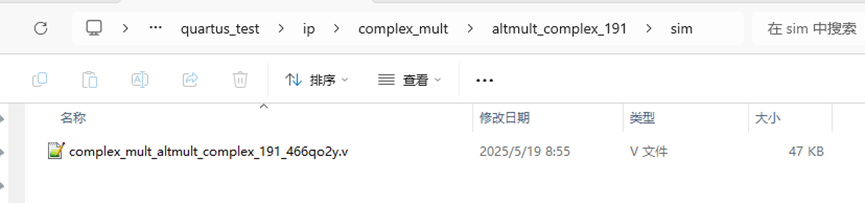

注意仿真模型在 IP 目录下