ARM A64 STR指令

ARM A64 STR指令

- 1 STR (immediate)

- 1.1 Post-index

- 1.1.1 32-bit variant

- 1.1.2 64-bit variant

- 1.2 Pre-index

- 1.2.1 32-bit variant

- 1.2.2 64-bit variant

- 1.3 Unsigned offset

- 1.3.1 32-bit variant

- 1.3.2 64-bit variant

- 1.4 Assembler symbols

- 2 STR (register)

- 2.1 32-bit variant

- 2.2 64-bit variant

- 2.3 Assembler symbols

- 3 STRB (immediate)

- 3.1 Post-index

- 3.2 Pre-index

- 3.3 Unsigned offset

- 4 STRB (register)

- 4.1 Extended register variant

- 4.2 Shifted register variant

- 5 STRH (immediate)

- 5.1 Post-index

- 5.2 Pre-index

- 5.3 Unsigned offset

- 6 STRH (register)

- 6.1 Encoding

- 6.2 Assembler symbols

Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile

1 STR (immediate)

Store Register (immediate) stores a word or a doubleword from a register to memory. The address that is used for the store is calculated from a base register and an immediate offset.

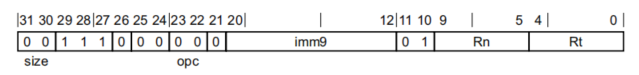

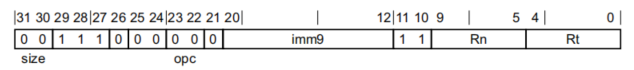

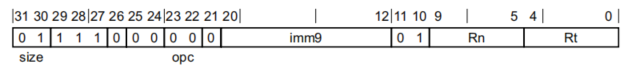

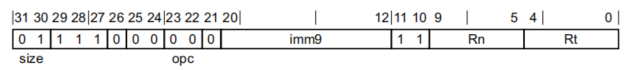

1.1 Post-index

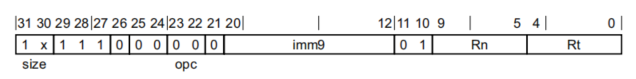

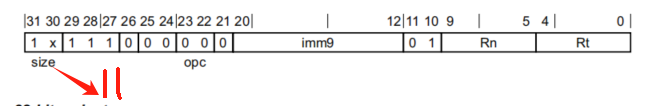

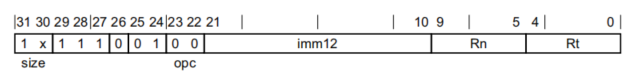

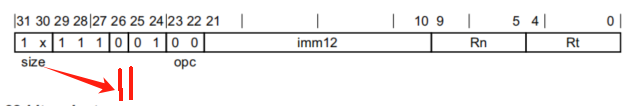

1.1.1 32-bit variant

Applies when size == 10.

STR <Wt>, [<Xn|SP>], #<simm>

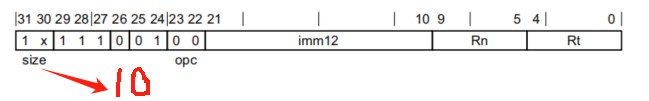

1.1.2 64-bit variant

Applies when size == 11.

STR <Xt>, [<Xn|SP>], #<simm>

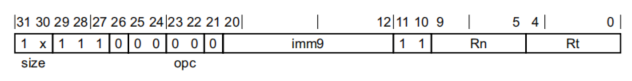

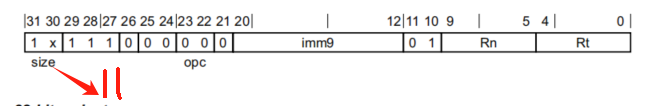

1.2 Pre-index

1.2.1 32-bit variant

Applies when size == 10.

STR <Wt>, [<Xn|SP>], #<simm>

1.2.2 64-bit variant

Applies when size == 11.

STR <Xt>, [<Xn|SP>], #<simm>

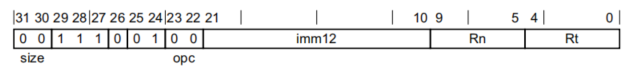

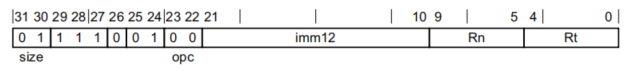

1.3 Unsigned offset

1.3.1 32-bit variant

Applies when size == 10.

STR <Wt>, [<Xn|SP>{, #<pimm>}]

1.3.2 64-bit variant

Applies when size == 11.

STR <Xt>, [<Xn|SP>{, #<pimm>}]

1.4 Assembler symbols

<Wt>

Is the 32-bit name of the general-purpose register to be transferred, encoded in the “Rt” field.

<Xt>

Is the 64-bit name of the general-purpose register to be transferred, encoded in the “Rt” field.

<Xn|SP>

Is the 64-bit name of the general-purpose base register or stack pointer, encoded in the “Rn” field.

<simm>

Is the signed immediate byte offset, in the range -256 to 255, encoded in the “imm9” field.

<pimm>

For the 32-bit variant: is the optional positive immediate byte offset, a multiple of 4 in the range 0 to 16380, defaulting to 0 and encoded in the “imm12” field as <pimm>/4.

For the 64-bit variant: is the optional positive immediate byte offset, a multiple of 8 in the range 0 to 32760, defaulting to 0 and encoded in the “imm12” field as <pimm>/8.

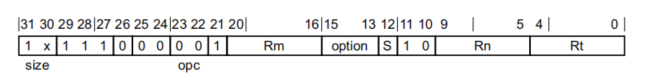

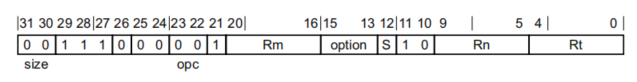

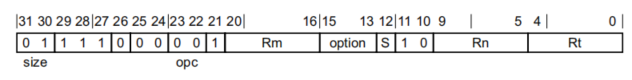

2 STR (register)

Store Register (register) calculates an address from a base register value and an offset register value, and stores a 32-bit word or a 64-bit doubleword to the calculated address, from a register.

The instruction uses an offset addressing mode, that calculates the address used for the memory access from a base register value and an offset register value. The offset can be optionally shifted and extended.

2.1 32-bit variant

Applies when size == 10.

STR <Wt>, [<Xn|SP>, (<Wm>|<Xm>){, <extend> {<amount>}}]

2.2 64-bit variant

Applies when size == 11.

STR <Xt>, [<Xn|SP>, (<Wm>|<Xm>){, <extend> {<amount>}}]

2.3 Assembler symbols

<Wt> Is the 32-bit name of the general-purpose register to be transferred, encoded in the “Rt” field.

<Xt> Is the 64-bit name of the general-purpose register to be transferred, encoded in the “Rt” field.

<Xn|SP> Is the 64-bit name of the general-purpose base register or stack pointer, encoded in the “Rn” field.

<Wm> When option<0> is set to 0, is the 32-bit name of the general-purpose index register, encoded in the “Rm” field.

<Xm> When option<0> is set to 1, is the 64-bit name of the general-purpose index register, encoded in the “Rm” field.

<extend> Is the index extend/shift specifier, defaulting to LSL, and which must be omitted for the LSL option when <amount> is omitted. encoded in the “option” field. It can have the following values:

UXTW when option = 010

LSL when option = 011

SXTW when option = 110

SXTX when option = 111

<amount> For the 32-bit variant: is the index shift amount, optional only when <extend> is not LSL. Where it is permitted to be optional, it defaults to #0. It is encoded in the “S” field. It can have the following values:

#0 when S = 0

#2 when S = 1

For the 64-bit variant: is the index shift amount, optional only when <extend> is not LSL. Where it is permitted to be optional, it defaults to #0. It is encoded in the “S” field. It can have the following

values:

#0 when S = 0

#3 when S = 1

3 STRB (immediate)

Store Register Byte (immediate) stores the least significant byte of a 32-bit register to memory. The address that is used for the store is calculated from a base register and an immediate offset.

3.1 Post-index

STRB <Wt>, [<Xn|SP>], #<simm>

3.2 Pre-index

STRB <Wt>, [<Xn|SP>, #<simm>]!

3.3 Unsigned offset

STRB <Wt>, [<Xn|SP>{, #<pimm>}]

4 STRB (register)

Store Register Byte (register) calculates an address from a base register value and an offset register value, and stores a byte from a 32-bit register to the calculated address.

The instruction uses an offset addressing mode, that calculates the address used for the memory access from a base register value and an offset register value. The offset can be optionally shifted and extended.

4.1 Extended register variant

Applies when option != 011.

STRB <Wt>, [<Xn|SP>, (<Wm>|<Xm>), <extend> {<amount>}]

4.2 Shifted register variant

Applies when option == 011.

STRB <Wt>, [<Xn|SP>, <Xm>{, LSL <amount>}]

5 STRH (immediate)

Store Register Halfword (immediate) stores the least significant halfword of a 32-bit register to memory. The address that is used for the store is calculated from a base register and an immediate offset.

5.1 Post-index

STRH <Wt>, [<Xn|SP>], #<simm>

5.2 Pre-index

STRH <Wt>, [<Xn|SP>, #<simm>]!

5.3 Unsigned offset

STRH <Wt>, [<Xn|SP>{, #<pimm>}]

6 STRH (register)

Store Register Halfword (register) calculates an address from a base register value and an offset register value, and stores a halfword from a 32-bit register to the calculated address.

The instruction uses an offset addressing mode, that calculates the address used for the memory access from a base register value and an offset register value. The offset can be optionally shifted and extended.

6.1 Encoding

STRH <Wt>, [<Xn|SP>, (<Wm>|<Xm>){, <extend> {<amount>}}]

6.2 Assembler symbols

<Wt> Is the 32-bit name of the general-purpose register to be transferred, encoded in the “Rt” field.

<Xn|SP> Is the 64-bit name of the general-purpose base register or stack pointer, encoded in the “Rn” field.

<Wm> When option<0> is set to 0, is the 32-bit name of the general-purpose index register, encoded in the “Rm” field.

<Xm> When option<0> is set to 1, is the 64-bit name of the general-purpose index register, encoded in the “Rm” field.

<extend> Is the index extend/shift specifier, defaulting to LSL, and which must be omitted for the LSL option when <amount> is omitted. encoded in the “option” field. It can have the following values:

UXTW when option = 010

LSL when option = 011

SXTW when option = 110

SXTX when option = 111

<amount> Is the index shift amount, optional only when <extend> is not LSL. Where it is permitted to be optional, it defaults to #0. It is encoded in the “S” field. It can have the following values:

#0 when S = 0

#1 when S = 1