JESD204 ip核使用与例程分析(一)

JESD204 ip核使用与例程分析(一)

- JESD204理解

- JESD204 与JESD204 PHY成对使用原因

- JESD204B IP核

- JESD204B IP核特点

- JESD204B IP核配置

- 第一页

- 第二页

- 第三页

- 第四页

- JESD204 PHY IP核配置

- 第一页

- 第二页

JESD204理解

JESD204B是一种针对ADC、DAC设计的传输接口协议。此协议包含四层,

分别为:物理层、链路层、传输层、应用层。

物理层:约束接口规范(SERDES CML),串化,线速率等。

你要使用这个协议,你的电气接口,电气属性是什么样的

如JESD204B必须用SERDES接口,电瓶标准是CML。

链路层:并性数据组帧(添加控制位,结束位),8B/10B编码,链路建立。

传输层:链路建立之后,传输ADC的数据,以半字节为单位。

应用层:用户解析ADC数据并使用。

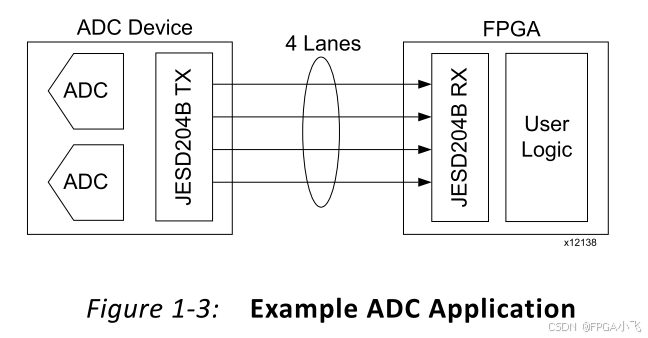

下图所示为JESD204 IP核例化为4通道接收器时与ADC芯片的应用,使用IP核后,用户只需要进行应用层逻辑开发:

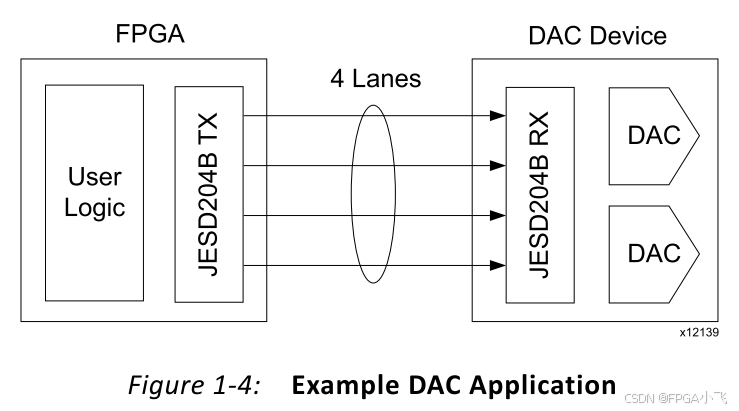

下图所示为JESD204 IP核例化为4通道发送器时与DAC芯片的应用:

JESD204从发布开始至今有四个版本,分别为JESD204、JESD204A、JESD204B、JESD204C,目前使用最多的是JESD204B,各个版本之间的差异如下所示。

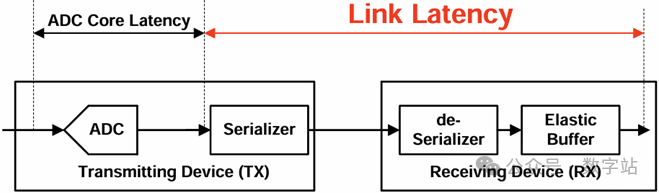

其中支持确定性延迟是JESD204B的特点,JESD204B链路的确定性延迟定义为串行数据从发送器(ADX或FPGA)的并行帧数据输入传播至接收器(DAC或接收端FPGA)并行帧数据输出所需的时间。

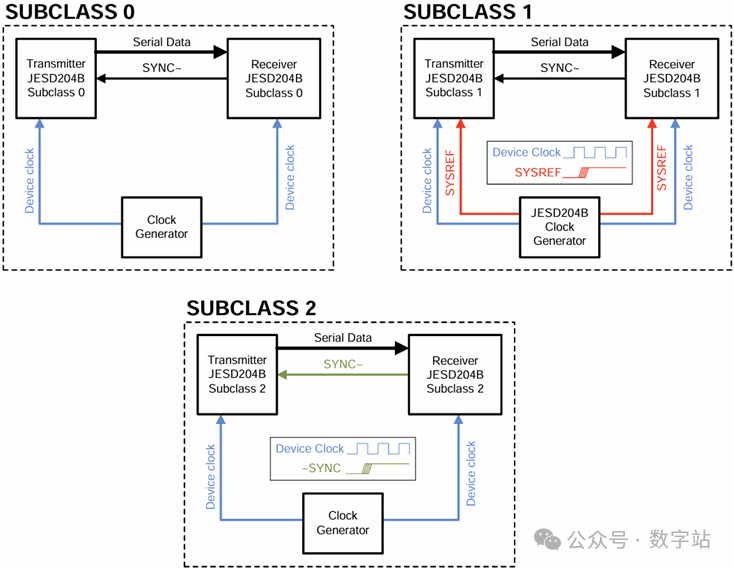

JESD204包含3种工作模式,如下所示。其中子类0是JESD204A的工作模式,不支持确定性延迟。子类1通过sysref和sync实现确定性延迟,子类2通过sync实现确定性延迟。子类1的结构最为复杂,也是JESD204B使用最广泛的模式。

子类1的框图如下所示,时钟芯片同时给发送端和接收端提供sysref和Device Clock,接收端和发送端通过sysref去产生与Device Clock同步的帧时钟和多帧时钟LMFC。在链路建立阶段接收端通过拉低SYNC信号,去同步多lane数据,具体细节在后文的JESD204B确定性延迟章节进