基于IMX429-IMX430-IMX432-IMX437等sensor的SLVS桥MIPI透传模组方案

作者:Hello,Panda

大家好,这篇博文是对之前一篇博文(视频)的补充。

一、概述

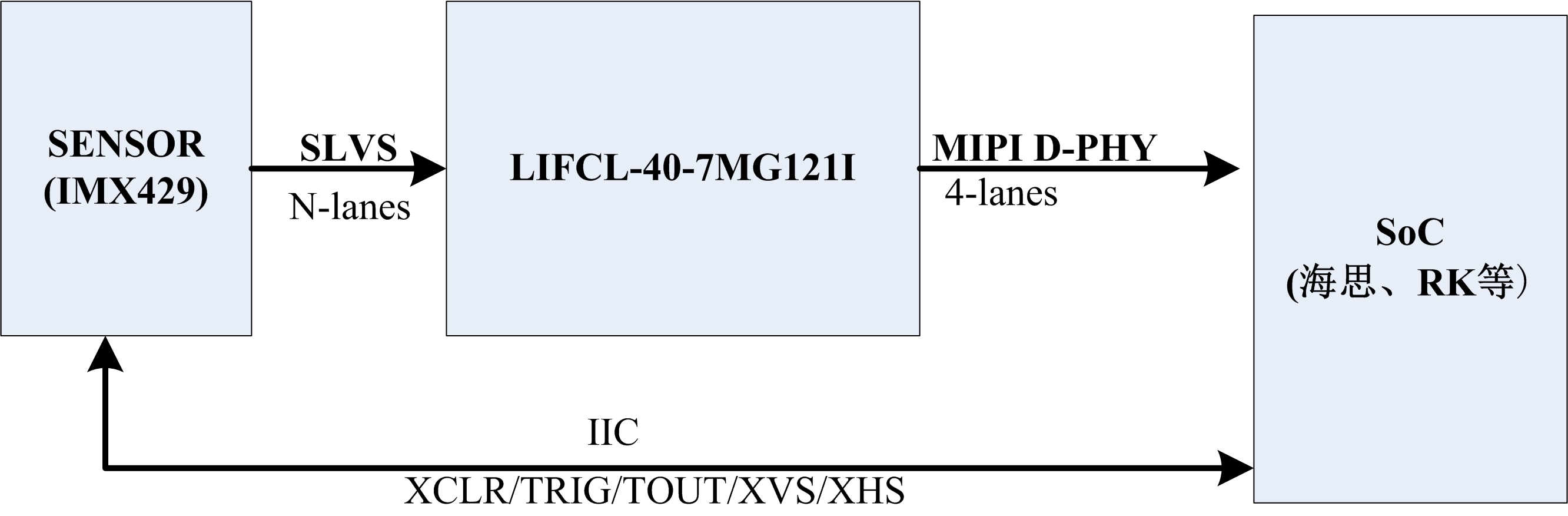

模组实现将CMOS图像传感器SLVS接口输出的图像透明传输桥接为MIPI格式,架构见下图1。

图1 透明传输桥接架构

图1 透明传输桥接架构

此类LVDS、SubLVDS、SLVS、HiSpi桥MIPI的应用场景主要是为适配不支持LVDS、SLVS、HiSpi等串行相机接口的SoC,可支持任意带宽允许范围内的串行接口到MIPI的数据透传转换,实现与SoC的普遍适配。支持当前所有的主流图像处理类SoC,如:海思Hislicon系列(Hi3559、Hi3519、Hi3403等)、RK系列(RK3588、RK3576、RV1126等)。

数据透传桥接的最大带宽由MIPI D-PHY的带宽决定,MIPI D-PHY接口最高带宽为2.5Gbps/Lane×8lanes = 20Gbps。任意通道的LVDS、SubLVDS、SLVS、HiSpi数据只要符合带宽要求,均可实现桥接。

桥接使用的FPGA需采用低功耗器件(发热越小越好,避免热量影响CMOS图像质量),从性能(速度、功耗、封装尺寸)上考虑,首选Lattice Crosslink-NX器件(LIFCL-17-MG121I或LIFCL-40-MG121I),其次为高云GW5A-25(MG121N封装)。区别是高云GW5A-25仅支持一组2.5Gbps 4-lanes MIPI硬核,带宽限制到了10Gbps,而Lattice Crosslink-NX支持2组2.5Gbps 4-lanes MIPI硬核,数据带宽可以支持到20Gbps。

可以根据实际需求来定制桥接的Sensor、输出AD位数、LVDS/SLVS/SubLVDS/HiSpi等接口数据通道数等。主控不支持Sony或安森美的SPI通信协议的,也可支持IIC转SPI通信功能。

二、硬件描述

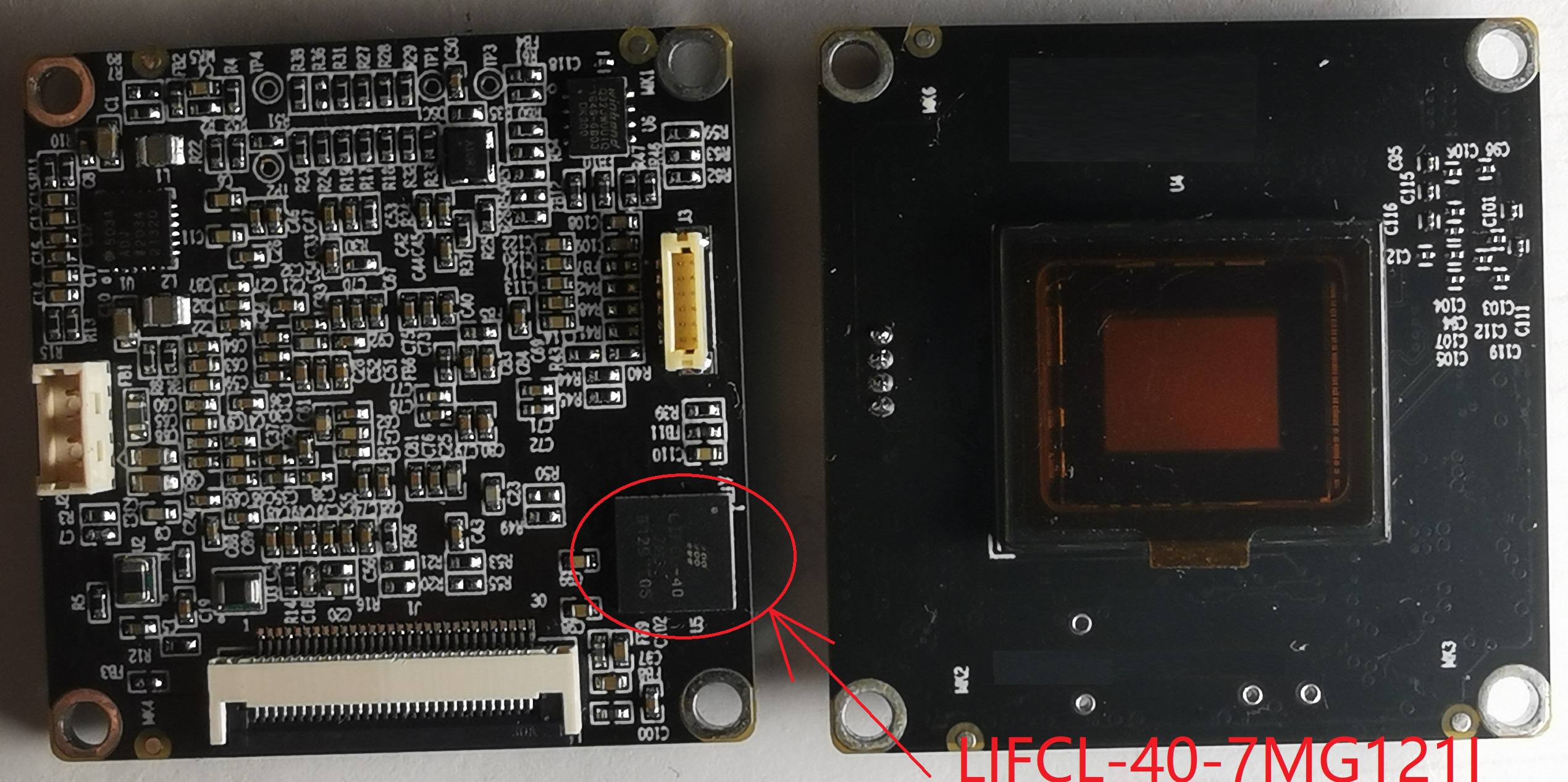

硬件尺寸为38mm×38mm,板层为6层,低功耗桥接FPGA和接插件安装在电路板的背面,硬件规格如下:

(1)模组电路尺寸:38mm×38mm;

(2)模组安装孔距:34mm×34mm,孔径φ=2.5mm,可安装任意34mm孔距CS口镜头座;

(3)搭配CMOS芯片:Sony IMX429 LLJ-C,2.83M(1936×1464)像素,4.5μm×4.5μm相元尺寸;

(4)桥接FPGA:Lattice Crosslink-NX LIFCL-40-7MG121I;

(5)对外接口:30Pin 0.5mm间距FPC;

(6)功耗:~1.5W,DC-5V±5%供电时;

(7)工作温度:-30~60°C。

下图2是硬件实物图,如图所示,桥接FPGA安装在CMOS芯片的背面,封装尺寸为6mm×60mm。

图2 IMX429桥接板实物图

图2 IMX429桥接板实物图

对外接插件采用30Pin 0.5mm间距FPC座,插件定义见下表1。

表1 FPC信号描述

| Pin号 | 信号名 | 信号描述 | 备注 |

| 1/3 | VCC | DC-5V直流输入,500mA | |

| 2 | NC | 悬空 | |

| 4 | GND | 电源地 | |

| 5 | TOUT1 | IMX429 TOUT1信号 | |

| 6 | CMOS_XCLR | IMX429 XCLR信号 | |

| 7 | CMOS_XVS | IMX429 XVS信号 | |

| 8 | CMOS_XHS | IMX429 XHS信号 | |

| 9 | TOUT0 | IMX429 TOUT0信号 | |

| 10 | GND | 电源地 | |

| 11 | IIC_SCL | IMX429 SCL信号 | |

| 12 | IIC_SDA | IMX429 SDA信号 | |

| 13 | GND | 电源地 | |

| 14 | CMOS_TRIG1 | IMX429 TRIG1信号 | |

| 15 | CMOS_TRIG2 | IMX429 TRIG2信号 | |

| 16 | GND | 电源地 | |

| 17 | MIPI_CKN | MIPI时钟N | |

| 18 | MIPI_CKP | MIPI时钟P | |

| 19 | GND | 电源地 | |

| 20 | MIPI_DN0 | MIPI LANE0数据N | |

| 21 | MIPI_DP0 | MIPI LANE0数据P | |

| 22 | GND | 电源地 | |

| 23 | MIPI_DN1 | MIPI LANE1数据N | |

| 24 | MIPI_DP1 | MIPI LANE1数据P | |

| 25 | GND | 电源地 | |

| 26 | MIPI_DN2 | MIPI LANE2数据N | |

| 27 | MIPI_DP2 | MIPI LANE2数据P | |

| 28 | GND | 电源地 | |

| 29 | MIPI_DN3 | MIPI LANE3数据N | |

| 30 | MIPI_DP3 | MIPI LANE3数据P |

三、软件描述

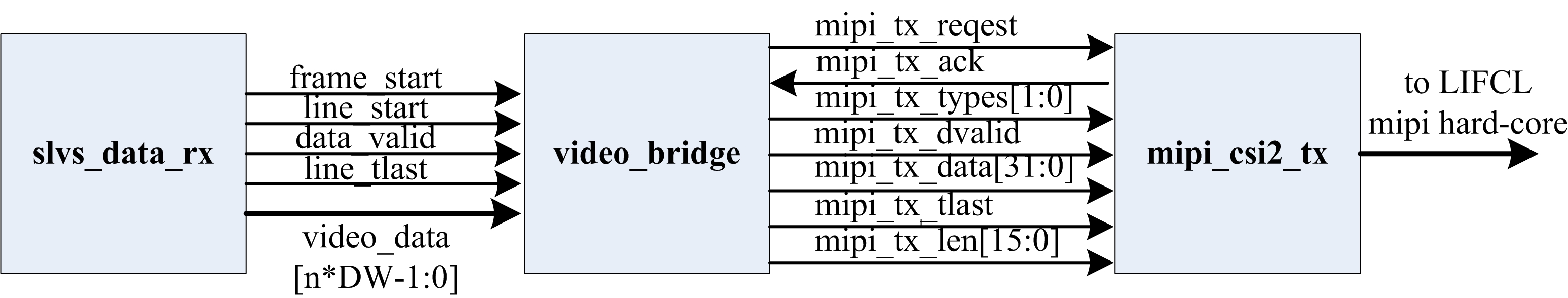

运行在LIFCL-40-7MG121I软件功能为SLVS透传桥接到MIPI,其实现逻辑为(见图3):

(1)FPGA的高速差分IO接收IMX429输出的4-lanes SLVS差分数据,去串行化并按照Sony的协议格式恢复为图像像素数据;

(2)接收到的IMX429图像经过桥接逻辑转发,重新按照MIPI CSI-2协议格式封装后经D-PHY发送给后端SoC使用。

图3 桥接逻辑架构

软件的规格参数如下:

(1)桥接模式:数据透传,控制信号和初始化寄存器配置由后端主控SoC完成,FPGA只桥接数据;

(2)输入输出:CMOS输出为4-Lanes 12bit SLVS数据信号,FPGA采集后经4-Lanes MIPI D-PHY接口输出,输出MIPI格式为CSI-2、RAW12、800Mbps/Lane Data Rate、Gated Clock Mode;

(3)软件采用Verilog源码开发,不使用Lattice官方或第三方付费IP;

(4)软件可直接适配IMX429、IMX430、IMX432、IMX437等Sony CMOS图像传感器。

四、运行效果

下图4是采集桥接后的MIPI数据并经HDMI显示的实际运行效果图(拍摄的是松香盒子)。

图4 拍摄松香盒子运行效果图

今天的分享到此结束,大家晚安。