基于FPGA的PID控制器verilog实现,包含simulink对比模型

目录

1.课题概述

2.系统测试效果

3.核心程序与模型

4.系统原理简介

5.完整工程文件

1.课题概述

根据PID控制器的原理,设计FPGA的总体架构。通常包括误差计算模块、比例运算模块、积分运算模块、微分运算模块、加法器模块以及控制信号输出模块等。同时通过simulink对比PID控制仿真输出。

2.系统测试效果

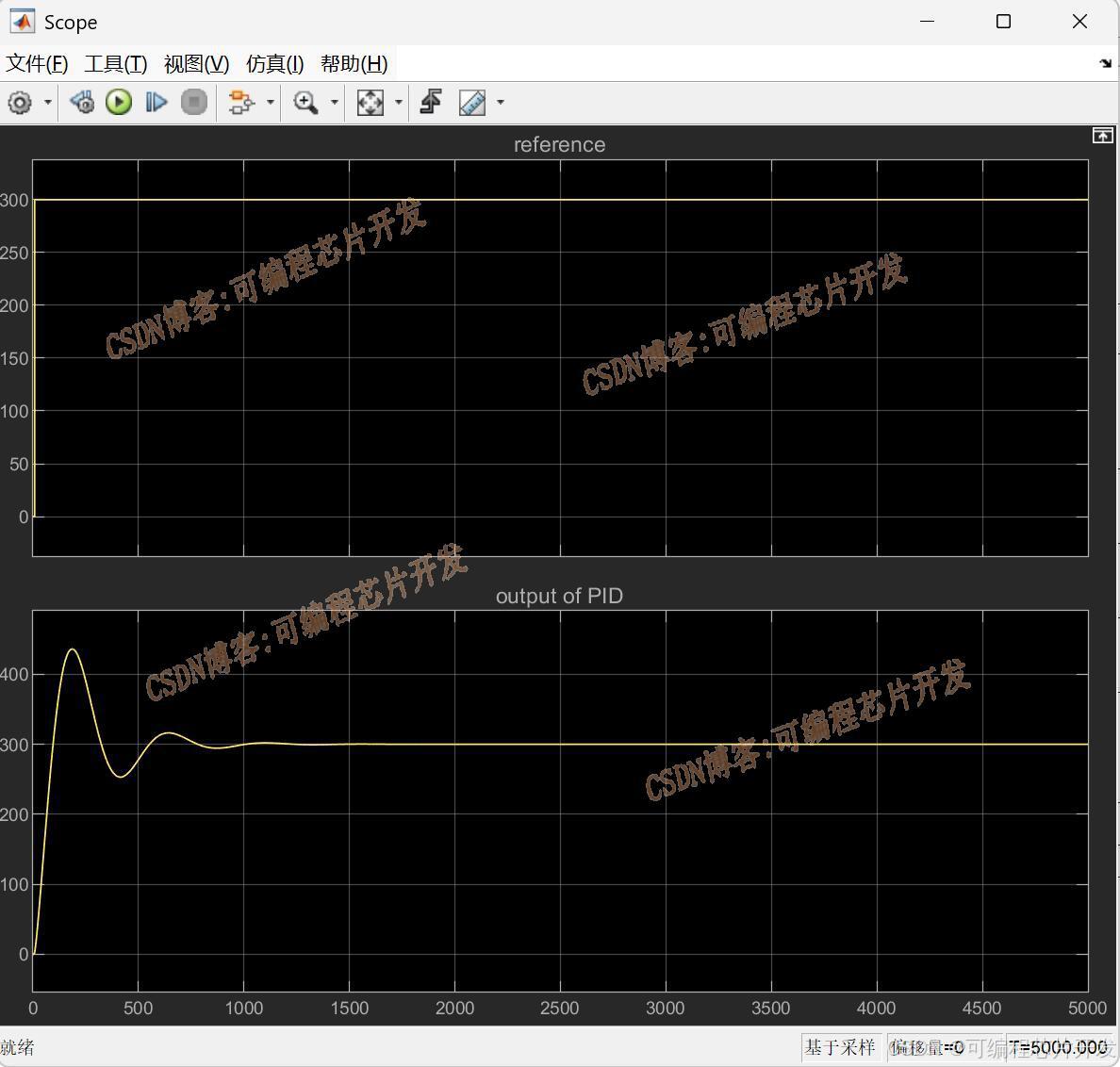

simulink仿真测试

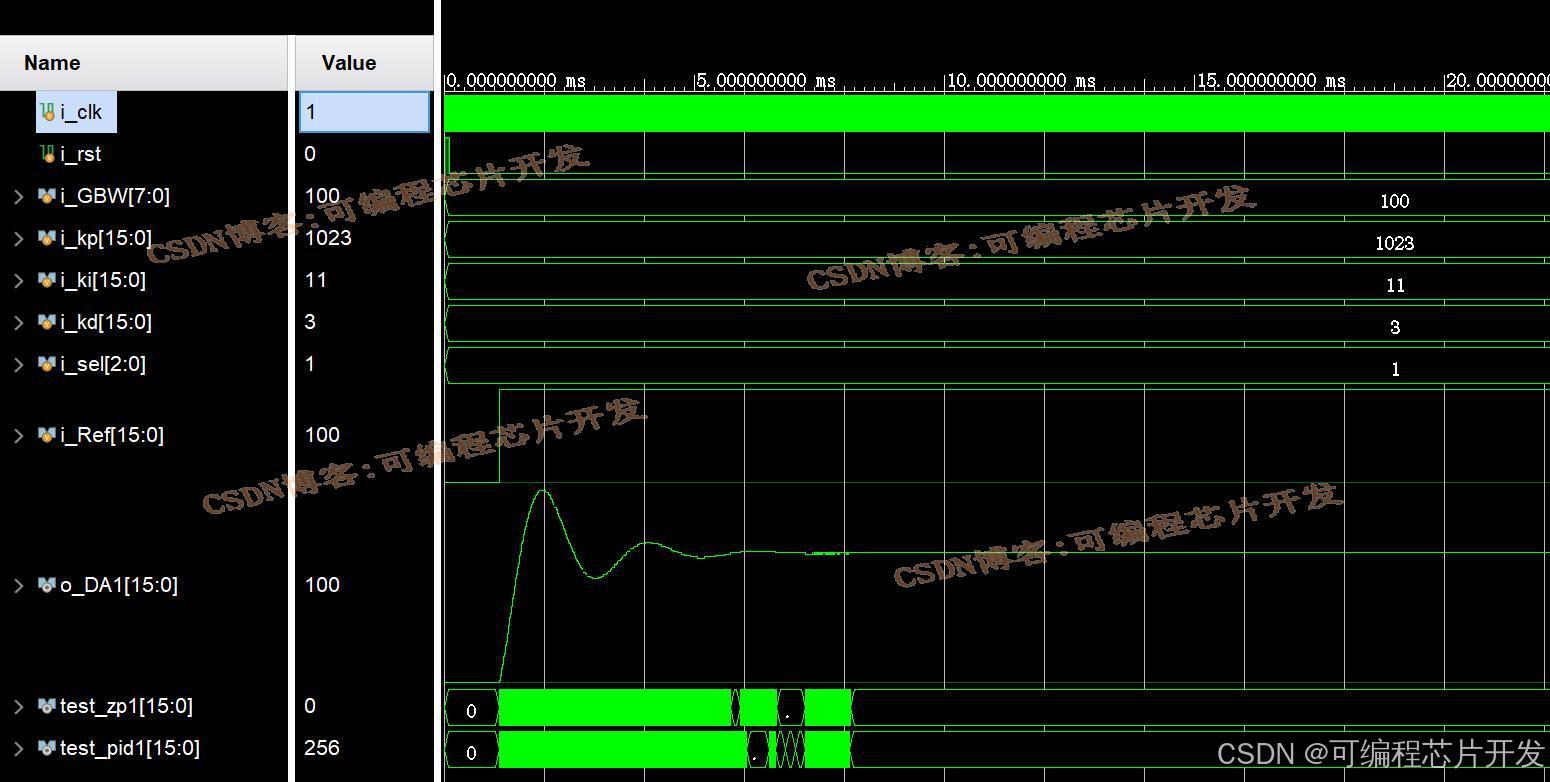

FPGA仿真测试

FPGA硬件测试

在实际测试过程中,如果你的开发板和我的不一样,可以参考本博客置顶文章进行硬件配置修改:

FPGA系统开发板调试过程不同芯片的移植步骤介绍_xilinx更换芯片怎么移植-CSDN博客

通过这个链接的步骤,可以实现不同开发板上的系统调试。

3.核心程序与模型

版本:vivado2022.2

`timescale 100ns / 100psmodule pid_zp_GBW(i_clk,i_rst,i_GBW,i_kp,i_ki,i_kd,i_sel,i_Ref,o_DA1,//testtest_zp1,test_pid1 );input i_clk;

input i_rst;

input [7:0]i_GBW;//1~200

input[15:0]i_kp;

input[15:0]i_ki;

input[15:0]i_kd;

input[2:0] i_sel;

input[15:0]i_Ref; output signed[15:0]o_DA1; //test

output signed[15:0]test_zp1; output signed[15:0]test_pid1; //STEP1

wire signed[15:0]err1; //if hardware

//assign err1 = i_Ref-i_AD1;

//assign err2 = i_Ref-i_AD2;

//assign err3 = i_Ref-i_AD3;

//assign err4 = i_Ref-i_AD4;

//if simulation

assign err1 = i_Ref-o_DA1;//zp

zp_filter zp_filter_u1(.i_clk (i_clk),.i_rst (i_rst),.i_sel (i_sel),.i_din (err1),.o_dout (test_zp1));//PID

//PID

PID_tops PID_tops_u(.i_clk (i_clk),.i_rst (i_rst),.i_kp (i_kp),.i_ki (i_ki),.i_kd (i_kd),.i_din (test_zp1),.o_dout (test_pid1),//test port.o_doutp (),.o_douti (),.o_doutd ());//GBW

GWB_tops GWB_tops_u(.i_clk (i_clk),.i_rst (i_rst),.i_GBW (i_GBW),.i_din1 (test_pid1),.o_dout1 (o_DA1));endmodule

00X6_003m4.系统原理简介

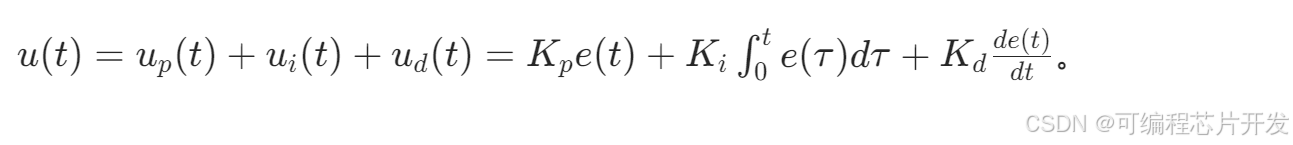

PID控制器由比例(Proportional)、积分(Integral)、微分(Derivative)三个环节组成,通过对误差信号进行比例、积分、微分运算,并将结果相加来控制被控对象,使其输出尽可能接近预期的目标值。

比例环节(P):比例环节的作用是根据当前误差的大小,成比例地输出控制量。其输出与误差信号成正比,比例系数Kp决定了控制作用的强度。比例环节能够快速响应误差的变化,使系统具有较快的调节速度。但单纯的比例控制会存在稳态误差,即系统最终稳定时,输出与目标值之间仍存在一定的偏差。

积分环节(I):积分环节用于消除系统的稳态误差。它对误差信号进行积分运算,随着时间的积累,积分项会逐渐增大,直到稳态误差为零。

微分环节(D):微分环节主要用于预测误差的变化趋势,提前给出控制作用,以减小系统的超调量和调节时间。它对误差信号的变化率进行运算,其输出与误差的变化速度成正比。

PID 控制器的总输出u(t) 是比例、积分、微分三个环节输出的叠加,即:

根据PID控制器的原理,设计FPGA内部的总体架构。通常包括误差计算模块、比例运算模块、积分运算模块、微分运算模块、加法器模块以及控制信号输出模块等。各个模块之间通过数据总线进行连接,实现数据的传输和处理。

5.完整工程文件

v