axi总线粗略学习

笔者因为项目需要用到AXI总线来控制数据跨时钟域的传输,通过这篇文章来当做学习的笔记

本文主要参考另一篇博主的文章文章链接 以及b站up主视频视频链接如需进一步的思考,可供参考

AXI(Advanced eXtensible Interface)高级可拓展接口

主要分为

AXI4:支持256长度burst传输

AXI-LIte:简单,不支持burst

AXI-Stream:不需要地址,可无限burst

主要通道

Read Address Channel

Write Address Channel

Read Data Channel

Read Data Channel

Write Response Channel

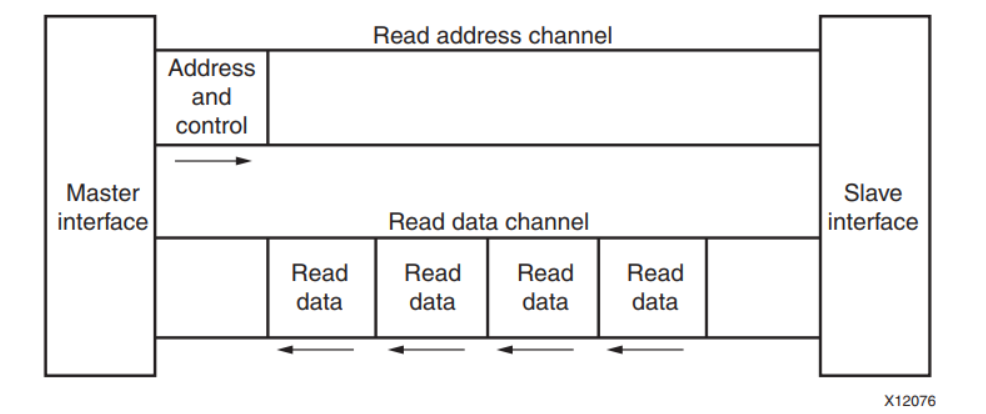

读事务

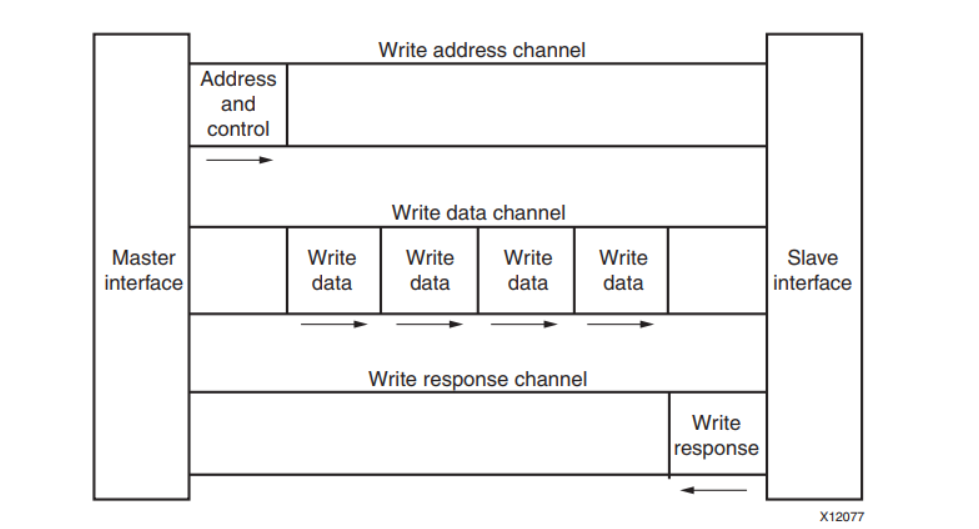

写事务

读写可以双向传输,允许每个Master 和 Slave的工作时钟不同,而且AXI可以通过打拍改善时序

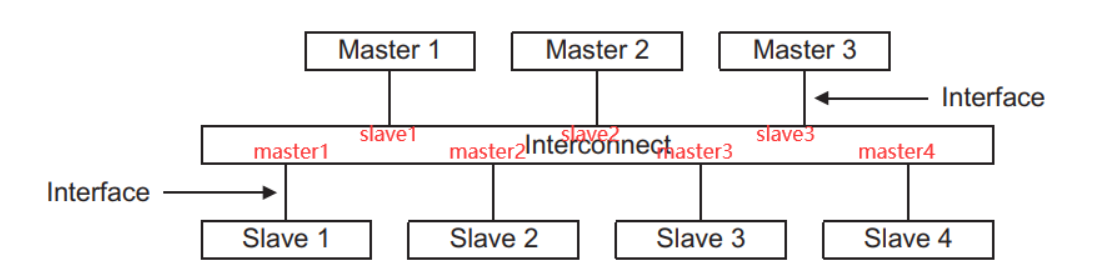

协议

协议支持多种master和slave互联,可以在任何通道插入寄存器,但要付出额外的延迟周期。

几种burst

突发读

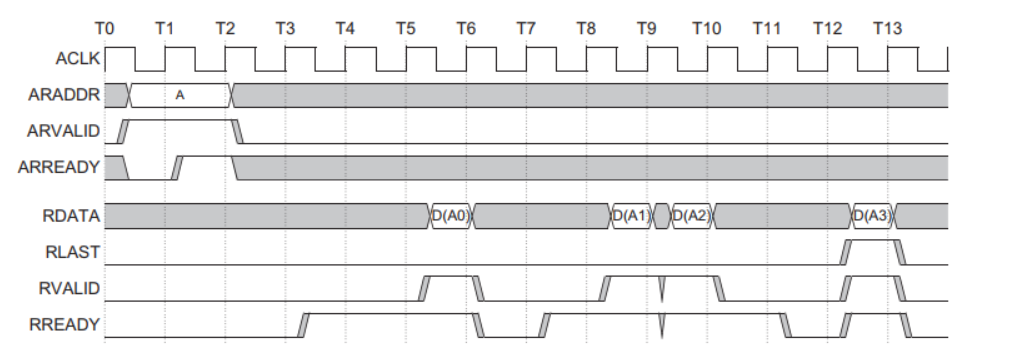

这是4长度的突发读示例

可以发现,当ARVALID和ARREADY同时为高时,ARADDR被传入从接口(其实这个没看出来,但手册是这么说的),当RVALID和RREADY同时为高时,RDATA被传入从接口,其中RLAST与最后一个有效数据同步。

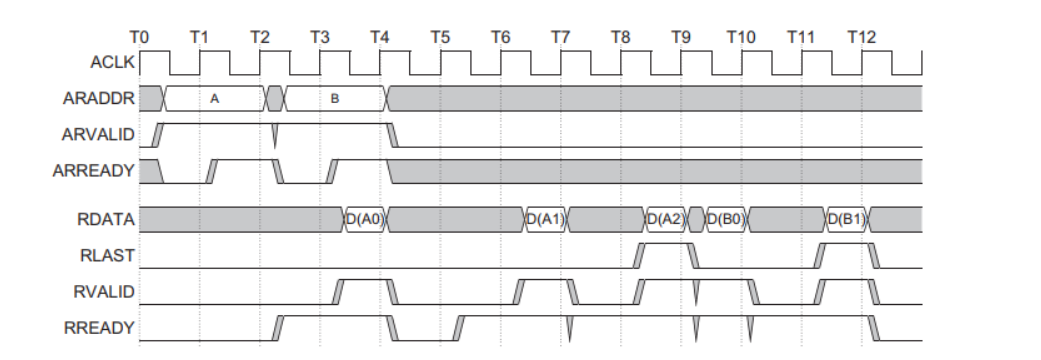

重叠突发读

按顺序传递,第一个突发读结束后,第二个突发读才开始

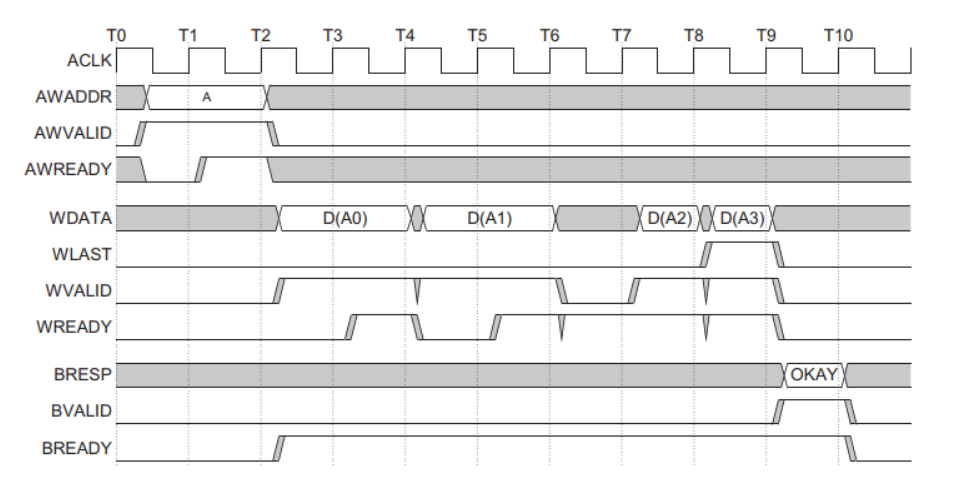

突发读

和突发读类似,不过在写结束后,从机会发送一个写响应,表明写事务完成

事务顺序

这个看起来有点复杂,但暂时先不管吧

信号

全局信号

| 信号 | 源 | 描述 |

|---|---|---|

| ACLK | 时钟源 | 全局时钟信号,所有信号在这个时钟的上升沿采样 |

| ARESETn | 复位源 | 全局复位信号,低电平有限 |

写地址信号

| 信号 | 源 | 描述 |

|---|---|---|

| AWID[x:0] | master | 写地址ID。这个信号是写地址组信号的标识标签。 |

| AWADDR[x:0] | master | 写地址。写地址总线给出写突发事务中第一次传输的地址。关联的控制信号用于确定突发中剩余传输的地址 |

| AWLEN[3:0] | master | 突发长度。突发长度给出了突发传输的确切数字。这个信息决定了与该地址相关联的数据传输的数量。突发长度=数据总长-1 |

| AWSIZE[2:0] | master | 突发尺寸。这个信号表示突发事件中每个传输的大小。另外配合字节通道选通信号(strobe,WSTRB)准确地指示要更新的字节通道。 |

| AWBURST[1:0] | master | 突发类型。突发类型,加上大小信息(AWSIZE),详细说明了如何在突发中计算每个传输的地址。 |

| AWLOCK[1:0] | master | 锁类型。这个信号提供有关转移的原子特性的附加信息。 |

| AWCACHE[3:0] | master | 缓存类型。这个信号指示事务的可缓冲(bufferable)、可缓存(cacheable)、透写(write-through)、回写(write-back)和分配(allocate)属性。 |

| AWPROT[2:0] | master | 保护类型。该信号指示传输事务的正常(normal)、私有(privileged)或安全保护(secure protection)级别,以及事务是数据访问(data access )还是指令访问(instruction access)。 |

| AWVALID | master | 写地址有效。该信号表示有效的写地址和控制信息可用 |

| AWREADY | slave | 写地址准备好。这个信号表明从机准备好接受一个地址和相关的控制信号 |

写数据信号

| 信号 | 源 | 描述 |

|---|---|---|

| WID[x:0] | master | 写ID标签。这个信号是写数据传输的ID标签。WID值必须与写事务的AWID值匹配。 |

| WDATA[x:0] | master | 写数据。写数据总线可以是8、16、32、64、128、256、512或1024位宽。 |

| WSTRB[3:0] | master | 写选通(strobe)。这个信号指示内存中要更新的字节位置。写数据总线的每8位都有一个写选通。因此,WSTRB[n]对应于WDATA[(8 × n) + 7:(8 × n)],即每一位选通自己对应的Byte |

| WLAST | master | 写last。这个信号表示写入突发中的最后一次传输。 |

| WVALID | master | 写有效。 |

| WREADY | slave | 写ready。 |

写响应信号

| 信号 | 源 | 描述 |

|---|---|---|

| BID[x:0] | Slave | 响应ID。写响应的标识标签。BID值必须匹配slave正在响应的写事务的AWID值。 |

| BRESP[1:0] | master | 写响应。这个信号指示写事务的状态。允许的响应有OKAY、EXOKAY、SLVERR和DECERR。 |

| BVALID | Slave | 写响应有效。 |

| BREADY | master | 响应ready。 |

读信号类似,省略

握手机制

握手过程

源产生VALID信号以指示何时数据或控制信息可用。VALID信号必须保持高电平,直到数据传输完成

目的地生成READY信号来表示它接受数据或控制信息。

只有当VALID和READY信号都是HIGH时,握手成功,数据在这一拍完成传输

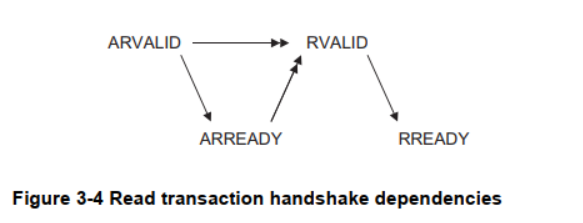

实际上都是先给VALID,对应的READY才会拉高,所以等READY再使能VALID是不对的工作时序。

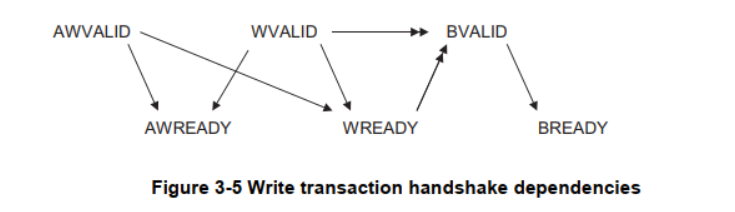

握手信号之间的关系

读事务

写事务