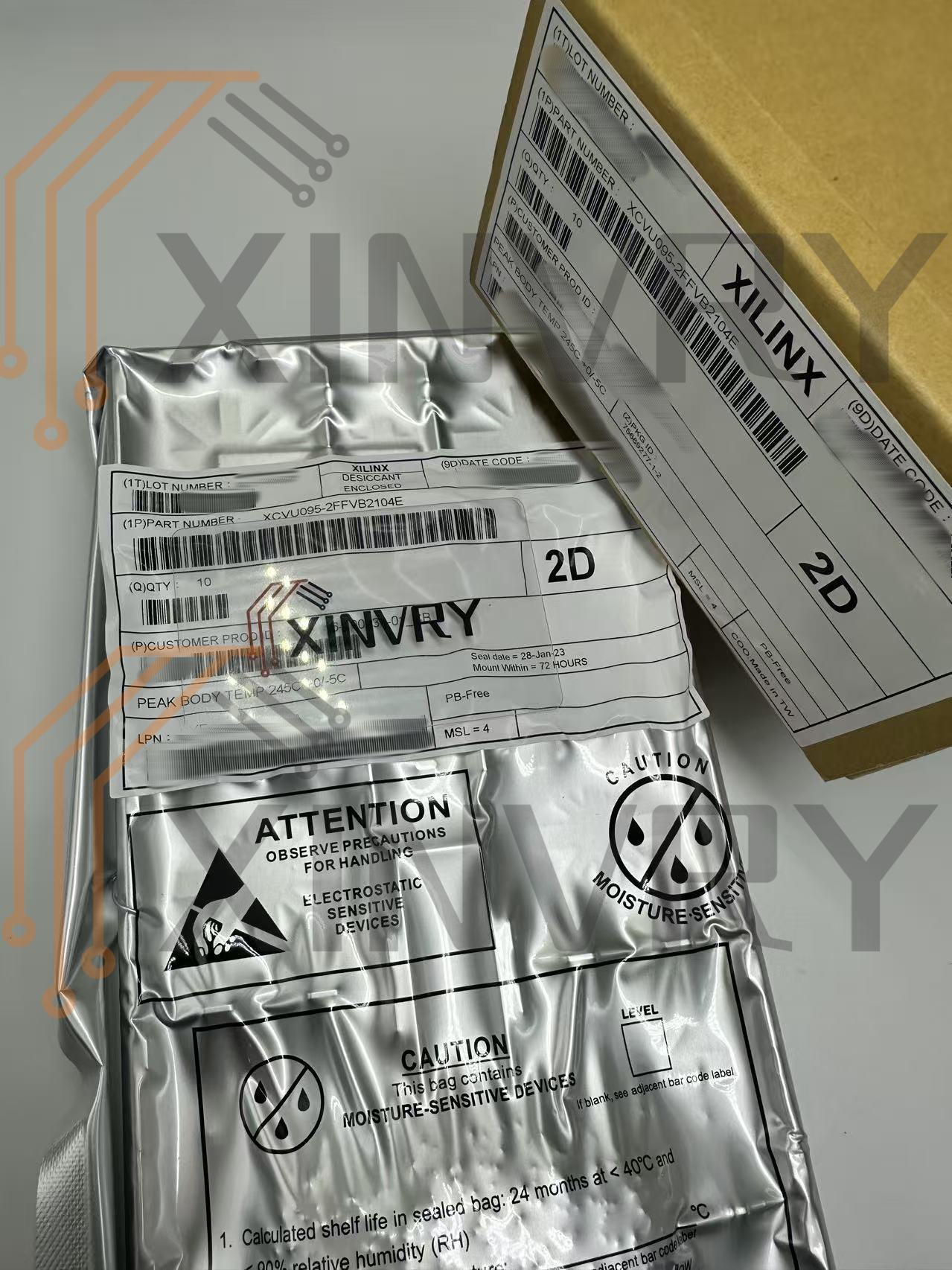

赛灵思 XCVU095-2FFVB2104E XilinxFPGA Virtex UltraScale

XCVU095-2FFVB2104I 是 Xilinx(现 AMD)Virtex UltraScale 系列中的高端 FPGA 器件,基于 20nm 工艺,提供卓越的逻辑密度和高速串行 I/O 能力,广泛应用于 400G 网络、ASIC 原型验证及大型数据中心互联

该器件集成 1 176 000 个逻辑单元,62 259 200 位片上 RAM,702 条通用 I/O,引脚封装为 2104‑球 FCBGA,典型核心电压 0.95 V(0.922 V–0.979 V),工作温度 0 ℃ 至 100 ℃

Virtex UltraScale FPGA 采用 20 nm 低功耗铜互连工艺,内置全局时钟网络和高级配置管理模块,兼顾高性能与低功耗。SRAM 型架构赋予器件灵活的动态重配置能力,但每次上电或复位后需重新加载位流

逻辑与存储资源

逻辑单元:1 176 000 个,可组成数万 LAB/CLB,用于实现高密度组合与时序逻辑。

块 RAM:62 259 200 位(约 7.8 MB),分布于多个 18 Kb M18K RAM 块。

分布式 RAM:LUT 可配置为小容量 RAM 或移位寄存器,满足低延迟存储需求