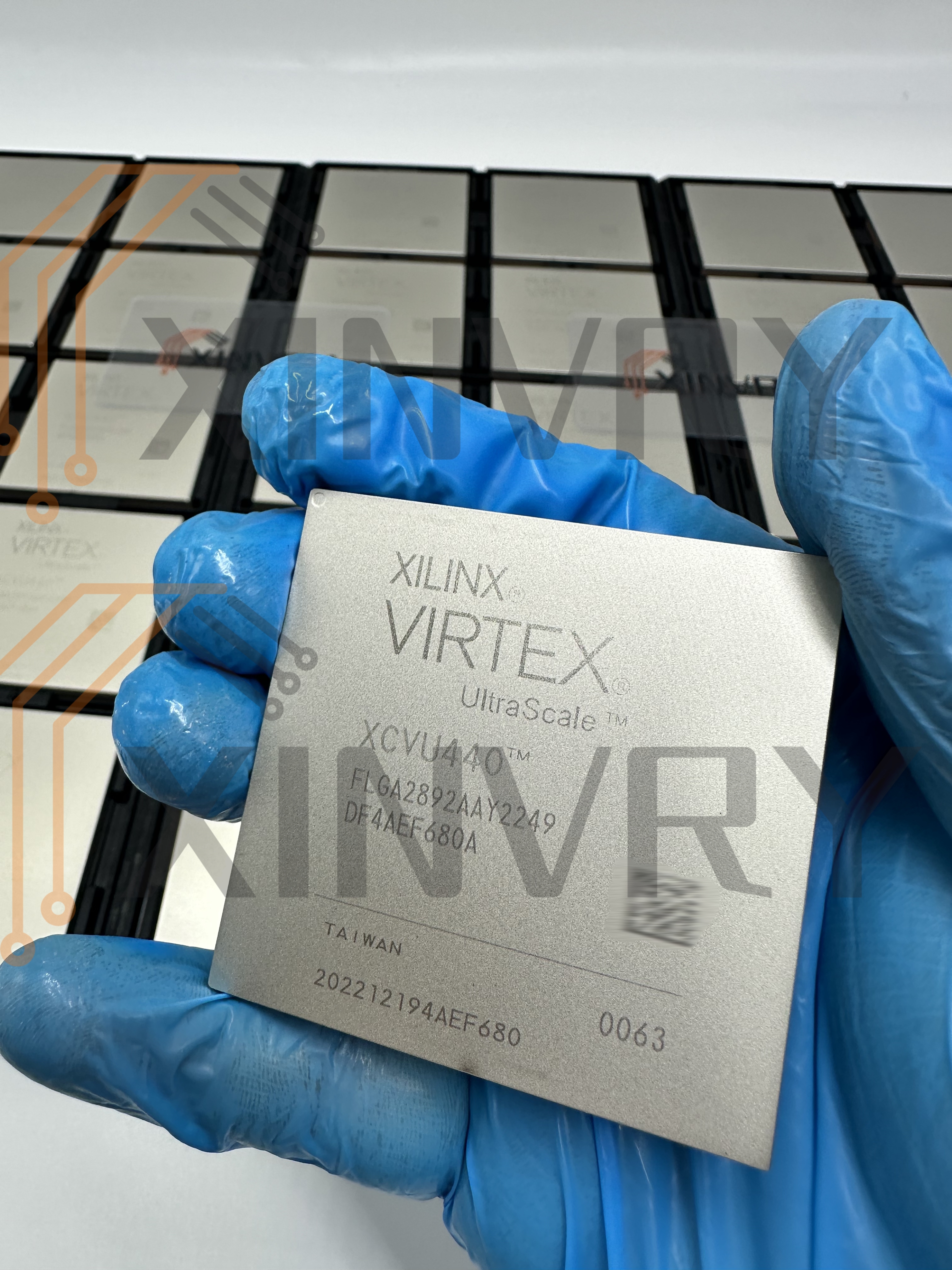

赛灵思 XCVU440-2FLGA2892E XilinxFPGA Virtex UltraScale

XCVU440-2FLGA2892E 属于 Xilinx Virtex UltraScale 系列,是面向高端应用的旗舰 FPGA 器件。该系列产品以出色的高并行处理能力、丰富的逻辑资源和高速互联能力闻名,广泛用于 高性能计算、数字信号处理等对计算能力和带宽要求极高的场景。采用先进的 20nm 工艺技术,其低功耗和高性能的特点使之成为系统设计者在定制硬件加速、实时数据处理等领域的重要选择。

1. 逻辑资源与内部存储

逻辑元件/单元数

XCVU440-2FLGA2892E 集成了约 5,540,850 个逻辑单元,这为设计大规模复杂数字系统提供了足够的资源,能够支持数百万级的逻辑运算和定制化接口设计。

逻辑数组块 (LAB/CLB)

该芯片拥有约 316,620 个逻辑数组块。每个 LAB 内部通常包括查找表(LUT)、寄存器和互连资源,设计者可基于这些资源灵活构建高效逻辑电路,实现大规模并行处理。

内部存储

总 RAM 位数达到 90,726,400 位,内部集成了多级存储资源:

分布式 RAM:适合存储局部数据或实现小型 FIFO。

块级 RAM(BRAM):用于大容量数据缓存,满足高速数据采集与处理需求。

(部分 UltraScale 器件还支持 UltraRAM 模块,用于更大带宽和存储密度设计。)

2. 高速 I/O 与互连架构

I/O 引脚数量

提供多达 1456 个高速 I/O 接口,极大地提升了芯片与外部系统的数据吞吐能力和并行通信能力。这一数量级的 I/O 资源能够满足包括多通道数据采集、并行处理、高速串行通讯协议(如 PCI Express、以太网等)的复杂应用场景。

互连与时钟管理

内部采用了高带宽、低延迟的互连架构,支持跨 LAB 之间的高速数据交换。芯片内嵌多组时钟管理资源,如 MMCM(Mixed-Mode Clock Manager)和 PLL(Phase-Locked Loop),这些模块可以对系统时钟进行动态调节,实现多频率时钟同步,保证高速逻辑操作的精确时序控制。

3. 电气与工艺参数

供电电压

核心电源电压设置在 0.922V 到 0.979V 之间,这种低电压供电不仅有助于降低功耗,同时对噪声和发热控制都有很大优势。

工作温度范围

支持从 0°C 至 100°C(TJ)的工作温度,符合工业级应用的要求,可以在严苛环境下长时间稳定运行。

先进工艺技术 采用 20nm 制程工艺,芯片的晶体管密度和互联技术达到国际领先水平。这种工艺不仅提高了电路速度,还能有效降低功耗和提高器件集成度。

三、内部架构与模块化设计

1. 逻辑块及数字信号处理(DSP)模块

逻辑块结构 Virtex UltraScale FPGA 内部采用模块化设计,逻辑块(LAB/CLB)构成了基本运算单元。每个逻辑块内嵌了查找表、寄存器和基本互联网络,支持灵活的逻辑功能定制。设计者可以根据需求通过 HDL(硬件描述语言)精细规划每个逻辑单元的功能。

数字信号处理模块

芯片内集成了专用的 DSP 切片,适用于高精度乘法器、加法器以及 MAC 运算。这些切片在实现复杂信号处理、图像处理或通信编码时,能够显著提高运算速度和效率。

2. 内嵌存储与数据传输

多级内存架构

不同层次的内存(分布式 RAM、BRAM 及 UltraRAM)互相配合,为设计者提供了灵活的数据存储与处理解决方案。对于需要缓存大数据流的应用,如视频处理或高速通信,芯片能够同时提供低延迟的数据访问和高带宽支持。

数据传输架构 内部采用分级互联网络,实现逻辑块之间的快速数据传送。同时,高速 I/O 接口支持多种外部数据协议,确保芯片能够在复杂系统中实现低延迟、高并发数据交换。

3. 可重构性与动态部分重配置

动态部分重配置

作为 FPGA 的一大优势,Virtex UltraScale 系列支持在系统运行时对部分逻辑资源进行动态重配置。这意味着在不干扰系统整体运行的情况下,可以根据实时需求更改某一局部电路功能,极大提升系统的灵活性和资源利用率。

模块化设计思路

设计者可以将 FPGA 内部划分为多个独立模块,每个模块独立完成特定功能。在实现大系统时,各模块之间可以通过高速互连进行协同工作,这种高度模块化的设计为复杂系统集成提供了便利。