FPGA--HDLBits网站练习

目录

用状态机编写一个 LED流水灯代码

CPLD和FPGA芯片

CPLD(复杂可编程逻辑器件)

FPGA(现场可编程门阵列)

Verilog练习

基本

向量

用状态机编写一个 LED流水灯代码

往期作业已完成,博客地址:

FPGA-流水灯-CSDN博客

CPLD和FPGA芯片

FPGA和CPLD都是可编程ASIC器件,在一定的程度上具有很大的相似性,但也有很多不同之处,因为各自的结构不同,让它们都各有特点。FPGA是现场可编程逻辑门阵列的简称。CPLD是复杂可编程逻辑器件的简称。下面将介绍这两者的区别:

CPLD(复杂可编程逻辑器件)

定义:CPLD是一种基于与或阵列结构的可编程逻辑器件,具有固定的逻辑块和互连矩阵。

特点:

- 逻辑块之间的连接是集总式的,适合实现简单的逻辑功能。

- 采用EEPROM或Flash技术,断电后能保持编程信息。

- 延时均匀且可预测,适合对时序要求严格的应用。

- 功耗相对较大,尤其是集成度较高的情况下。

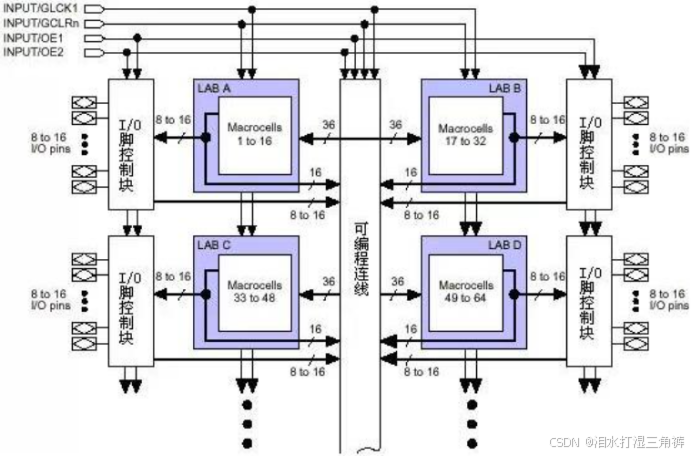

CPLD主要由以下三部分组成:

1、宏单元(Macrocell)

宏单元是PLD的核心部分,负责实现基本的逻辑功能。它就像一个“逻辑工厂”,可以完成各种逻辑运算(比如与、或、非等)。图中蓝色部分代表多个宏单元的集合,因为宏单元数量较多,所以没有逐一画出。

2、可编程连线(PIA)

可编程连线是PLD内部的“道路”,负责信号的传递。它将所有的宏单元连接起来,确保信号可以在不同的逻辑单元之间流动。通过编程,可以灵活地定义这些连线的路径,实现信号的高效传输。

3、I/O控制块

I/O控制块是PLD与外部电路之间的“开关”,负责管理输入和输出的电气特性。它可以根据需要调整输出方式,比如设置为集电极开路输出、控制信号的摆率(信号变化的速度)或实现三态输出(高电平、低电平和高阻态)。

其总体结构如下图所示(以MAX7000为例):

FPGA(现场可编程门阵列)

定义:FPGA是一种基于查找表(LUT)结构的可编程逻辑器件,具有可编程逻辑块、可编程I/O块和可编程互连。

特点:

- 互连是分布式的,适合实现复杂的逻辑功能。

- 基于SRAM技术,断电后编程信息丢失,需重新配置。

- 延时与布局布线有关,具有一定的不可预测性。

- 功耗相对较低,适合对功耗敏感的应用。

FPGA主要由以下7部分组成:

1、可编程输入/输出单元(IOB)

IOB是FPGA与外部电路之间的桥梁,负责信号的输入和输出。它可以根据需要配置信号的驱动方式,确保芯片与外部设备的通信顺畅。

2、可配置逻辑块(CLB)

CLB是FPGA的核心逻辑单元,每个CLB包含一个可编程的开关矩阵,通常有4到6个输入端口。通过灵活配置这些矩阵,可以实现各种逻辑功能,比如组合逻辑、移位寄存器、RAM等。

3、数字时钟管理模块(DCM)

DCM负责管理时钟信号,通过数字技术和相位锁定环(PLL)来优化时钟信号的稳定性,减少时钟抖动,确保系统运行的精确性。

4、嵌入式块RAM(BRAM)

BRAM是FPGA内部的存储模块,可以灵活配置为单口RAM、双口RAM、内容寻址存储器(CAM)或FIFO等结构。这种灵活性让FPGA在需要存储功能的场景中表现得更加出色。

5、布线资源

FPGA内部有丰富的布线资源,分为四类:

全局布线:用于全局时钟和复位信号的连接。

长线布线:用于芯片不同区域之间的高速信号传输。

短线布线:用于逻辑单元之间的局部连接。

分布式布线:用于专有时钟和控制信号的连接。

6、底层内嵌功能单元

这些功能单元包括延迟锁定环(DLL)、相位锁定环(PLL)、数字信号处理模块(DSP)和软核处理器(CPU)。它们为FPGA提供了额外的功能支持,比如信号延迟控制、时钟信号稳定和数据处理能力。

7、内嵌专用硬核

为了提升性能,FPGA内部集成了专用的硬核模块,比如乘法器和高速串行收发器(SerDes)。这些硬核模块通过IP核调用实现,虽然通用性不如底层功能单元,但能显著提高特定功能的效率。

其原理与结构如下图所示:

相对比得,CPLD基于与或阵列结构,逻辑块连接固定,适合简单逻辑功能,采用EEPROM或Flash技术,断电可保持编程信息,延时均匀可预测,适用于对时序要求严格的小型嵌入式系统、接口电路和工业控制等,功耗较大但成本低,适合成本敏感应用。FPGA基于查找表(LUT)结构,逻辑块和互连可编程,适合复杂逻辑功能,基于SRAM技术,断电后需重新配置,延时与布局布线有关,灵活性高,适用于复杂数字系统、原型验证和需频繁更新的通信设备、图像处理、人工智能等场合,功耗相对低,适合功耗敏感应用。

综上所述,CPLD适合简单、成本敏感应用,FPGA适合复杂、灵活配置需求场合。

Verilog练习

对于我们日常学习、练习FPGA,HDLBits网站是一个很友好得到网站,它是一个国外的开源FPGA学习网站,提供了一个网页版的Verilog代码编辑仿真验证平台。

用户可以在该网站上进行Verilog代码的编写、综合,并且能够仿真出波形来验证设计代码的正确性。该平台基于Icarus Verilog(开源HDL仿真工具),用户只需登录网页就能享受Verilog编程仿真的乐趣。

HDLBits的题目由浅入深,设计合理,可以帮助初学者掌握Verilog这门语言。下面我将由浅入深讲解几个例题,如有不对的地方,请大家帮忙指出。

基本

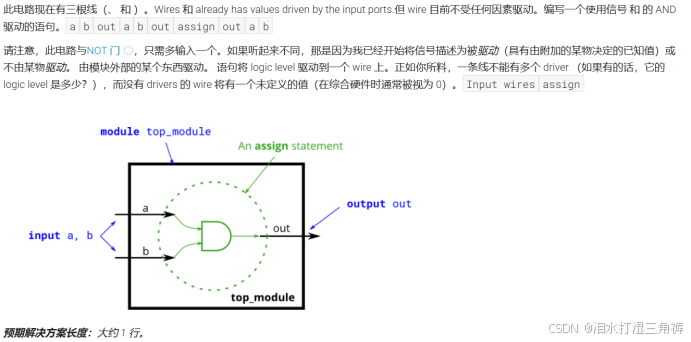

AND门

module top_module(

input a,

input b,

output out

);

assign out = a && b;

endmodule

注:红字为编写的解决方案

- assign out = a && b;

这是一个连续赋值语句,表示 out 的值始终等于 a 和 b 的逻辑与结果。

&& 是逻辑与操作符,只有当 a 和 b 都为1时,out 才为1;否则 out 为0。

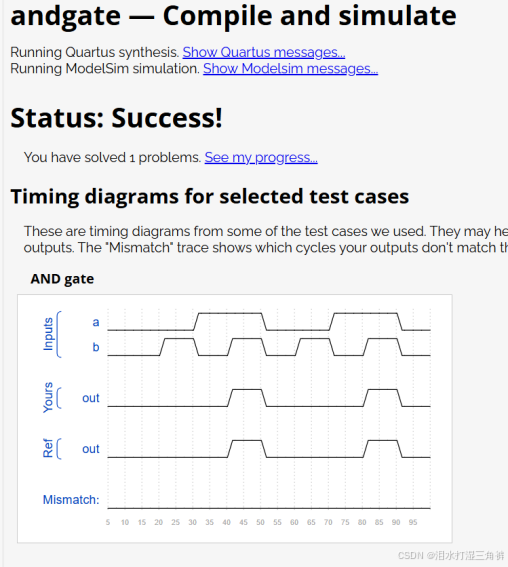

方案结果:

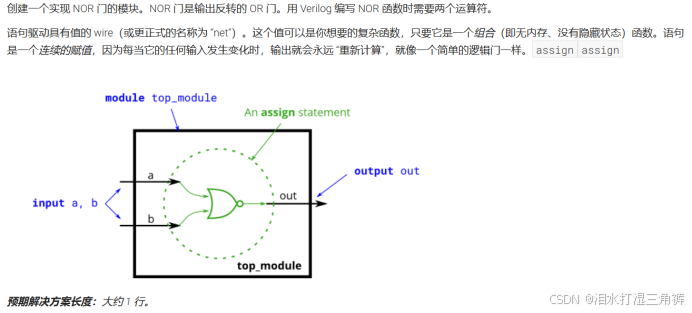

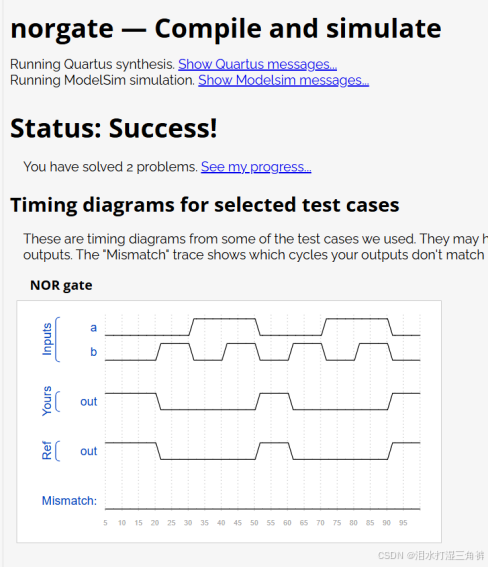

NOR门

module top_module(

input a,

input b,

output out

);

assign out = ~(a || b);

endmodule

- assign out = ~(a || b);

这是一个连续赋值语句,表示 out 的值始终等于 a 和 b 的逻辑或(OR)结果的反(NOT)。

|| 是逻辑或操作符,当 a 或 b 中有一个为1时,结果为1;否则为0。

~ 是逻辑非操作符,对逻辑或的结果取反。

方案结果:

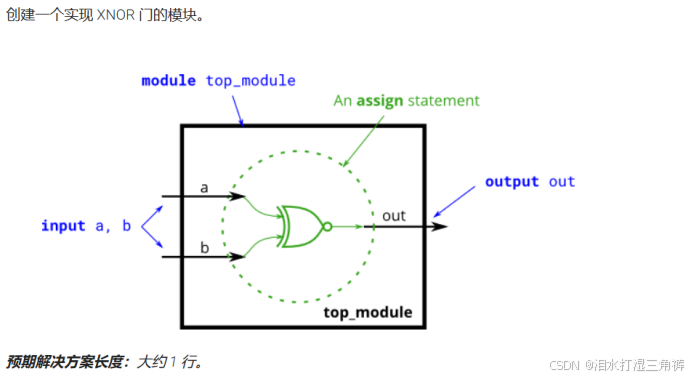

XNOR门

module top_module(

input a,

input b,

output out

);

assign out = a == b;

endmodule

- assign out = a == b;

这是一个 连续赋值语句,表示 out 的值始终等于 a 和 b 是否相等的结果。

== 是比较运算符,用于判断 a 和 b 的值是否相等。如果相等,结果为1;否则为0。

方案结果:

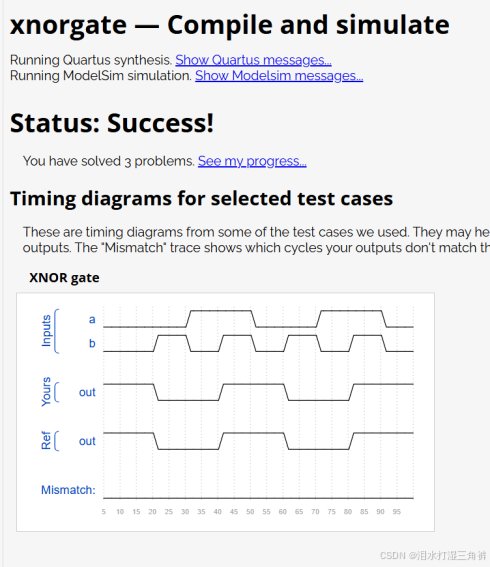

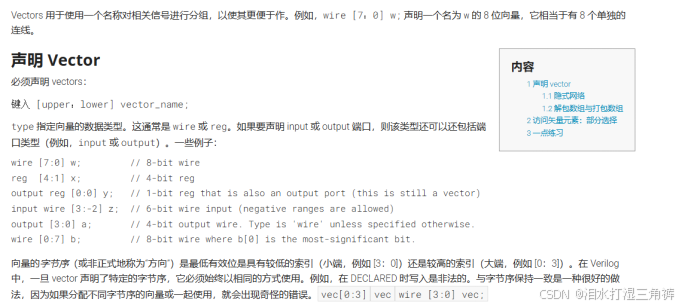

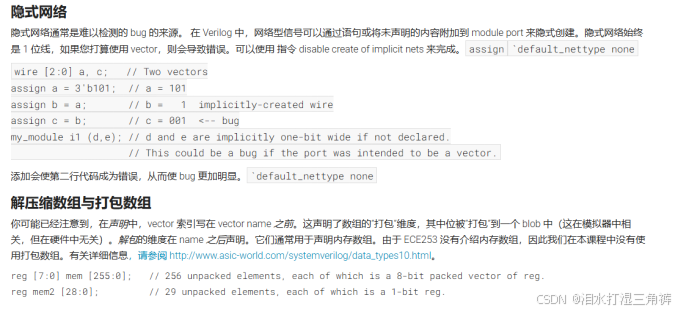

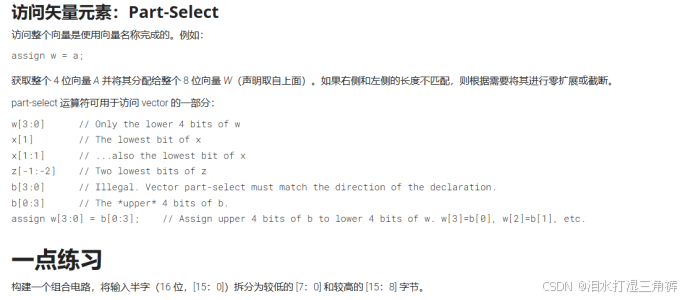

向量

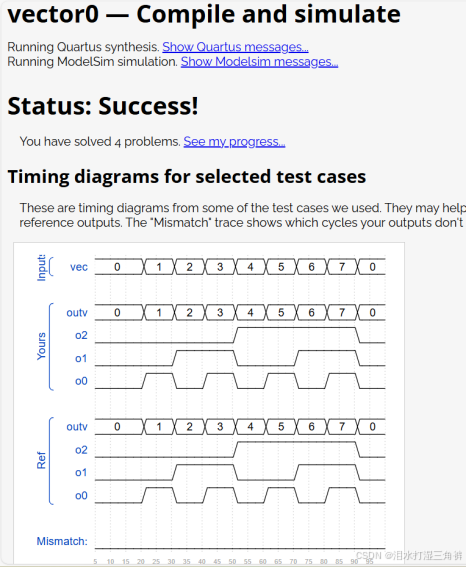

矢量0:

module top_module(

input [2:0] vec,

output [2:0] outv,

output o2,

output o1,

output o0

);

assign outv = vec;

assign o0 = vec[0];

assign o1 = vec[1];

assign o2 = vec[2];

endmodule

方案结果:

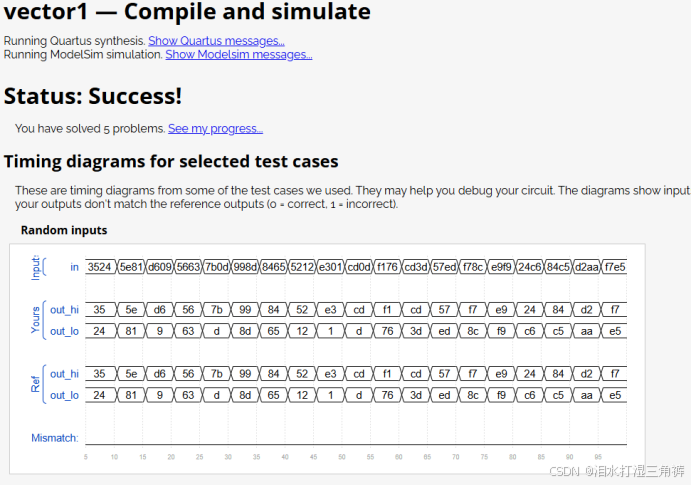

矢量1:

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo

);

assign out_lo = in[7:0]; // 低8位

assign out_hi = in[15:8]; // 高8位

endmodule

方案结果:

以上是本人对于题目的分析理解,学习还不够深入,暂时先列举能理解的一些题目,其他题目在以后的学习中,还会继续深入了解透彻。