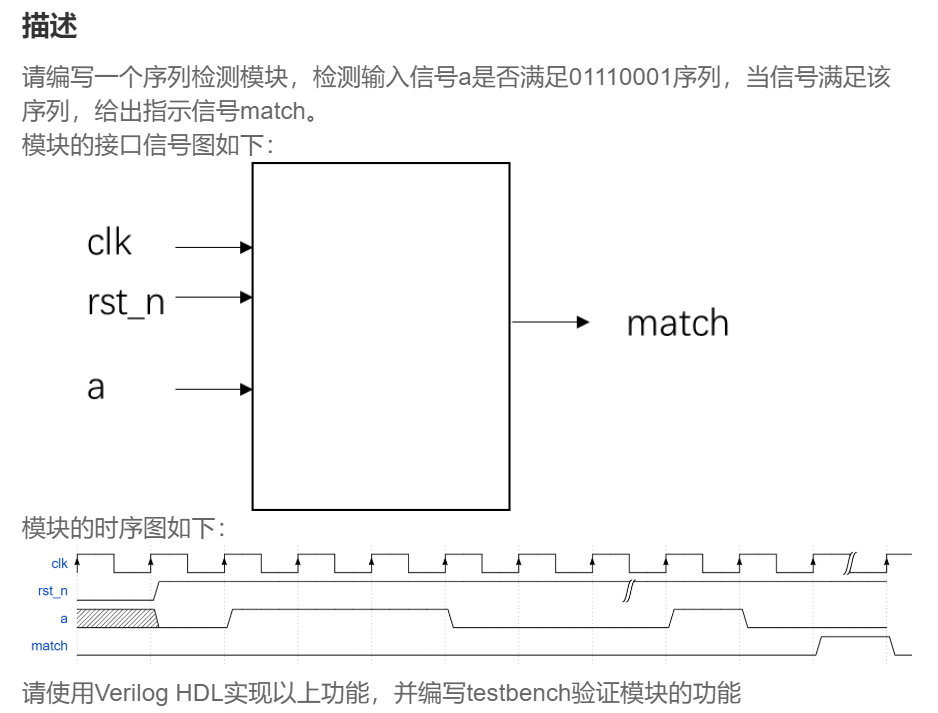

VL25 输入序列连续的序列检测

输入序列连续的序列检测_牛客题霸_牛客网

方法一:序列缓存比对

方法二:有限状态机写法(序列检测器)

`timescale 1ns/1nsmodule sequence_detect(input clk,input rst_n,input a,output reg match // ← 保持为 reg,在 always 中赋值

);parameter IDLE = 3'd0;parameter s0 = 3'd1;parameter s1 = 3'd2;parameter s2 = 3'd3;parameter s3 = 3'd4;parameter s4 = 3'd5;parameter s5 = 3'd6;parameter s6 = 3'd7;reg [2:0] state;reg [2:0] next_state;// 状态寄存器always @(posedge clk or negedge rst_n) beginif (!rst_n) beginstate <= IDLE;end else beginstate <= next_state;endend// 下一状态逻辑always @(*)begincase (state)IDLE : next_state = ~a ? s0 : IDLE ;s0 : next_state = a ? s1 : s0 ;s1 : next_state = a ? s2 : s0 ;s2 : next_state = a ? s3 : s0 ;s3 : next_state = ~a ? s4 : IDLE ;s4 : next_state = ~a ? s5 : s1 ;s5 : next_state = ~a ? s6 : s1 ;s6 : next_state = a ? IDLE : s0 ;default : next_state = IDLE ;endcase end// 直接在时序块中赋值 matchalways @(posedge clk or negedge rst_n) beginif (!rst_n) beginmatch <= 1'b0;end else if (state == s6 && a) beginmatch <= 1'b1;end else beginmatch <= 1'b0;endendendmodule