PCB之电源完整性之电源网络的PDN仿真CST---06

最近天气逐渐转凉了,各位道友们是时候展示出你的秋衣秋裤了,要美丽就要挨冻了。这年头什么行业都感觉不是太景气啊,小编我也不知道这个经济低落的大环境啥时候可以结束啊。

但是与其抱怨环境差不如去提升自己适应这个环境吧,毕竟孔子曾SAY:优胜劣汰,适者生存嘛。

好了,这期的扯犊子环节到此为止了,咱们言归正传了。本期的案例是小编我在成都出差的时候,帮忙一个分部的EE同事孙二波做电源仿真遇到的一个不错的案例。

一,我找了二波要了主芯片手册上的需要仿真的电源网络的设计要求如下所示:

VDD_DDR0N1:

0-100KHZ,阻抗要求是4.5mohm;

0.1MHz--7MHz,阻抗要求是15mohm;

7MHz--20MHz,阻抗要求是20mohm;

50MHz,阻抗要求是46mohm;

VDD_DDR2:

0-100KHZ,阻抗要求是9mohm;

0.1MHz--7MHz,阻抗要求是22mohm;

7MHz--20MHz,阻抗要求是42mohm;

50MHz,阻抗要求是75mohm;

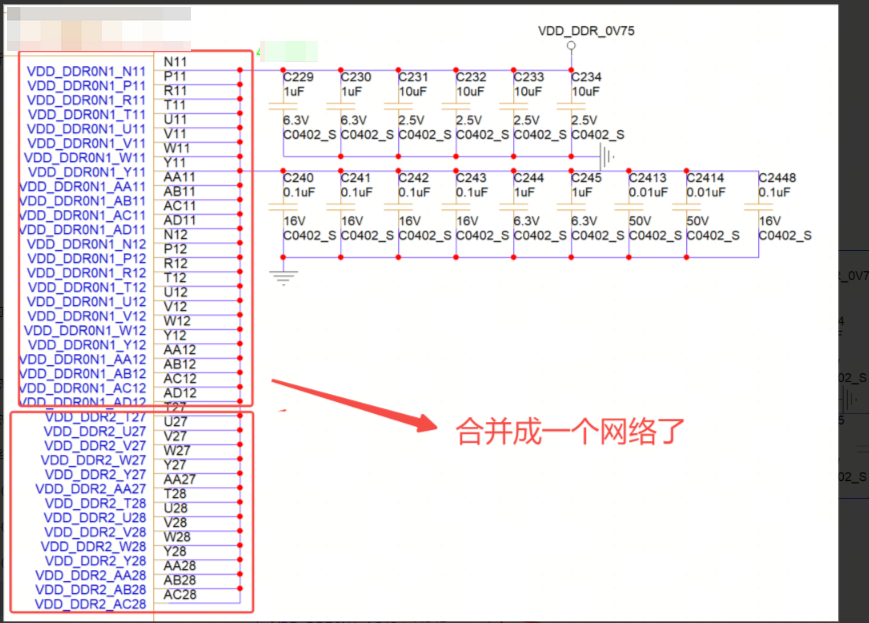

一看是两个不同的电源网络,但是孙二波在原理图上的设计是把这两个网络合并到一起了:

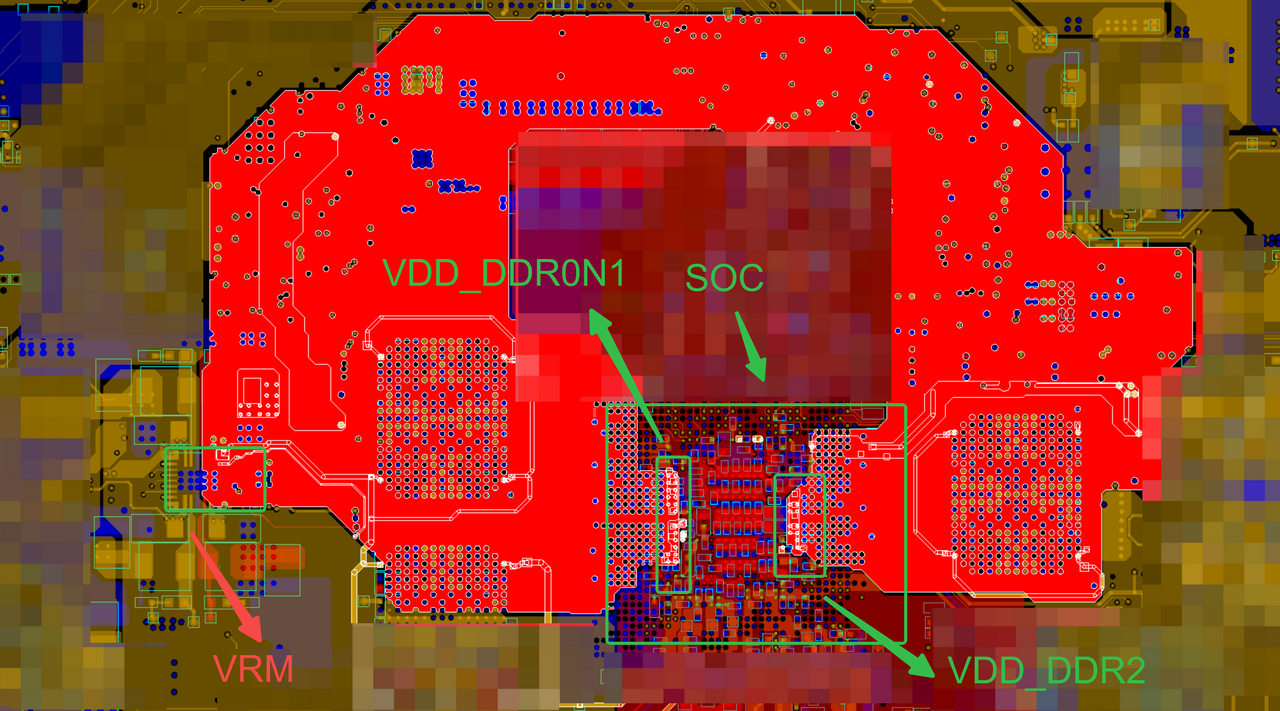

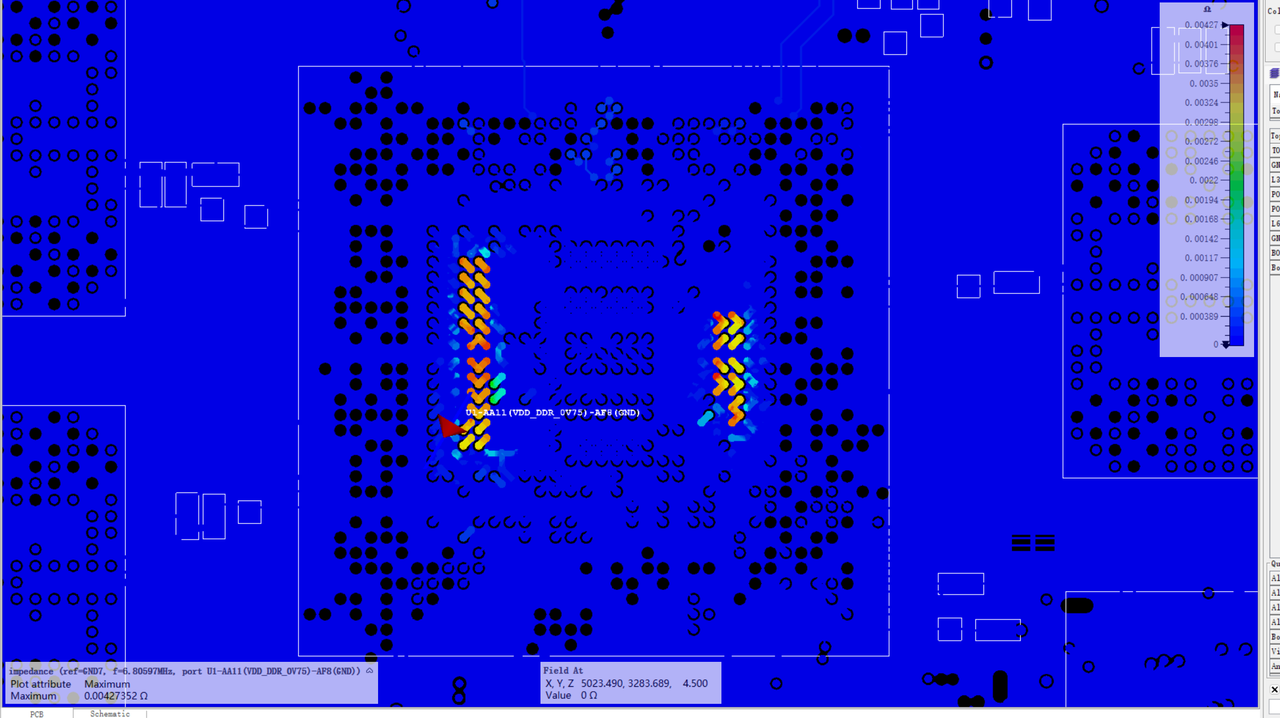

整体的布局布线的分布情况如下所示:

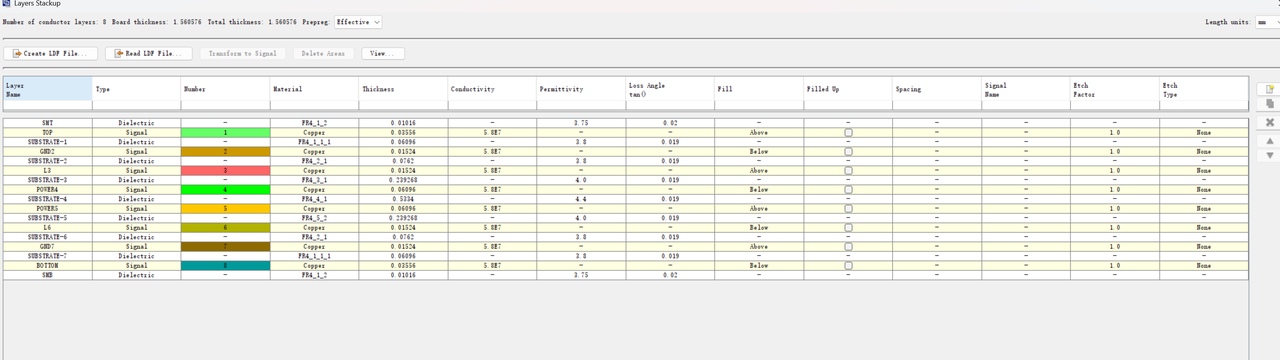

二,小编我开始了导入ODB++文件和编辑层叠:

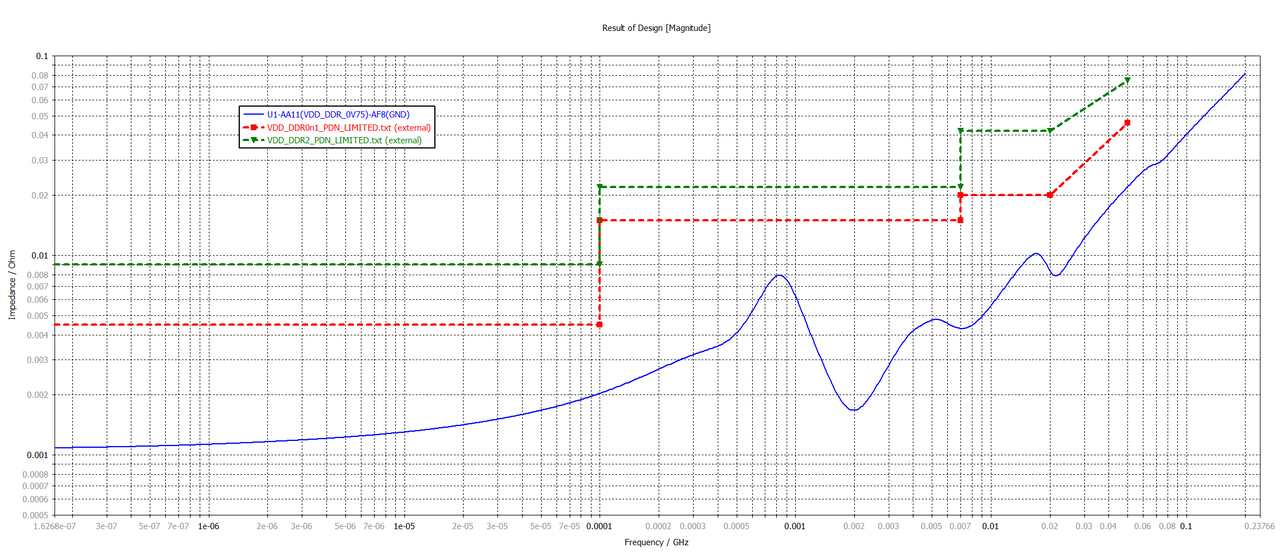

最后仿真得出的电源网络VDD_DDR_0V75的PDN曲线:

小编我于是乎就立马得出了这样的结论:VDD_DDR0N1和VDD_DDR2网络的PDN要求前者稍微更加严苛一些,建议PDN的限值曲线还是使用第一个比较好一些。但是你认为你这样就结束了吗?

NO,NO ,NO,下期文章小编我为道友您揭秘其中的玄机,我们下期文章不见不散

。

--------声明:本文属于小编的原创文章,如需转载请注明来源!