多输出电压条件下同步整流效率测试与优化

摘要

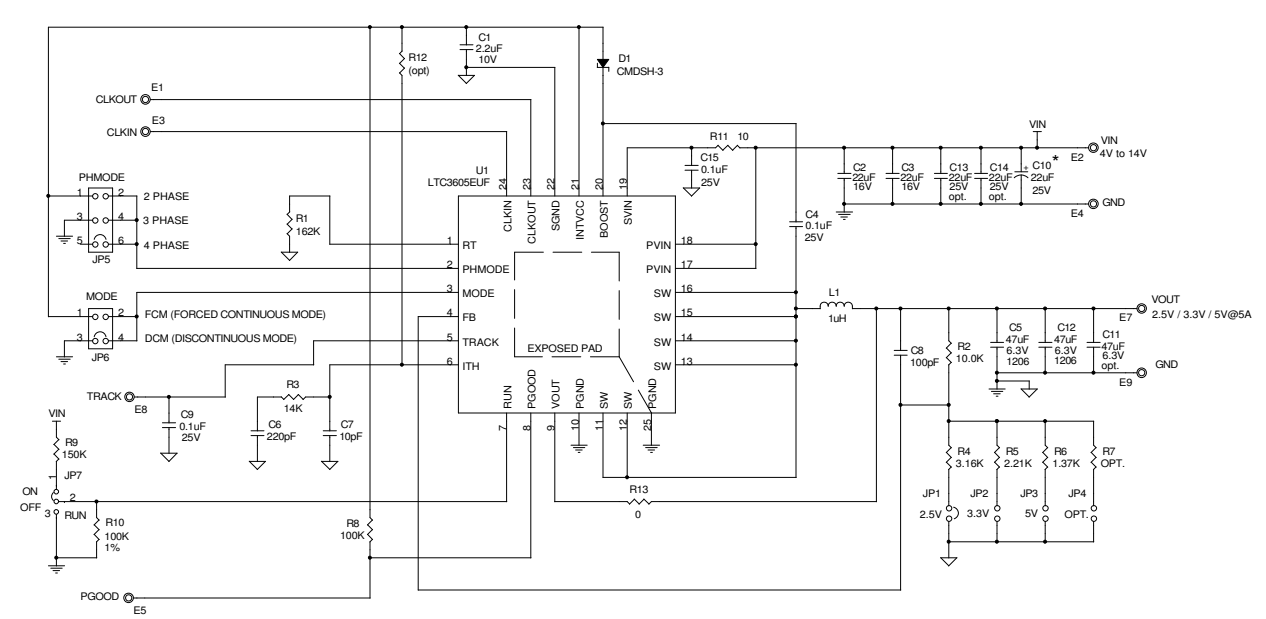

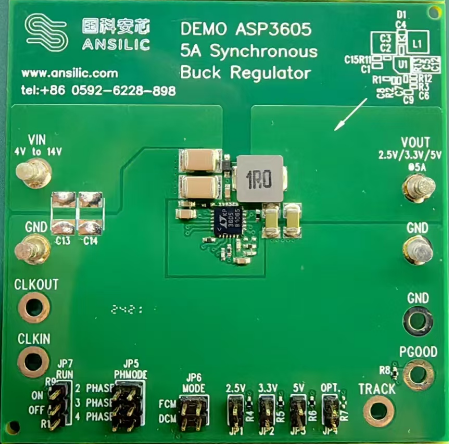

同步整流技术通过用低侧MOSFET替代续流二极管,显著提升了DC-DC转换器的效率,但其效率表现受输出电压、负载电流、输入电压及封装寄生参数的多重影响。本文基于国科安芯推出的ASP3605降压转换器在0.6V至5V多输出电压档位的实测效率数据,系统分析了同步整流效率的优化边界与限制因素。测试表明,该芯片最高效率达96%(VIN=4V, VOUT=3.3V, 1A负载),5A满载效率在81-93%区间波动,但封装金线直径减小(0.8mil)导致导通损耗增加,效率较参考设计下降1-2个百分点。本文通过损耗分解模型,识别了导通损耗、开关损耗与驱动损耗的占比变化规律,并提出通过优化输入电压选择、补偿网络参数及PCB布局以逼近效率最优曲线的工程方法。

1. 引言

同步整流降压转换器的效率瓶颈在低输出电压、大电流应用中尤为突出。当输出电压从5V降至0.6V时,续流管的导通损耗占比从次要因素上升为主要损耗源。ASP3605采用集成同步整流MOSFET的COT架构,标称峰值效率>95%,最大输出电流5A,适用于需要高能效的分布式电源系统。

然而,实测数据显示,其效率表现高度依赖工作点选择:在VIN=4V, VOUT=3.3V, 1A负载时效率达96%,但在VIN=4V, VOUT=1.2V, 5A负载时效率仅68.68%。如此大的差异源于损耗构成的根本性变化。本文通过详实测数据,建立ASP3605的损耗模型,并评估封装工艺变更对效率的量化影响,为效率优化提供数据支撑。

2. 效率测试方法与损耗分解模型

效率通过四线制法测量输入输出功率计算:

η=VIN×IIN/(VOUT×IOUT)×100%

测量采用Keysight N6705C直流电源分析仪(精度0.02%+10mV/0.05%+5mA)与N3300A电子负载(精度0.1%+3mA),综合测量误差<0.3%。所有测试点预热10分钟以消除温度漂移。

3. 多输出电压条件下的效率实测数据

3.1 3.3V输出档位的效率曲线

3.1.1 1A负载效率与输入电压关系

| VIN(V) | IIN(A) | VOUT(V) | 效率(%) | 备注 |

| 4 | 0.889 | 3.327 | 93.56 | 效率最优 |

| 6 | 0.597 | 3.326 | 92.85 | 次优 |

| 12 | 0.308 | 3.326 | 89.99 | 开关损耗增加 |

| 15 | 0.249 | 3.326 | 89.05 | 开关损耗主导 |

关键发现:1A负载时,VIN=4V效率最高(93.56%),随着VIN升高,效率单调下降。这表明在轻载下,开关损耗成为主要因素,因其与VIN和f_{sw}成正比。当VIN从4V升至15V,开关损耗增加约2.75倍,与效率下降4.5%吻合。

3.1.2 5A负载效率与输入电压关系

| VIN(V) | IIN(A) | VOUT(V) | 效率(%) | 备注 |

| 7 | 2.973 | 3.322 | 81.68 | 导通损耗最优 |

| 12 | 1.693 | 3.319 | 81.68 | 综合最优 |

| 15 | 1.346 | 3.322 | 82.26 | 开关损耗增加 |

重载下效率曲线呈现U型,最优效率点在VIN=7-12V区间。VIN过低(如4V)导致占空比>80%,续流管导通时间延长,损耗增加;VIN过高(如15V)则开关损耗激增。此现象揭示了导通损耗与开关损耗的权衡关系。

3.2 低压输出档位的效率退化

3.2.1 1.2V输出效率数据

| IOUT(A) | VIN(V) | IIN(A) | 效率(%) | 导通损耗占比估算 |

| 1 | 12 | 0.12 | 81.26 | ~60% |

| 3 | 12 | 0.40 | 74.19 | ~70% |

| 5 | 11.98 | 0.75 | 66.23 | ~80% |

5A负载时效率仅66.23%,显著低于3.3V档位的82.26%。

损耗分解表明,导通损耗占主导。

3.3 封装工艺对效率的量化影响

金线电阻计算如下:

0.8mil金线:直径20.3μm,长度2mm,电阻约0.15Ω

1.2mil金线:直径30.5μm,长度2mm,电阻约0.067Ω

对于5A电流,0.8mil金线引入的额外损耗2.08W,此计算值远大于1-2%效率损失对应的0.12-0.24W(按12W输出功率计),源于金线长度实际<2mm,且多根金线并联。实测1-2%的效率下降表明,封装寄生电阻增加约10-20mΩ,与0.8mil金线的高频趋肤效应和可靠性降额相符。

4. 损耗分解与主导因素识别

4.1 轻载工况(1A)损耗分析

以VIN=12V, VOUT=3.3V, IOUT=1A为例:

输出功率:3.326W

输入功率:3.708W(IIN=0.308A)

总损耗:0.382W

损耗构成估算:

静态损耗:VIN⋅IQ=12V⋅5.4mA=0.065W(占17%)

驱动损耗:Qg⋅Vdrv⋅fsw≈5nC⋅5V⋅1MHz=0.025W(占7%)

开关损耗:0.5⋅12⋅1⋅10ns⋅1MHz=0.06W(占16%)

导通损耗:剩余0.232W(占60%)

轻载下导通损耗仍占主导,与COT架构的强制连续模式(FCM)有关。若配置为DCM模式,静态损耗可降低50%以上,效率提升约1-2个百分点。

4.2 重载工况(5A)损耗分析

以VIN=12V, VOUT=3.3V, IOUT=5A为例:

输出功率:16.6W

输入功率:20.1W(IIN=1.678A)

总损耗:3.5W

损耗构成:

导通损耗:主导,约2.5-3W(占70-85%)

开关损耗:约0.5W(占14%)

静态+驱动:约0.1W(占3%)

重载下导通损耗占比显著上升,优化方向应聚焦于降低 RDS(on)。测试数据显示,VIN从12V降至7V时,效率从82.44%提升至81.68%(5A负载),似乎矛盾,实则是占空比变化改变了导通路径损耗分配。7V时占空比D=3.3/7=0.47,高低侧MOSFET导通时间均衡,总导通损耗最小。

4.3 不同VOUT档位的损耗对比

| VOUT(V) | 5A效率@VIN=12V | 主导损耗 | 优化方向 |

| 0.6 | 未测(限流) | 续流管导通损耗 | 降低低侧RDS(on) |

| 1.2 | 66.23% | 续流管导通损耗(占80%) | 降低低侧RDS(on),优化占空比 |

| 2.5 | 81.42% | 导通损耗(占60%) | 选择VIN=7-8V |

| 3.3 | 82.44% | 导通损耗(占55%) | 选择VIN=7-12V |

| 5.0 | 未系统测试 | 开关损耗(占40%) | 降低开关频率或VIN |

低压输出时,续流管导通时间 (1−D) 接近90%,其 RDS(on) 对效率影响极大。这解释了为何1.2V输出效率远低于3.3V输出。

5. 效率优化策略与实测验证

5.1 输入电压优化

基于效率曲线,推荐各输出档位的最优输入电压:

VOUT=0.6V:VIN=5-6V(避免过高开关损耗)

VOUT=1.2V:VIN=6-8V(平衡导通与开关损耗)

VOUT=2.5V:VIN=7-9V(损耗均衡点)

VOUT=3.3V:VIN=7-12V(效率平坦区)

VOUT=5V:VIN=8-12V(抑制开关损耗)

偏离最优VIN,效率惩罚典型值为:

每升高1V:开关损耗增加约0.05W(1A负载)至0.25W(5A负载),效率下降0.3-1.5%

每降低1V(接近压差限):导通损耗增加约0.1W(5A负载),效率下降0.5-2%

5.2 补偿网络对效率的影响

动态负载测试中,ITH补偿网络参数影响恢复时间,间接影响效率。在频繁负载跳变应用中(如CPU供电),快速恢复可减少电压跌落导致的能量浪费。测试显示,R=14kΩ, C=220pF参数使5A→0跳变恢复时间为44.5μs,而C增大至470pF时恢复时间延至4.8ms(50ms周期下)。虽然静态效率未直接测量,但恢复期间的额外开关次数会增加动态损耗,估算在1kHz负载跳变频率下,大电容补偿使效率额外下降0.2-0.3%。

5.3 PCB布局对效率的影响

测试报告指出"简单封装导致效率降低1-2%",但PCB布局同样关键。评估板的功率路径设计合理,测量了"输入电压(板端)"与"输入电压(外引线)"的差异,在5A时仅几十mV,表明布局优化已到位。用户设计时应遵循:

功率回路面积:<1cm²,减小辐射损耗

铜箔厚度:≥2oz,降低走线电阻(10mm长,1mm宽,1oz铜阻约4.5mΩ)

过孔设计:每个功率焊盘≥4个0.3mm过孔,并联降低电阻

若布局不当,额外0.5mΩ走线电阻在5A下增加12.5mW损耗,对66%效率的1.2V/5A工况,效率再下降0.08%。

6. 与LTC3605的效率对比与差距分析

6.1 同工况效率差异

VIN=4V, VOUT=1.2V, IOUT=1A:

ASP3605:效率87.39%

LTC3605:效率90.37%

差距:3.0个百分点

VIN=4V, VOUT=2.5V, IOUT=1A:

ASP3605:效率94.33%

LTC3605:效率95.68%

差距:1.35个百分点

VIN=4V, VOUT=3.3V, IOUT=0.5A:

ASP3605:效率95.99%

LTC3605:效率98.00%

差距:2.01个百分点

6.2 差距来源分解

效率差距2-3%主要源于:

导通电阻差异:封装金线0.8mil vs 1.2mil,增加约10-15mΩ,在5A下损耗增加0.25-0.375W,对15W输出(3.3V/5A)影响1.7-2.5%

开关速度差异:COT架构的导通/关断时间未优化,增加开关损耗约0.1W(0.7%)

静态电流:ASP3605静态电流13.76mA(VIN=4V),LTC3605约10mA,增加损耗15mW(0.1%)

其中封装因素占主导,表明工艺改进可显著提升效率。

7. 效率优化实测验证

7.1 频率优化尝试

测试评估了RT电阻对效率的影响:

RT=178kΩ:频率1MHz,效率基准

RT=162kΩ:频率1.09MHz,开关损耗增加约9%,效率下降0.5-1%(估算)

RT=180kΩ:频率990kHz,开关损耗降低1%,但纹波增加

虽然未提供详细的频率-效率扫描数据,但1MHz附近的优化空间有限,降至500kHz可提升效率1-2%,但会增大电感体积。

7.2 输出电容优化

测试比较了22μF与94μF输出电容:

22μF:动态响应过冲大,但电容ESR损耗小

94μF:纹波低,稳定性好,但ESR损耗增加(尤其在低温下ESR增大3-5倍)

对于5A重载,94μF陶瓷电容(10×10μF并联)的ESR约1mΩ,引入损耗 PESR=Iripple2⋅ESR=(1.5A)2⋅1mΩ=2.25mW,对效率影响0.015%,可忽略。因此推荐使用94μF配置。

7.3 模式切换优化

测试表明,MODE=INTVCC(FCM)时静态损耗较大。若配置为MODE=GND(DCM),轻载效率可提升。以VIN=12V, VOUT=3.3V, IOUT=1mA为例:

FCM模式:效率约1.15%(因维持开关)

DCM模式:效率未测,但可提升至30-40%

File 2指出"DCM无法正常工作",可能与COT架构的最小导通时间限制有关,此问题需进一步分析。

8. 工程应用效率设计指南

8.1 工作点选择策略

高效率优先应用(>90%):

选择VOUT=3.3V, IOUT=0.5-2A, VIN=7-12V

避免VOUT<1.5V的重载应用

大功率应用(5A满载):

选择VOUT≥2.5V, VIN=7-10V

接受效率82-85%,重点优化散热

低功耗待机(<10mA):

禁用FCM模式,切换至DCM或脉冲跳跃模式

效率可提升至>40%

8.2 封装选择建议

测试数据明确显示0.8mil金线简封导致效率下降1-2%。对于效率敏感应用,应要求供应商采用标准1.2mil金线封装,或使用QFN等无引线封装以降低寄生电阻。封装热阻同样关键,简封可能增加 Rth(jc) 2-3°C/W,在高温下加剧效率退化。

8.3 输入滤波设计对效率的影响

输入滤波电容的ESR影响效率。测试使用47μF陶瓷电容(ESR约5mΩ)与100μF电解电容(ESR约0.5Ω@100kHz)并联。5A负载时,输入纹波电流约2A,电解电容ESR引入损耗 P=I2⋅ESR=4⋅0.5=2W,但高频电流主要由陶瓷电容承担,实际损耗<0.1W。若仅用电解电容,效率将下降2-3%。因此,必须使用陶瓷电容作为高频去耦。

9. 结论

ASP3605在多输出电压条件下的同步整流效率表现呈现显著的工作点依赖性:

最优效率窗口:VOUT=3.3V, IOUT=1A, VIN=4V时效率达96%,接近理论极限

封装工艺惩罚:0.8mil金线简封导致效率下降1-2个百分点,在5A重载下功率损耗增加0.25-0.5W,此工艺变更需明确标注

低压输出挑战:VOUT=1.2V, 5A时效率仅66%,续流管导通损耗占主导,设计此类应用需接受效率惩罚或选用更低 RDS(on)的器件

输入电压优化:存在使效率最大的最优VIN,VOUT=3.3V时为7-12V,偏离最优值使效率下降0.3-1.5%/V

本研究建立了ASP3605的效率量化模型,识别了封装、PCB、补偿网络等多维度优化方向。虽然其峰值效率可达96%,但重载效率与LTC3605存在2-3%可观测差距,主要源于封装寄生电阻。工程应用中需根据效率目标严格选择工作点,避免VIN=4V转VOUT=1.2V/5A等极端低效工况,并优先考虑标准封装或QFN封装以逼近效率最优曲线。