【FPGA】时序逻辑计数器——板级验证

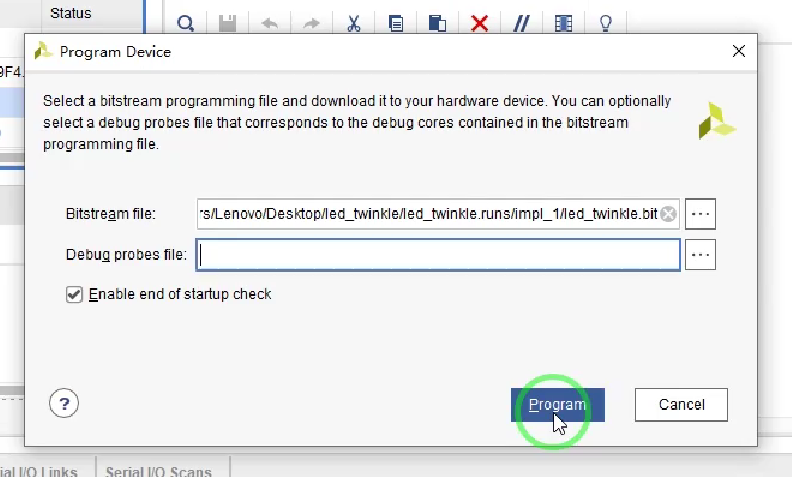

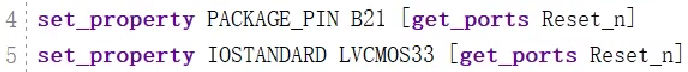

1.确定物理硬件和设计功能之间的端口关系

时钟由晶振提供

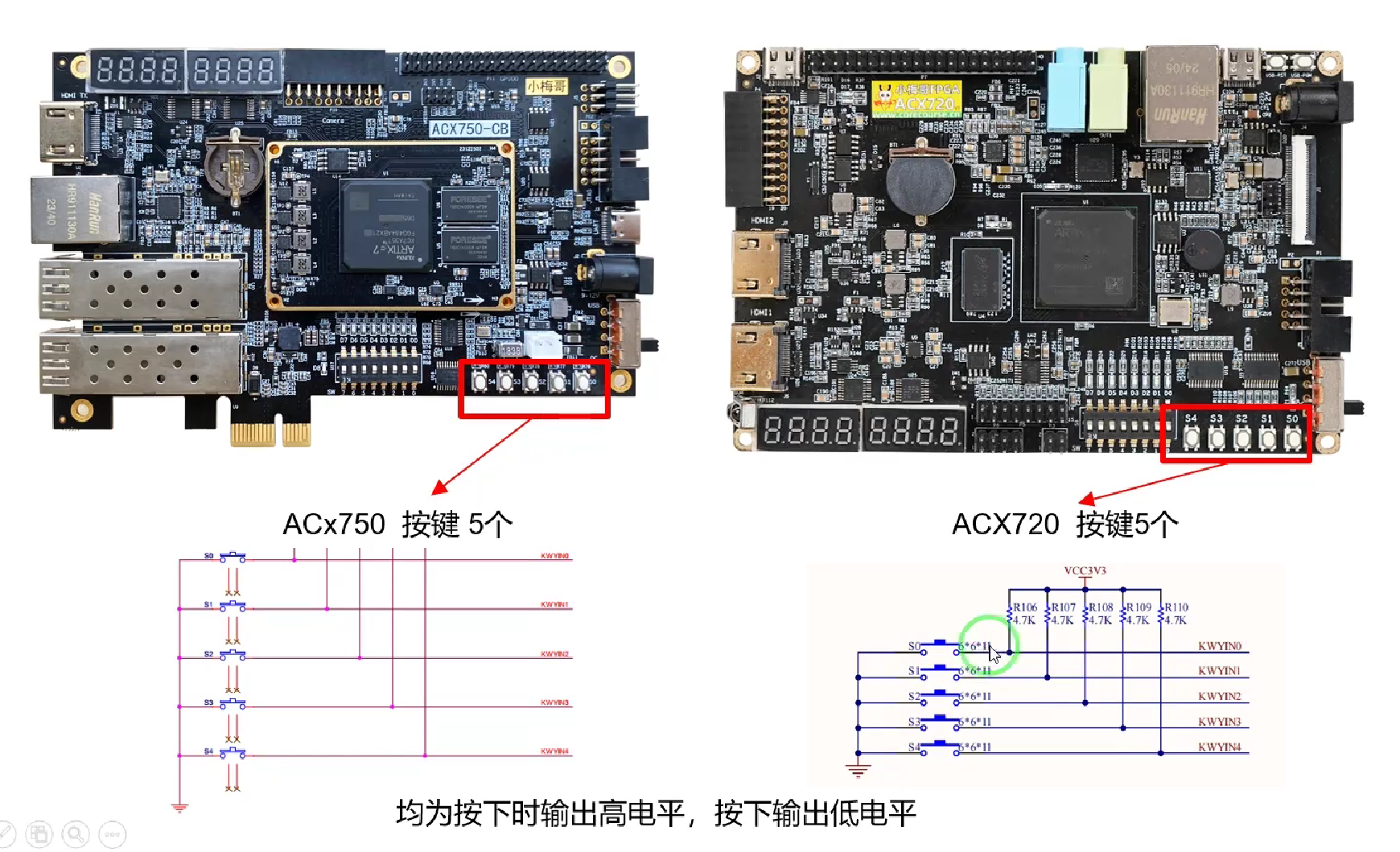

复位信号高电平正常运行,低电平进入复位状态

an按键可以用来提供复位信号

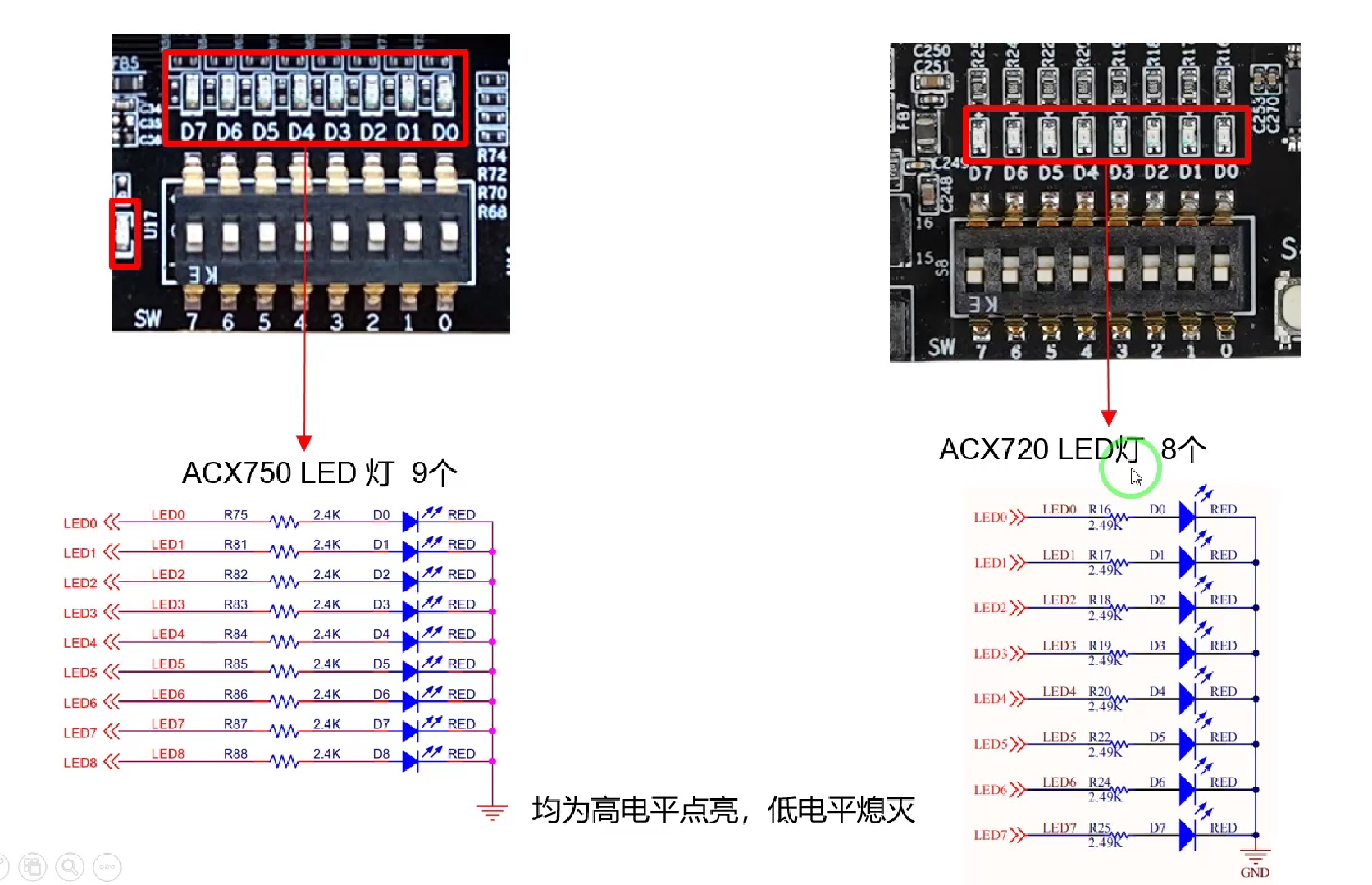

Led输出

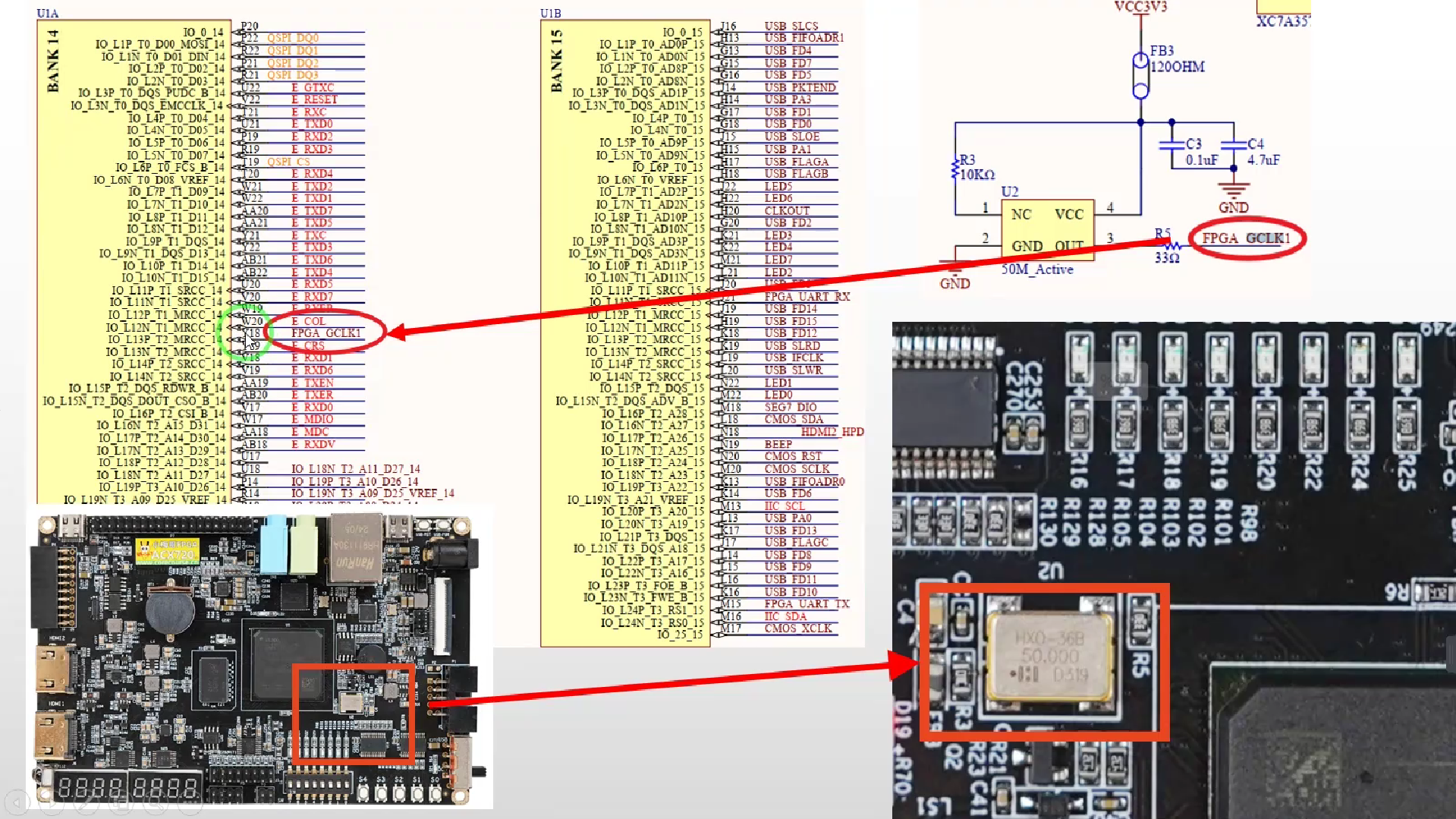

2.管脚约束

可以跳过图形界面自行编写xdc文件内容进行管脚约束

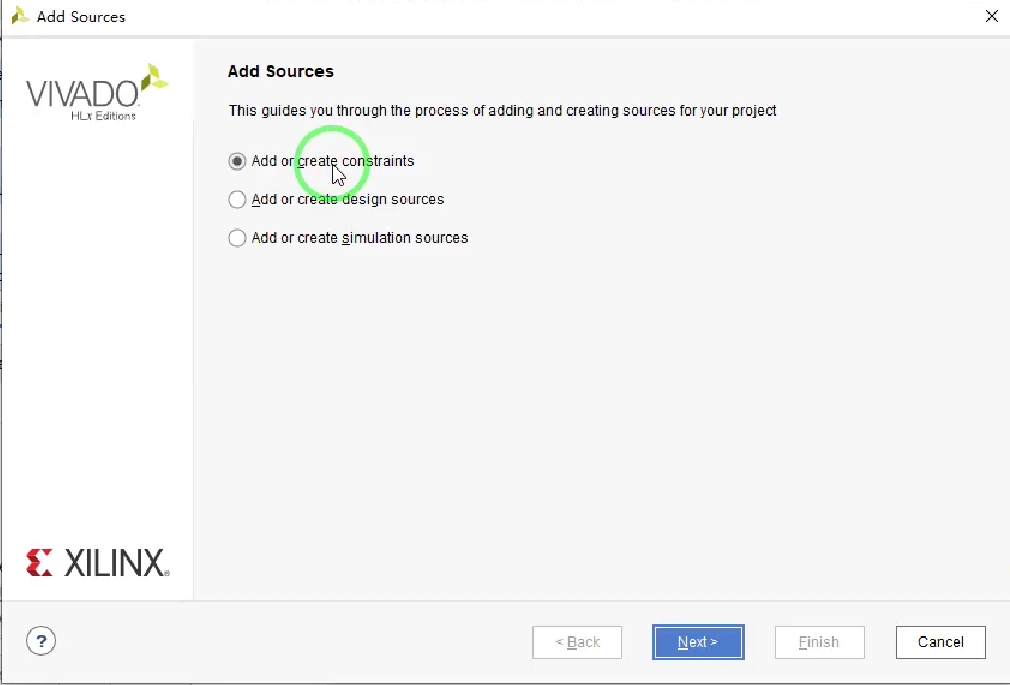

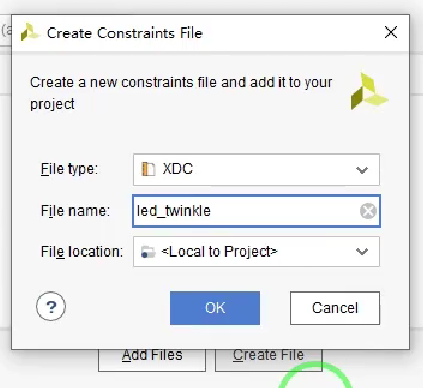

创建xdc文件,组合键Alt+A,选择第一个,创建一个约束文件

创建文件

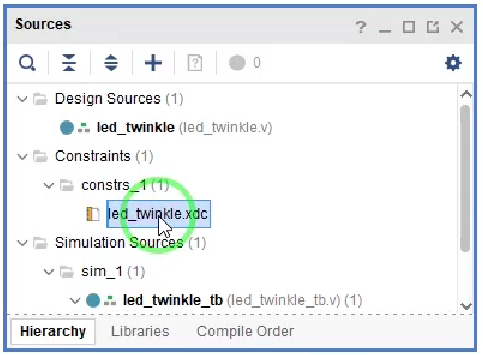

打开刚创建的文件

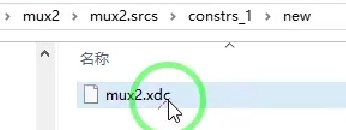

找到之前mux2的xdc文件

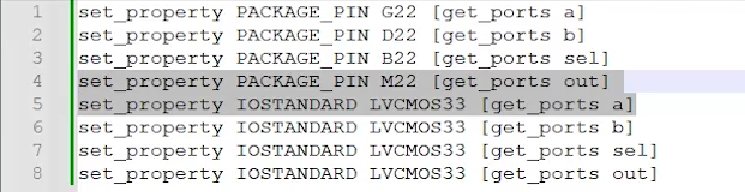

复制两行代码

- 设置管脚位置

- 设置管脚的电平标准

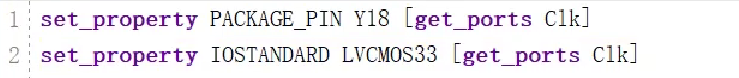

1)对Clk管脚进行约束

Clk对应的是晶振

ACX750开发板对应W19

ACX720开发板对应Y18

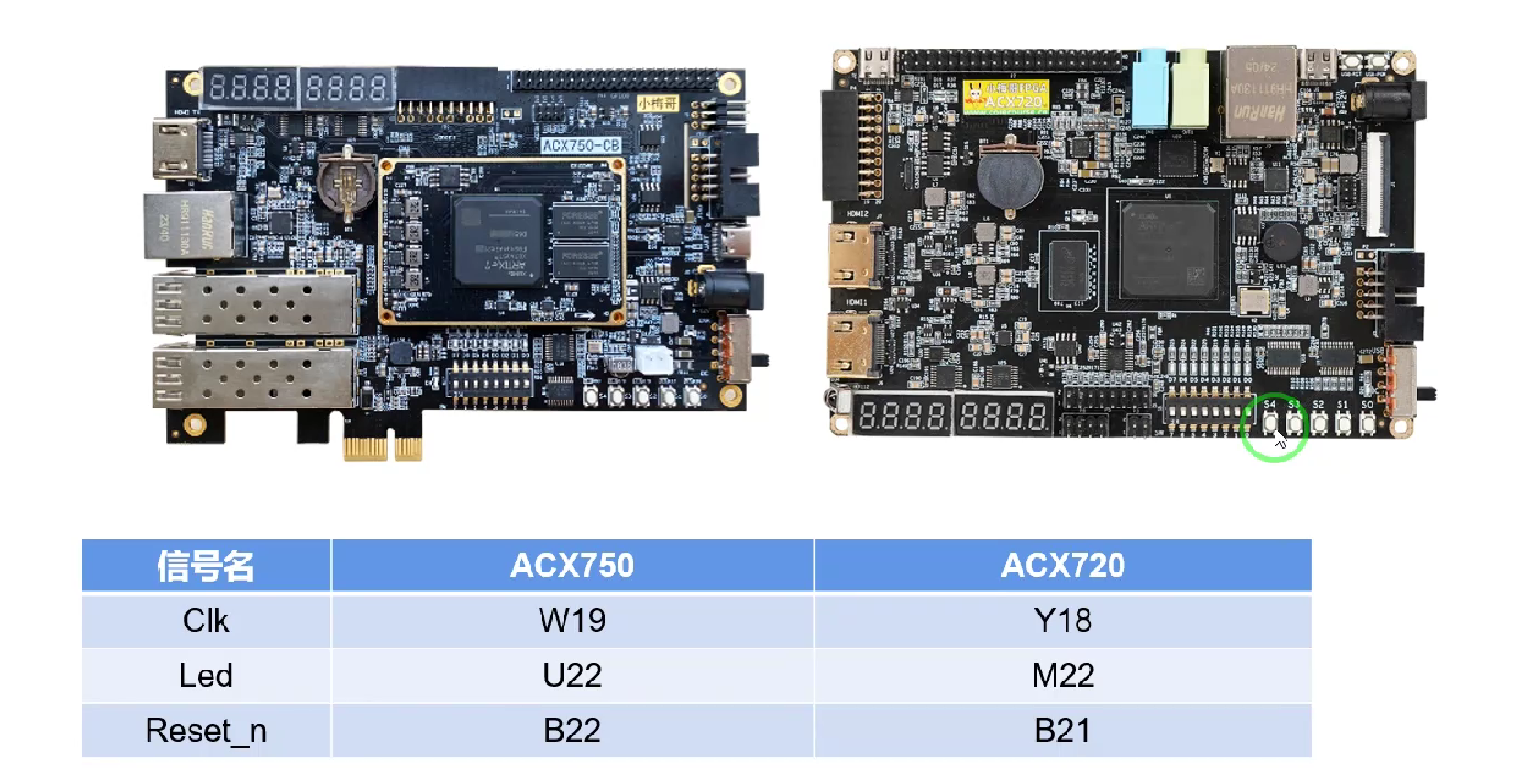

2)对复位的管脚进行约束

复位对应的是按键

S4对应B21

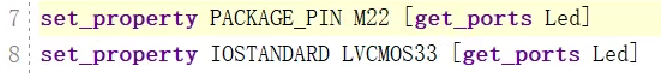

3)对Led的管脚进行约束

Led0对应M22

电平在复制的时候已经修改好了,所以这里不用修改

在论坛的自助服务手册的三楼也有写好的代码框架

将需要的代码复制到工程中修改一下管脚名称和对应的引脚即可

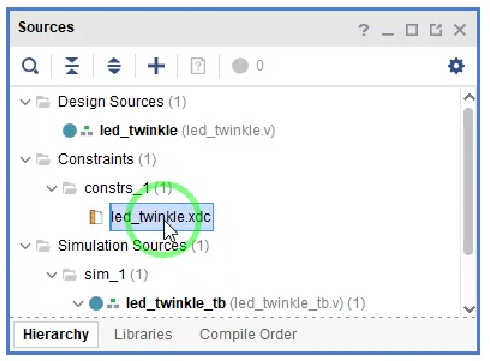

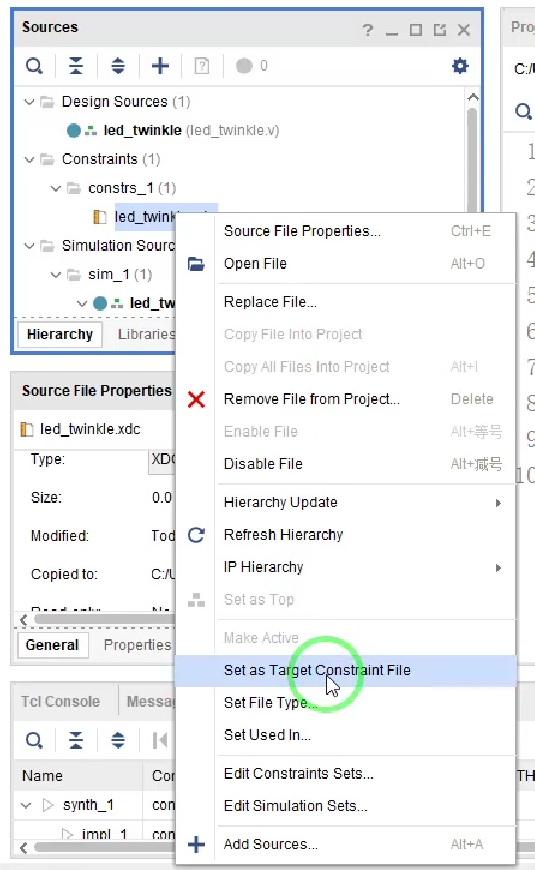

3.设置目标约束文件

此时文件并没有target的字样,就证明该文件当前还不是工程的目标约束文件

右击找到图示选项即可完成设置

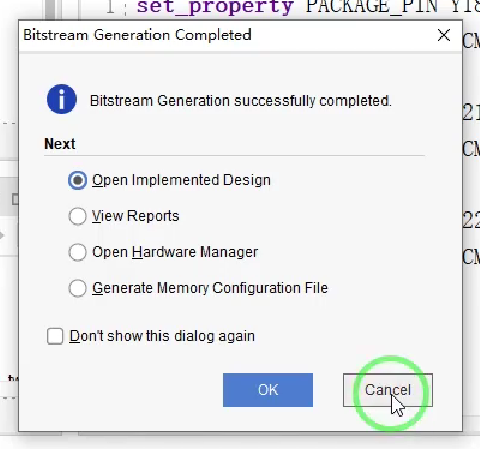

4.产生beat文件

按图示选项选择,生成可以直接下载到FPGA中的beat文件

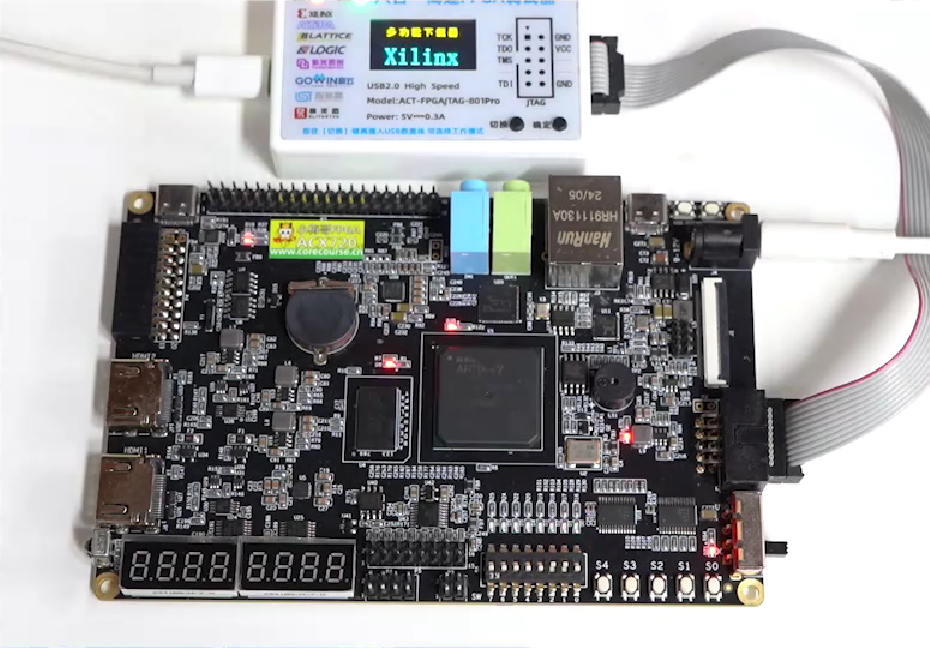

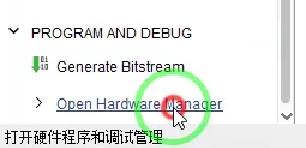

需要确保电脑已经连接了专用下载器,并且打开了开发板的电源开关

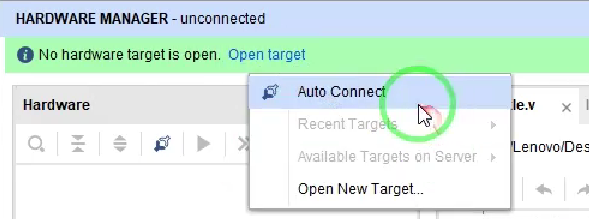

点击图示选项

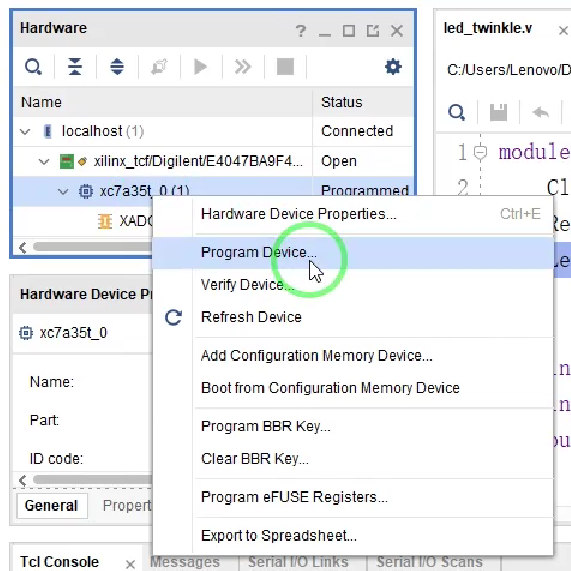

选中芯片右键选中