Marin说PCB之高速差分信号设计:紧耦合还是松耦合?

一,基本概念:

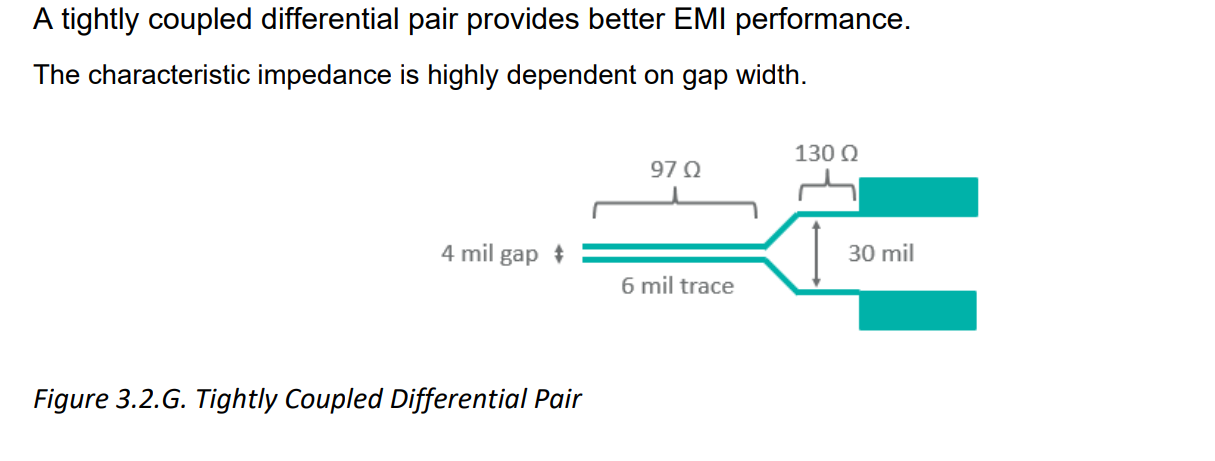

A,紧耦合:指差分对的两根走线间距非常小,通常小于或等于线宽(S ≤ W)。

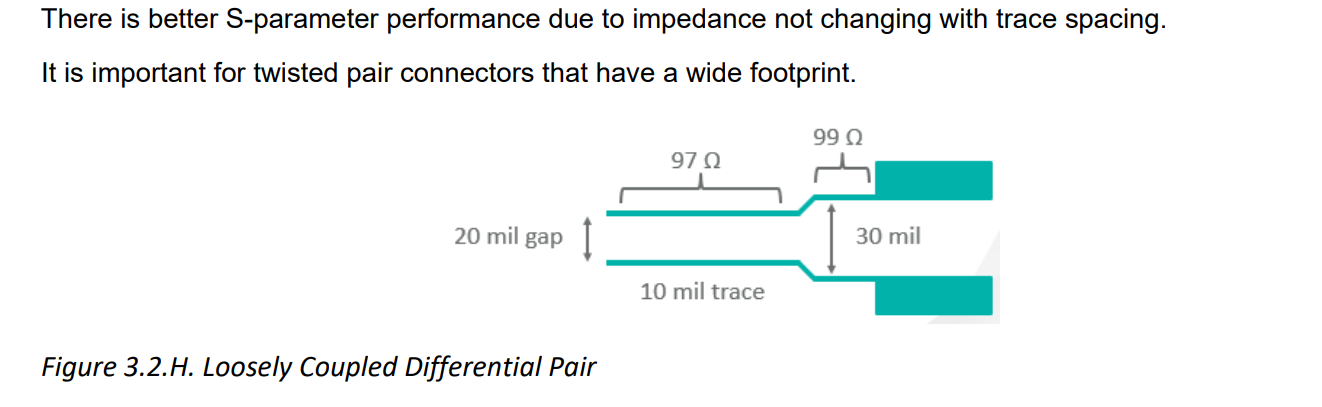

B, 松耦合:指差分对的两根走线间距相对较大,通常大于线宽(S > W)。

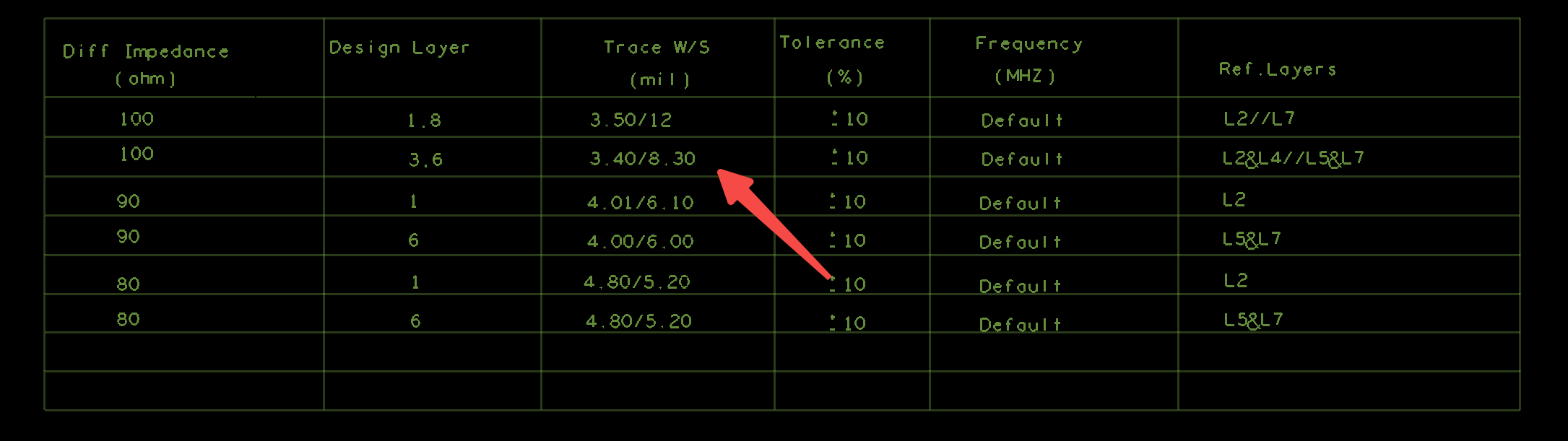

首先来看下我们实际单板上的高速差分线到底是按照哪种耦合方式设计的:

二,对比分析:紧耦合 vs. 松耦合

首先我们通过考虑单端信号对于差分对的串扰,来去分析紧耦合 vs.松耦合对差分噪声和共模噪声的抗干扰能力。

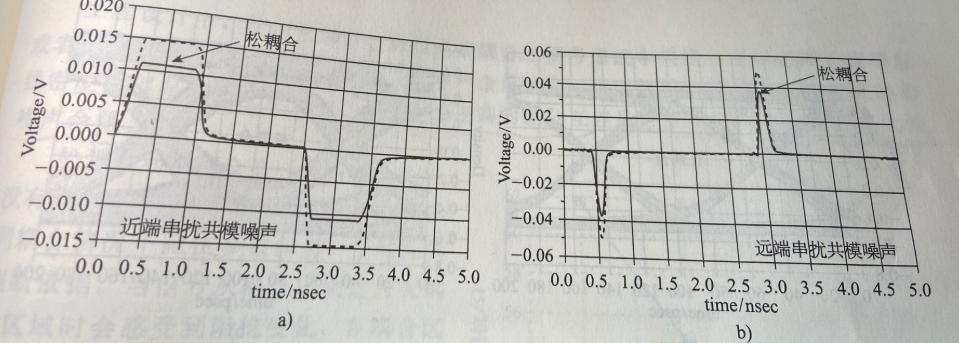

A,对比松紧耦合的两种CASE下,串扰引起的差分噪声的大小,其抗差分噪声的能力:

B,对比松紧耦合的两种CASE下,串扰引起的差分噪声的大小,其抗共模噪声的能力:

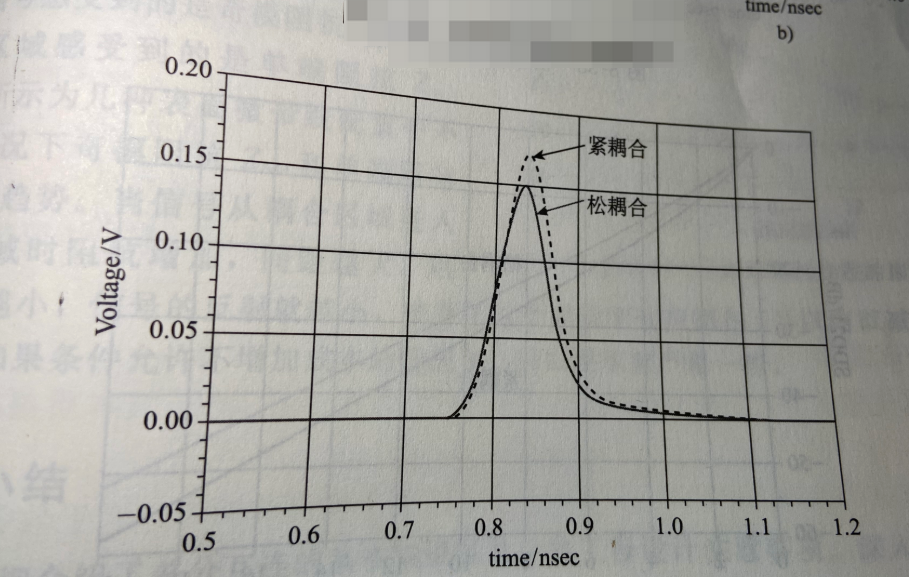

C,还有一种情况就是我们的驱动器的两个信号输出存在偏斜后者是我们单板的差分对走线存在无耦合区域的时候,通常紧耦合的差分对会产生更大的共模噪声,共模噪声在传输线中反复反射和震荡会使得接收端的信号抖动增加,最终造成我们传输线的信号质量眼图恶化。

通过以上的两组仿真数据可以得知:紧耦合的差分线抗差分噪声的能力是优于松耦合的,但其抗共模噪声的能力是弱于松耦合的。

D,使用松耦合对信号的衰减也有一定的好处。通常对于我们的PCB走线来说,若是单板的层叠厚度都已经确定了,差分线使用松耦合的情况下由于其间距加大,走线的宽度也是必然加大的,趋肤效应引起的信号损耗就会相应的减少了,这损害的改善在长距离互链接的差分对中非常重要的。

所以综上来看的话还是松耦合的差分对性能优于紧耦合的。

小编我列出一个表格供给诸位道友们一起看下:

| 特性 | 紧耦合 | 松耦合 |

| 耦合强度 | 强 | 弱 |

| 对参考平面依赖性 | 较低 | 较高 |

| 抗外部不对称干扰能力 | 较好(因为两根线紧贴,所处环境非常相似) | 稍差(因为两根线距离较远,可能受到不同程度的干扰) |

| 布板密度 | 高,节省空间 | 低,需要更多空间 |

| 阻抗可控性 | 对叠层变化敏感(如介质厚度、介电常数变化),可能导致阻抗波动 | 对叠层变化相对不敏感,阻抗更稳定,更易控制 |

| 与地/电源层距离变化 | 敏感度较低 | 敏感度较高 |

| 设计难度 | 相对容易(因为间距固定且小,容易保持等距) | 相对容易(现代EDA工具能很好地处理) |

| 主流程度 | 传统设计常用 | 现代高速设计(>5Gbps)的主流选择 |

结论与设计建议

对于绝大多数现代高速串行链路(如PCIe4.0, MIPI, USB3.1, 10G/25G以太网等),小编我的建议还是优先去推荐使用松耦合。

具体建议:

首选松耦合:将差分对的内间距设置为 1.5倍到2倍的线宽(S = 1.5W ~ 2W)。这是一个很好的起点,能在布线密度和阻抗稳定性之间取得平衡。

保持一致性:无论选择哪种耦合方式,整个走线路径上保持“等长”和“等距” 是我们高速PCB设计准则的中一条不变的铁律。

优先相信你的参考平面:确保差分线下方的参考平面完整、无割裂。这是保证信号质量比追求紧耦合那一点点理论上的抗干扰优势更重要。

使用阻抗计算工具:不要猜测。使用Polar SI9000或其他EDA工具,根据你的PCB叠层和目标阻抗,精确计算出所需的线宽和间距。你会发现,为了达到目标阻抗(如100Ω),松耦合通常是更自然、更稳健的选择。

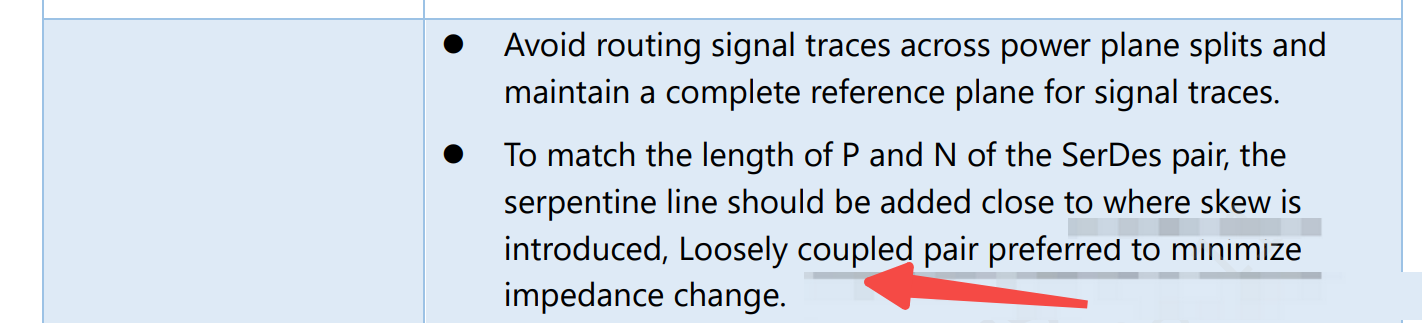

遵循设计规范:如果芯片厂商(如Intel, 地平线,美信)的设计指南中有明确要求,请务必优先遵循其规范。

例如某家芯片手册上对其PEIC信号上布线要求就有提及到差分线优先使用松耦合模式。

总而言之,将你的设计建立在“松耦合+完整参考平面”的基础上,是当前高速差分信号设计更可靠、更主流的方法。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!