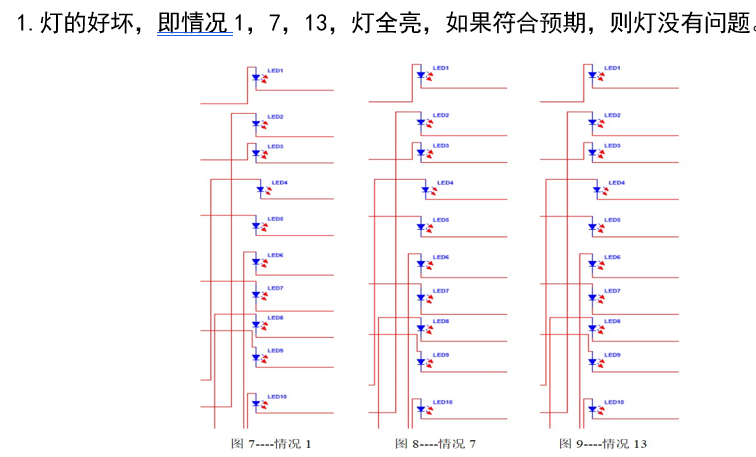

【数字逻辑】24进制LED综合控制实战!10灯精准执行(74HC161+138+139完整方案)

24进制LED综合控制实战!10灯按“奇灭→偶灭→依次灭”精准执行(74HC161+138+139完整方案)

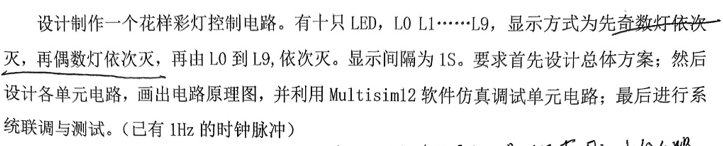

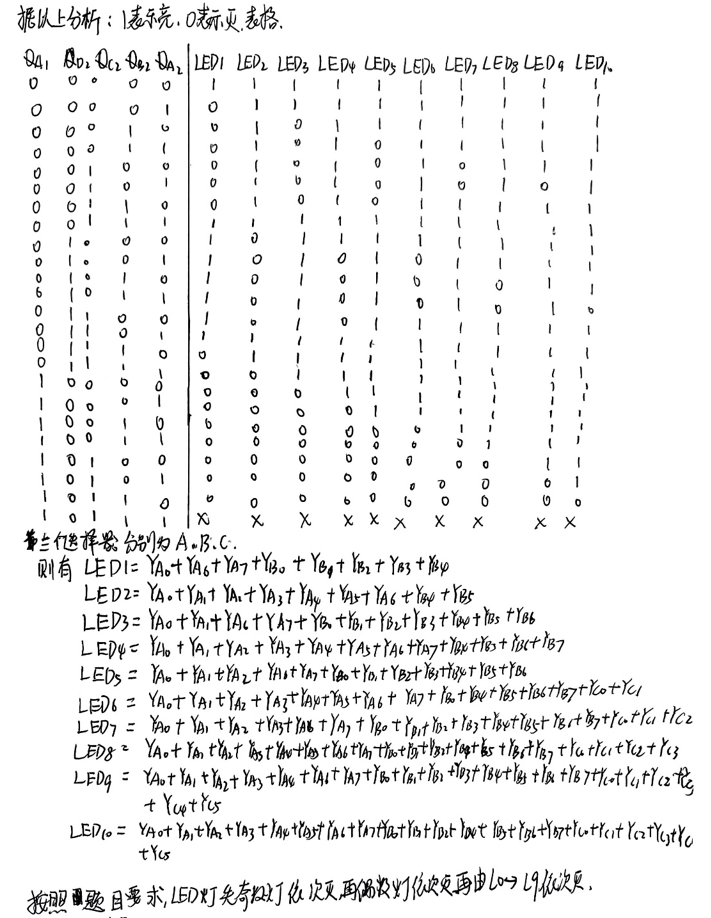

刚做这个综合实验时,我对着一堆芯片和10个LED发懵:24进制怎么和LED灭灯顺序挂钩?为什么要拆成3个8进制?奇灭、偶灭、依次灭的逻辑怎么用电路实现?后来才发现核心是“把24个状态对应3个灭灯阶段,用计数器分阶段,译码器选LED,选择器控阶段切换”。今天就从需求拆解到模块接线,跟着做就能实现实验要求的灭灯逻辑。

一、先明确:实验要做啥?核心难点在哪?

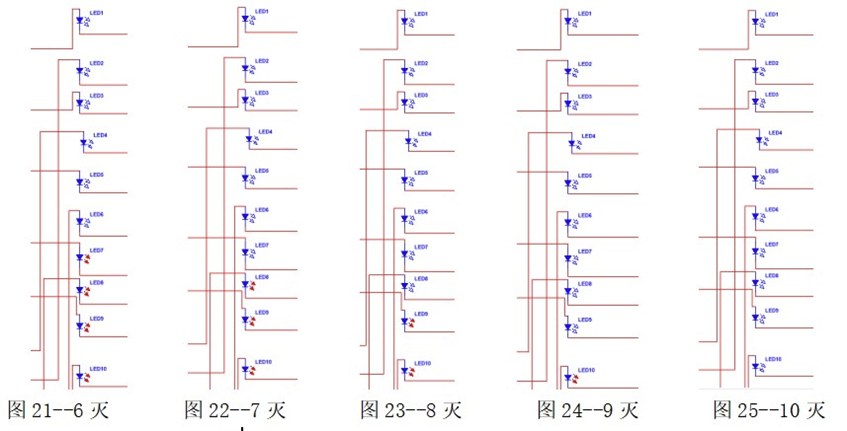

1. 实验核心需求(必须先吃透)

- LED数量:10个(LED1~LED10),初始全亮;

- 灭灯顺序:分3个阶段,共24个状态(对应24进制):

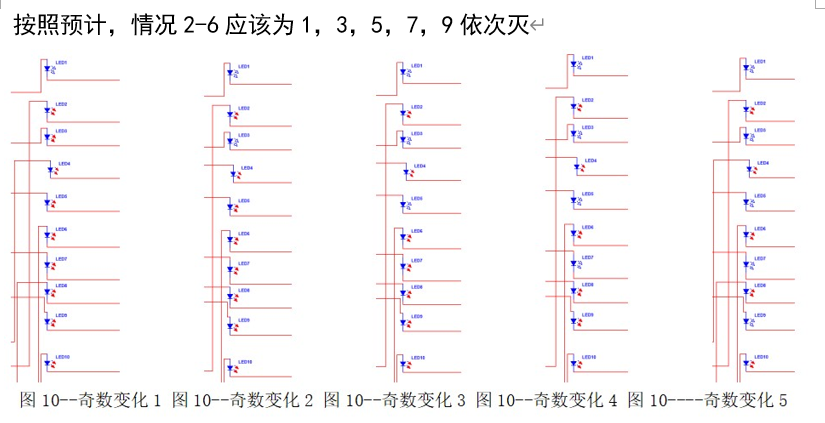

- 阶段1(状态0~4):奇数灯依次灭(LED1→LED3→LED5→LED7→LED9);

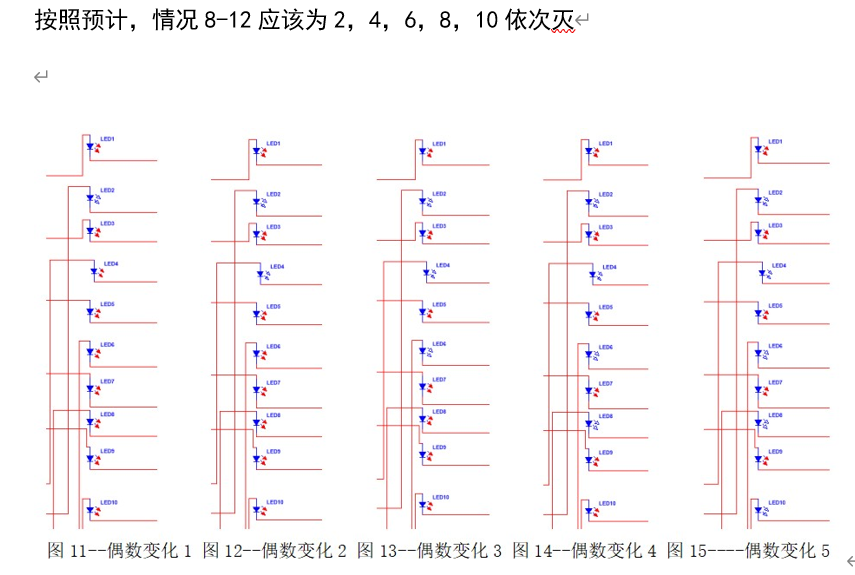

- 阶段2(状态5~9):偶数灯依次灭(LED2→LED4→LED6→LED8→LED10);

- 阶段3(状态10~23):10个灯依次灭(LED1→LED2→…→LED10);

- 控制核心:用24进制计数器生成24个状态,每个状态对应1个灭灯动作。

2. 核心难点与解决思路

- 难点1:24进制怎么实现?

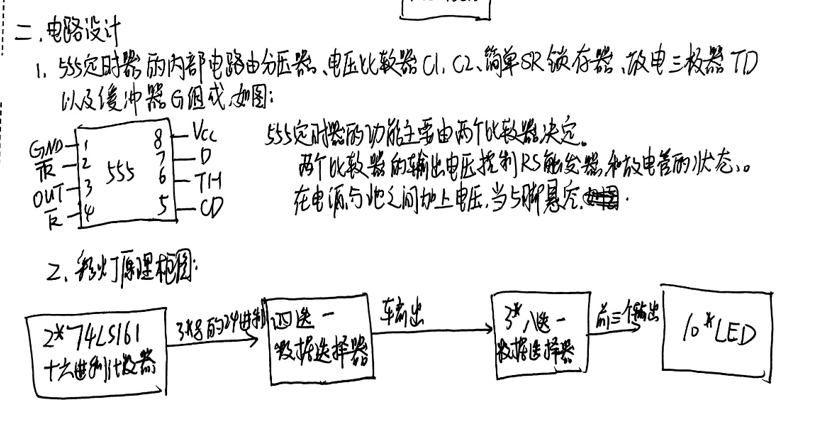

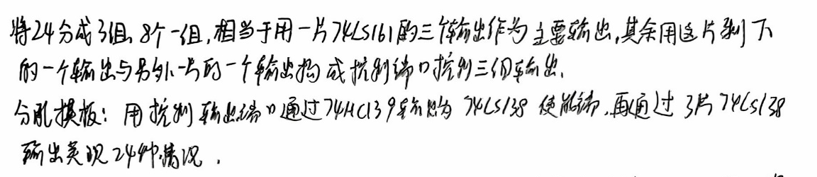

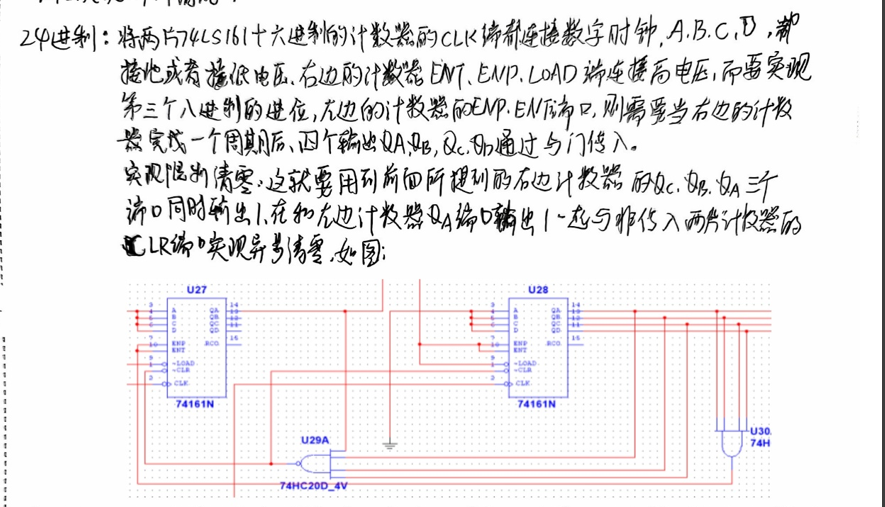

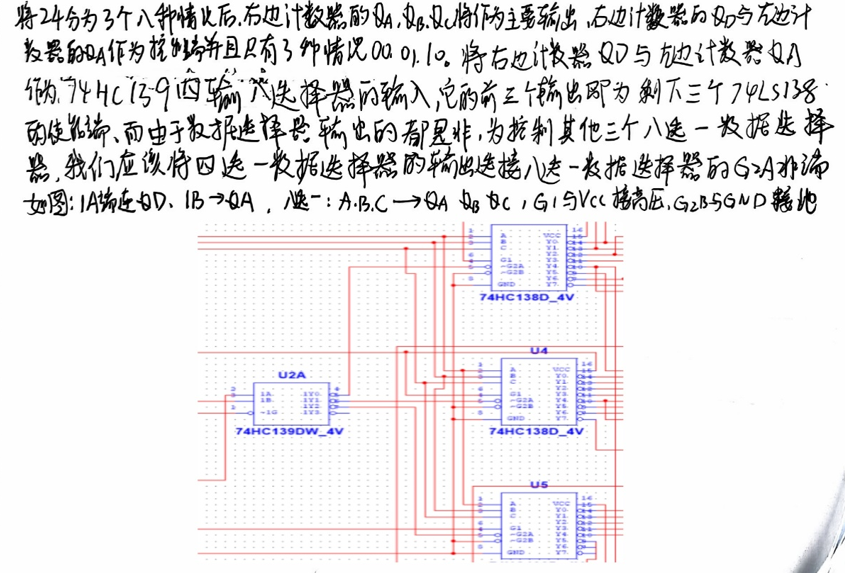

用2片74HC161(4位同步计数器) 拆成“3个8进制”(24=3×8),1片74HC161做2个8进制(低8位+中8位),另1片做高8位,3个8进制联动实现24进制。 - 难点2:怎么让不同阶段灭不同灯?

用74HC138(3-8译码器) 把8进制状态转LED控制信号,再用74HC139(2-4选择器) 选当前阶段的信号生效(比如阶段1选低8位信号,阶段2选中8位,阶段3选高8位)。 - 难点3:怎么确保1个状态只灭1个灯?

用74HC20(4输入与非门) 合并译码器输出,每个LED对应专属的“灭灯状态信号”,只有该状态下信号生效,其他状态灯保持亮。

二、器件分工:一张表看懂每个芯片的作用

不用记复杂参数,记住“模块分工”即可,新手按表找芯片功能:

| 器件型号 | 所属模块 | 通俗作用 | 核心任务 |

|---|---|---|---|

| 74HC161×2 | 24进制计数器 | 生成24个状态(0~23),1个状态=1个灭灯动作 | 2片芯片拆3个8进制,联动实现24进制循环,进位信号控阶段切换 |

| 74HC138×3 | 状态译码器 | 把8进制状态(07)转8路控制信号(Y0Y7) | 3片分别对应3个8进制,输出“哪个灯该灭”的信号 |

| 74HC139×1 | 阶段选择器 | 选当前阶段的译码信号(低8位/中8位/高8位) | 接收计数器进位信号,切换3个阶段的信号输入 |

| 74HC20×n | 信号合并器 | 把多个译码信号合并,控制单个LED灭灯 | 每个LED对应1个与非门,只有专属状态信号输入时输出“灭灯指令” |

| 共阴极LED×10 | 显示模块 | 按控制信号亮灭 | 阳极接与非门输出,阴极串1kΩ电阻接GND,高电平亮、低电平灭 |

| 函数发生器 | 时钟源 | 提供触发信号 | 输出1Hz方波(1秒1个状态切换,方便观察灭灯顺序) |

三、核心模块设计:从24进制计数到LED灭灯的全流程

分4个模块拆解,每个模块有接线关键和验证方法,新手可分步实操:

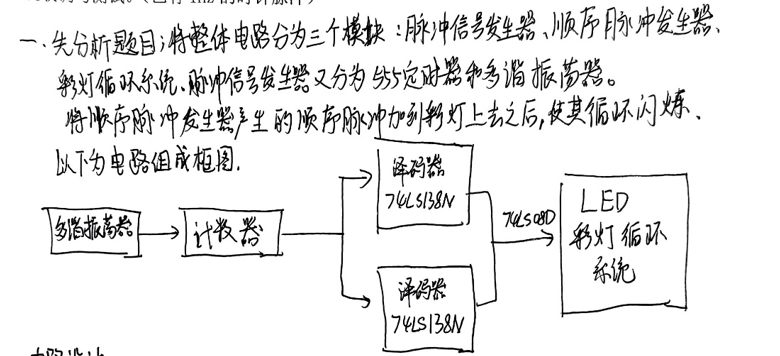

模块1:24进制计数器(用2片74HC161实现)

设计思路:拆成“低8位(07)+中8位(815)+高8位(16~23)”

接线步骤(关键引脚必看)

-

低8位计数器(U1:74HC161):

- 电源:VCC(16)接5V,GND(8)接GND;

- 使能:CEP(7)、CET(10)接VCC(允许计数);

- 清零:CR(1)接高电平(不清零),LOAD(9)接高电平(不置数);

- 时钟:CLK(2)接1Hz方波;

- 输出:Q2Q0(1412)接第1片74HC138的A2~A0(低8位状态),TC(11,进位端)接中8位计数器的CEP/CET(U2的7/10)。

-

中8位计数器(U2:74HC161):

- 电源/使能:同U1,CEP/CET接U1的TC(U1计满8个状态时,TC=1,触发U2计数);

- 输出:Q2Q0接第2片74HC138的A2A0(中8位状态),TC接高8位计数器的CEP/CET(U3的7/10)。

-

高8位计数器(U3:74HC161):

- 电源/使能:同U1,CEP/CET接U2的TC(U2计满8个状态时,TC=1,触发U3计数);

- 清零:当U3计到3(Q1=1, Q0=1)且U2计到7(Q2=1, Q1=1, Q0=1)时,用74HC20与非门输出低电平接CR(1),实现24进制清零(0~23循环);

- 输出:Q1Q0接74HC139的A1A0(阶段选择信号)。

功能验证

- 接示波器看U1~U3的Q输出:U1从000→111循环(8次),U2从000→111循环(8次),U3从00→10循环(8次),总共24次后清零,说明24进制正常。

模块2:阶段选择器(74HC139)

设计思路:用U3的Q1~Q0选3个8进制的译码信号

接线步骤

- 电源与使能:VCC(16)接5V,GND(8)接GND,G2A/G2B(1/2)接GND(允许选择);

- 输入:A1A0(32)接U3的Q1~Q0(阶段信号:00=低8位,01=中8位,10=高8位);

- 输出:Y0Y2(46)分别接3片74HC138的G1(使能端),Y3(7)悬空(不用);

- 当A1A0=00(阶段1):Y0=0,第1片138使能,其他2片禁用;

- 当A1A0=01(阶段2):Y1=0,第2片138使能;

- 当A1A0=10(阶段3):Y2=0,第3片138使能。

模块3:状态译码器(3片74HC138)

设计思路:每片138对应1个8进制,输出“哪个灯该灭”的信号

接线步骤(以第1片138为例,对应低8位阶段1)

- 电源与使能:VCC(16)接5V,GND(8)接GND,G1(6)接74HC139的Y0(阶段1使能),G2A/G2B(4/5)接GND;

- 输入:A2A0(31)接U1的Q2Q0(低8位状态07);

- 输出:Y0Y4(1511)接74HC20的输入(对应阶段1的5个灭灯状态:Y0=灭LED1,Y1=灭LED3,Y2=灭LED5,Y3=灭LED7,Y4=灭LED9),Y5~Y7悬空(阶段1用不到)。

其他2片138接线逻辑

- 第2片(中8位,阶段2):Y0~Y4接74HC20,对应灭LED2、LED4、LED6、LED8、LED10;

- 第3片(高8位,阶段3):Y0Y9接74HC20(需多片20级联),对应灭LED1LED10。

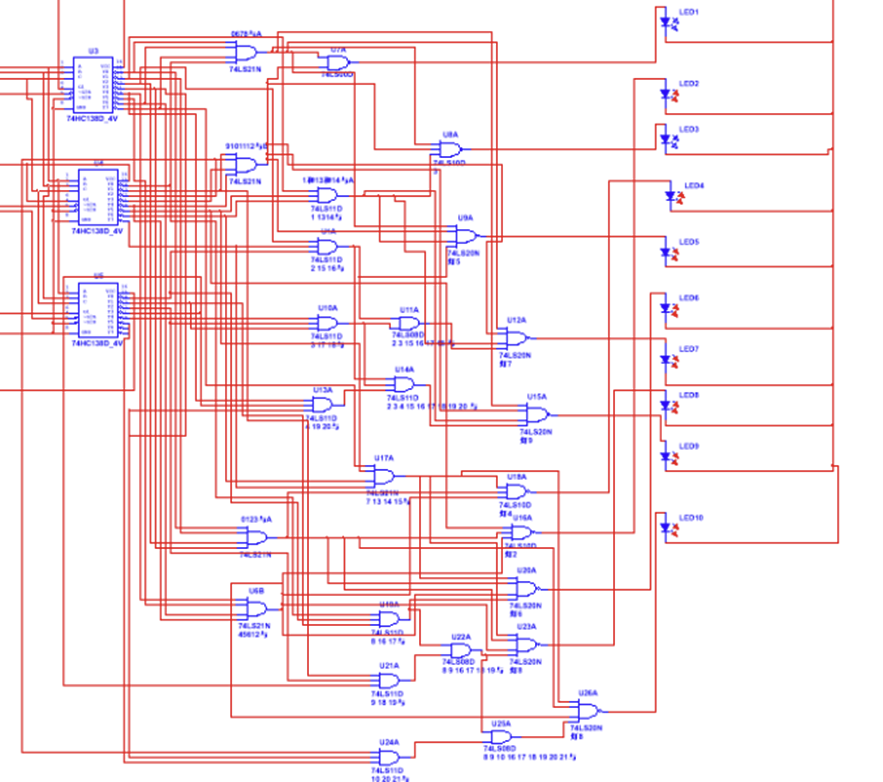

模块4:LED驱动(74HC20+LED)

设计思路:每个LED对应1个74HC20,只有专属状态信号输入时,LED灭

接线步骤(以LED1为例)

- 74HC20(与非门):

- 输入1:第1片138的Y0(阶段1灭LED1);

- 输入2:第3片138的Y0(阶段3灭LED1);

- 输入3~4:接高电平(不用,凑4输入);

- 输出:接LED1的阳极;

- LED1:阴极串1kΩ电阻接GND;

- 当阶段1Y0=0或阶段3Y0=0时,与非门输出1→LED1亮;

- 当Y0=1(对应灭灯状态)时,与非门输出0→LED1灭。

其他LED接线逻辑

- LED3:接第1片138的Y1+第3片138的Y2;

- LED2:接第2片138的Y0+第3片138的Y1;

- 以此类推,确保每个LED只在专属状态下灭,其他状态亮。

四、新手必避4个坑(我踩过的错,你别犯)

- 74HC161的进位端接反:把U1的TC接U2的CLK( instead of CEP/CET),导致U2不计数,24进制变成8进制,灭灯顺序混乱;

- 74HC138的使能端接错:忘了把G2A/G2B接GND,导致译码器不输出信号,所有LED一直亮;

- LED没串限流电阻:直接接电源,LED瞬间烧了,必须串1kΩ电阻,阳极接与非门输出;

- 74HC20的输入没接全:4输入与非门只接2个输入,其他输入悬空( instead of 接高电平),导致输出不稳定,LED乱闪。

五、测试步骤:分模块验证,避免整体出问题

新手别直接连整体电路,按以下步骤测,出问题能快速定位:

- 测计数器:断开译码器,接LED看U1U3的Q输出,是否023循环,24个状态后清零;

- 测选择器+译码器:给74HC139手动输入A1A0(00/01/10),看对应138是否输出低电平(用万用表测Y0~Y7);

- 测单个LED:给对应138的Y端手动输入高电平,看LED是否灭,其他状态是否亮;

- 测整体顺序:接1Hz时钟,观察LED是否按“奇灭→偶灭→依次灭”循环,24个状态后回到全亮。

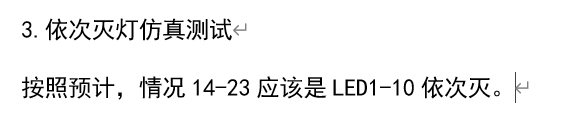

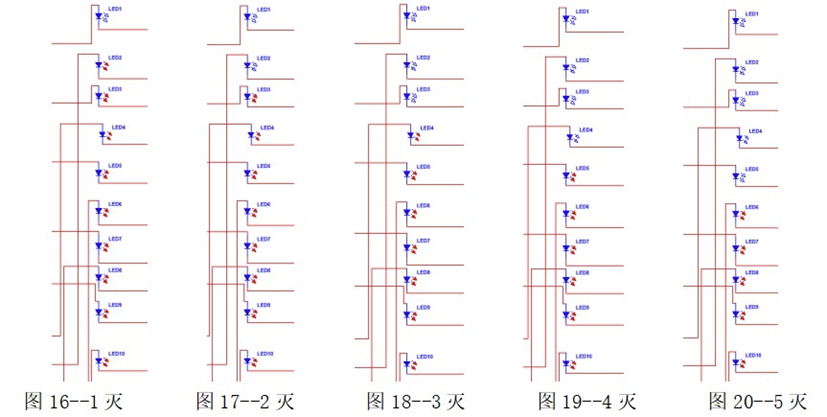

如图所示,我们的预计和演示结果相同,则奇偶数部分正确。