【STM32】WDG看门狗

【STM32】WDG看门狗

- 一、WDG简介

- 二、IWDG独立看门狗

- 2.1 独立看门狗框图

- 2.2 IWDG键寄存器

- 2.3 IWDG超时时间

- 三、WWDG窗口看门狗

- 3.1 窗口看门狗框图

- 3.2 WWDG工作特性

- 3.3 WWDG超时时间

- 四、IWDG和WWDG对比

一、WDG简介

- WDG(Watchdog)看门狗

- 本质:看门狗是一个定时器,其工作依赖于 “喂狗” 操作与超时复位的机制。

- 核心功能:监控程序运行状态,当程序因漏洞、硬件故障、电磁干扰等因素出现卡死、跑飞时,自动触发复位,避免系统长时间瘫痪,保障可靠性与安全性。

- 触发逻辑:程序需在规定时间内执行 “喂狗”(重置计数器)操作;若超时未执行,看门狗硬件会直接产生复位信号,重启系统。

- STM32内置两个看门狗

独立看门狗(IWDG):独立工作,对时间精度要求较低

窗口看门狗(WWDG):要求看门狗在精确计时窗口起作用

二、IWDG独立看门狗

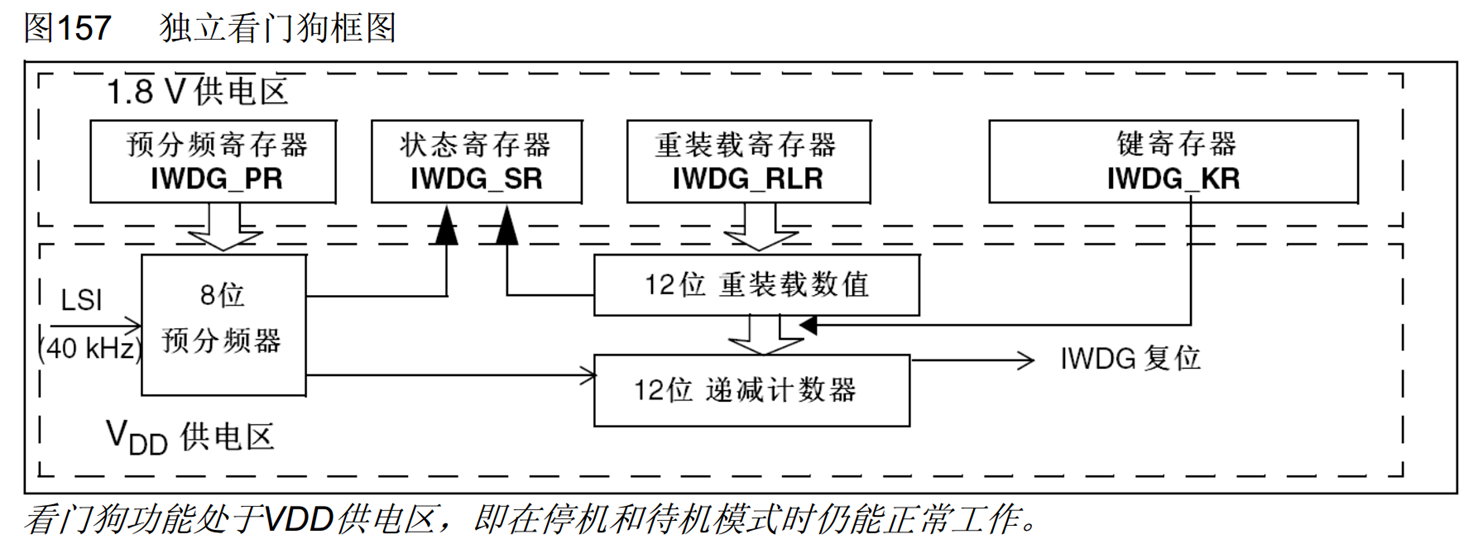

2.1 独立看门狗框图

1. 模块组成与供电

- 供电分区:

- 上方为

1.8V供电区,包含预分频寄存器(IWDG_PR)、状态寄存器(IWDG_SR)、重装载寄存器(IWDG_RLR)、键寄存器(IWDG_KR),这些是配置看门狗的“控制类寄存器”。 - 下方为

VDD供电区,包含预分频器、12位递减计数器、12位重装载数值,这些是看门狗的“时序执行类模块”。 - 特性:看门狗功能位于

VDD供电区,因此在停机模式、待机模式下仍能正常工作,保证异常场景下的监控能力。

- 上方为

2. 时钟与分频链路

- 时钟源(LSI):独立看门狗采用内部低速时钟(LSI),频率典型值为

40 kHz,它是看门狗的计时基准。 - 8位预分频器:由预分频寄存器(IWDG_PR)配置,可对LSI时钟进行分频,输出不同的计数时钟。分频系数可选(如/4、/8、/16…/256),用于调整看门狗的“超时周期”范围。

在预分频寄存器写入分频值,然后8位预分频器执行分频

3. 计数与重装载链路

- 12位递减计数器:基于分频后的时钟做递减计数,计数范围为

0~4095(12位最大值)。当计数器减到0时,触发IWDG复位,强制系统重启。 - 12位重装载数值:由重装载寄存器(IWDG_RLR)配置,用于定义“计数器的初始值”。程序执行“喂狗”操作时,会将该数值重新加载到递减计数器中,重置计数周期。

4. 控制与状态链路

- 键寄存器(IWDG_KR):是看门狗的“控制入口”,写入不同密钥实现不同功能:

- 写入

0xCCCC:启动看门狗计数; - 写入

0xAAAA:执行“喂狗”,将重装载数值加载到计数器; - 写入

0x5555:解锁预分频寄存器(IWDG_PR)和重装载寄存器(IWDG_RLR),允许修改配置。

- 写入

- 状态寄存器(IWDG_SR):用于标记看门狗的工作状态,例如是否正在进行“重装载操作”等,供程序查询。

5. 整体工作逻辑

- 配置阶段:写入

0x5555解锁寄存器,通过IWDG_PR设置分频系数、IWDG_RLR设置重装载数值,完成超时周期的定制。 - 启动阶段:写入

0xCCCC启动递减计数器,看门狗开始工作。 - 运行阶段:计数器不断递减,程序需在“超时前”写入

0xAAAA执行“喂狗”,将重装载数值重新加载到计数器,避免复位。 - 异常阶段:若程序卡死/跑飞,无法及时“喂狗”,计数器减到

0时,触发IWDG复位,系统重启,恢复可靠性。

2.2 IWDG键寄存器

- 键寄存器本质上是控制寄存器,用于控制硬件电路的工作

- 在可能存在干扰的情况下,一般通过在整个键寄存器写入特定值来代替控制寄存器写入一位的功能,以降低硬件电路受到干扰的概率

| 写入键寄存器的值 | 作用 |

|---|---|

| 0xCCCC | 启用独立看门狗 |

| 0xAAAA | IWDG_RLR中的值重新加载到计数器(喂狗) |

| 0x5555 | 解除IWDG_PR和IWDG_RLR的写保护 |

| 0x5555之外的其他值 | 启用IWDG_PR和IWDG_RLR的写保护 |

2.3 IWDG超时时间

- 超时时间:TIWDG=TLSI×PR预分频系数×(RL+1)T_{\text{IWDG}} = T_{\text{LSI}} \times \text{PR预分频系数} \times (\text{RL} + 1)TIWDG=TLSI×PR预分频系数×(RL+1)

+1原因:独立看门狗的12 位递减计数器是从 “重装载数值 RL” 开始,逐次减 1,直到减到 0 时触发复位。

- 其中:TLSI=1/FLSIT_{\text{LSI}} = 1 / F_{\text{LSI}}TLSI=1/FLSI

| 预分频系数 | PR[2:0]位 | 最短时间(ms) RL[11:0] = 0x000 | 最长时间(ms) RL[11:0] = 0xFFF |

|---|---|---|---|

| /4 | 0 | 0.1 | 409.6 |

| /8 | 1 | 0.2 | 819.2 |

| /16 | 2 | 0.4 | 1638.4 |

| /32 | 3 | 0.8 | 3276.8 |

| /64 | 4 | 1.6 | 6553.6 |

| /128 | 5 | 3.2 | 13107.2 |

| /256 | (6或7) | 6.4 | 26214.4 |

三、WWDG窗口看门狗

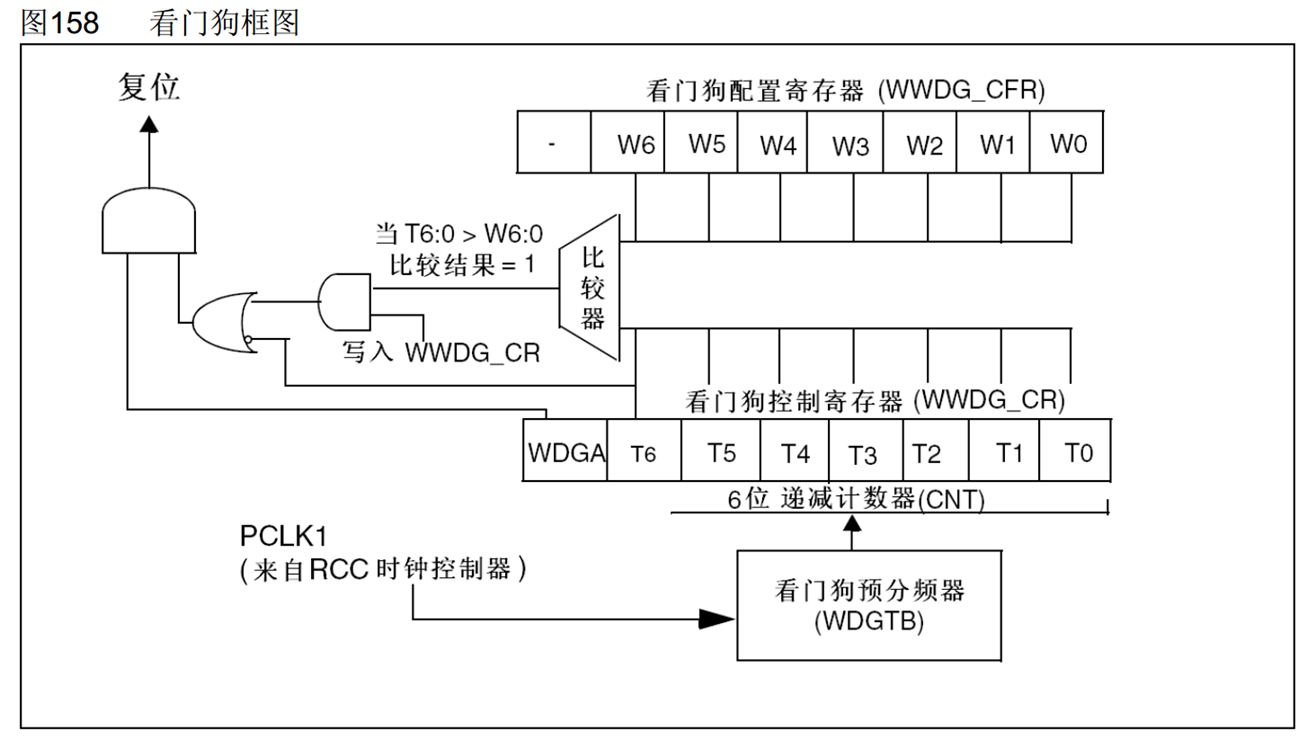

3.1 窗口看门狗框图

1. 时钟与分频链路

- 时钟源(PCLK1):窗口看门狗依赖外设时钟PCLK1(由RCC时钟控制器提供),因此其工作与主系统时钟强关联。

- 看门狗预分频器(WDGTB):对PCLK1进行分频,输出计数时钟,用于控制6位递减计数器的计时周期。

2. 计数与控制链路

- 6位递减计数器(CNT):集成在看门狗控制寄存器(WWDG_CR)中,计数范围为

0~63(6位最大值)。计数器不断递减,是窗口看门狗“超时检测”的核心时序单元。 - WWDG_CR寄存器:

WDGA位:看门狗使能位,置1则启动窗口看门狗;T6~T0位:6位递减计数器的当前计数值,程序需通过“喂狗”操作更新该值。

- 6位递减计数器(CNT)和看门狗控制寄存器(WWDG_CR)集成在同一寄存器

- WWDG_CR 中的 6 位递减计数器(T6~T0)是一直在自减的

- 窗口看门狗的 “喂狗” 操作就是向 WWDG_CR 寄存器写入新的计数值

- CNT是6位计数器,但寄存器却是7位,它是根据T6为准,如果T6由1变为0触发复位,所以实际上递减的是T5-T0。比如当寄存器自减到1000000,再减1,变为0111111时,溢出产生复位。

3. 窗口与比较链路

- 看门狗配置寄存器(WWDG_CFR):

W6~W0位:定义“喂狗窗口的上限值”,即程序必须在计数器值大于W6~W0且大于0的区间内执行喂狗操作(否则触发复位)。

- 比较器:实时比较WWDG_CR的T6T0与WWDG_CFR的W6W0:

- 若

T6~T0 > W6~W0,比较结果为1,此时允许程序执行“喂狗”; - 若

T6~T0 ≤ W6~W0或T6~T0 = 0,则触发复位逻辑。

- 若

4. 复位触发逻辑

复位由或门+与门的组合逻辑触发,满足以下任一条件时,系统将被复位:

- 计数器减到

0(超时未喂狗); - 喂狗操作在“窗口外”执行(即计数器值≤W6~W0时喂狗);

- 未在有效窗口内执行喂狗操作。

5. 整体工作逻辑

- 配置阶段:通过WWDG_CFR设置喂狗窗口上限(W6~W0),通过预分频器(WDGTB)设置计数时钟分频比。

- 启动阶段:向WWDG_CR的

WDGA位置1,启动6位递减计数器。 - 运行阶段:计数器不断递减,程序需在“计数器值 > W6~W0 且 > 0”的窗口内,写入新的计数值到WWDG_CR(喂狗),重置计数周期。

- 异常阶段:若程序卡死/跑飞,或喂狗操作在窗口外执行,触发复位逻辑,系统重启。

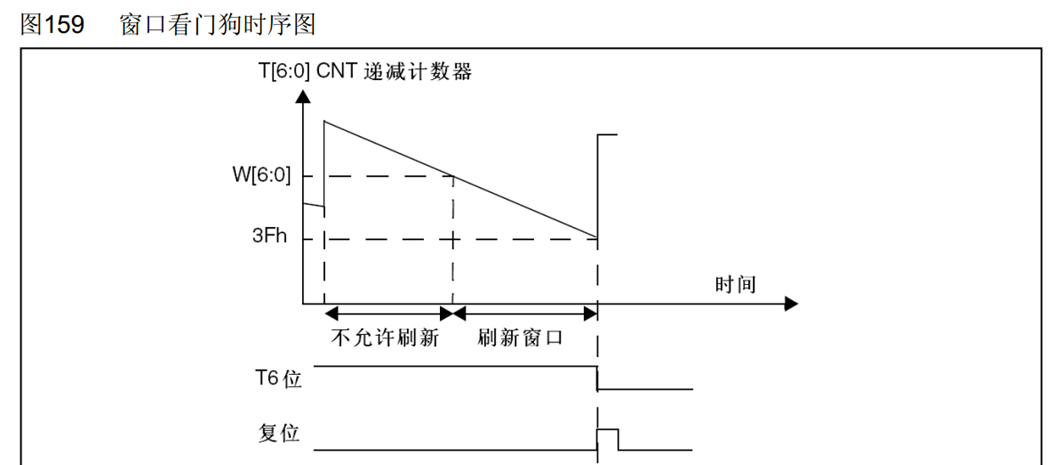

3.2 WWDG工作特性

- 递减计数器T[6:0]的值小于0x40时,WWDG产生复位

- 递减计数器T[6:0]在窗口W[6:0]外被重新装载时,WWDG产生复位

- 递减计数器T[6:0]等于0x40时可以产生早期唤醒中断(EWI),用于重装载计数器以避免WWDG复位

- 定期写入WWDG_CR寄存器(喂狗)以避免WWDG复位

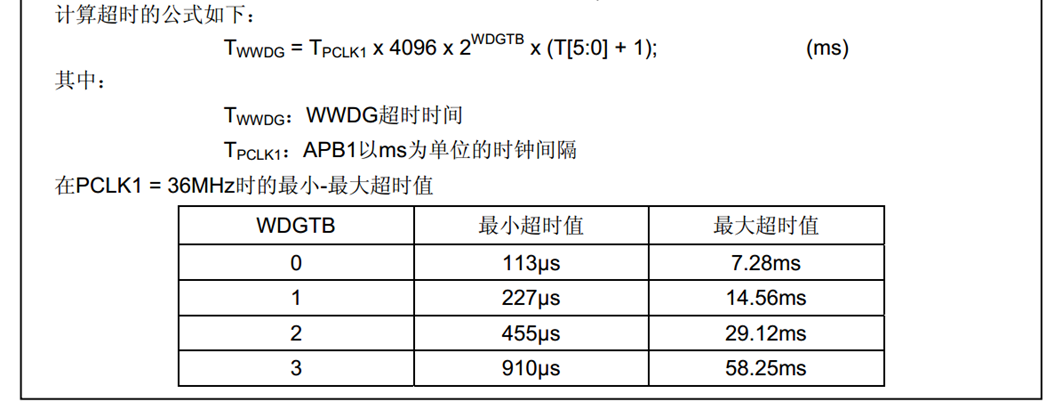

3.3 WWDG超时时间

- 超时时间:

TWWDG=TPCLK1×4096×WDGTB预分频系数×(T[5:0]+1)T_{\text{WWDG}} = T_{\text{PCLK1}} \times 4096 \times \text{WDGTB预分频系数} \times (\text{T[5:0]} + 1)TWWDG=TPCLK1×4096×WDGTB预分频系数×(T[5:0]+1)

- 窗口时间:

TWIN=TPCLK1×4096×WDGTB预分频系数×(T[5:0]−W[5:0])T_{\text{WIN}} = T_{\text{PCLK1}} \times 4096 \times \text{WDGTB预分频系数} \times (\text{T[5:0]} - \text{W[5:0]})TWIN=TPCLK1×4096×WDGTB预分频系数×(T[5:0]−W[5:0])

- 其中:TPCLK1=1/FPCLK1T_{\text{PCLK1}} = 1 / F_{\text{PCLK1}}TPCLK1=1/FPCLK1

Tpclk1 x 4096原因:WWDG 的计数基于一个内部的4096 分频器(这是芯片硬件设计的固定参数)。这个分频器会先对PCLK1进行 4096 倍的分频

四、IWDG和WWDG对比

| 对比项 | IWDG独立看门狗 | WWDG窗口看门狗 |

|---|---|---|

| 复位 | 计数器减到0后 | 计数器T[5:0]减到0后、过早重装计数器 |

| 中断 | 无 | 早期唤醒中断 |

| 时钟源 | LSI(40KHz) | PCLK1(36MHz) |

| 预分频系数 | 4、8、32、64、128、256 | 1、2、4、8 |

| 计数器 | 12位 | 6位(有效计数) |

| 超时时间 | 0.1ms~26214.4ms | 113us~58.25ms |

| 喂狗方式 | 写入键寄存器,重装固定值RLR | 直接写入计数器,写多少重装多少 |

| 防误操作 | 键寄存器和写保护 | 无 |

| 用途 | 独立工作,对时间精度要求较低 | 要求看门狗在精确计时窗口起作用 |

1. 复位机制

- IWDG独立看门狗:仅当12位计数器减到0时,才会触发系统复位。逻辑简单,仅监控“是否超时未喂狗”。

- WWDG窗口看门狗:复位触发有两种场景:

- 计数器

T[5:0](6位有效计数)减到0(超时未喂狗); - 过早重装计数器(即喂狗操作在“窗口外”执行,如计数器值≥窗口上限时喂狗)。

这种设计让WWDG能同时监控“程序是否跑飞超时”和“程序是否执行过快(过早喂狗)”。

- 计数器

2. 中断支持

- IWDG:无中断功能,仅通过复位强制系统重启。

- WWDG:支持早期唤醒中断(EWI)。当计数器值减到

0x40(T6位由1变0)时,会触发中断,可用于在复位前执行一些紧急操作(如保存关键数据)。

3. 时钟源

- IWDG:使用LSI(内部低速振荡器,典型40KHz),完全独立于系统主时钟(即使主时钟故障,IWDG仍能工作),但时钟精度较低。

- WWDG:依赖PCLK1(外设时钟,如36MHz),与系统主时钟强关联,时钟精度高,适合对时序要求严格的场景。

4. 预分频系数

- IWDG:预分频系数可选

4、8、32、64、128、256,可灵活调整计数器的计时周期,覆盖“0.1ms~26214.4ms”的超时范围。 - WWDG:预分频系数可选

1、2、4、8,计时周期相对更短,配合6位计数器实现“113us~58.25ms”的超时范围。

5. 计数器位数

- IWDG:12位计数器,计数范围

0~4095,结合预分频系数可实现长超时时间(最长约26秒)。 - WWDG:6位有效计数器(

T[5:0]),计数范围0~63,但因时钟源精度高、预分频系数调整灵活,仍能满足精准的短时监控需求。

6. 超时时间范围

- IWDG:超时时间跨度大(

0.1ms~26214.4ms),适合对时间精度要求不高、但需要长时间监控的场景(如工业控制中设备长时间无响应的复位)。 - WWDG:超时时间更短(

113us~58.25ms),且能通过“窗口机制”实现精准时序监控(如实时系统中程序必须在固定时间区间内执行喂狗)。

7. 喂狗方式

- IWDG:需通过“写入键寄存器”的方式,重装固定的重装载值(RLR)。操作相对繁琐,但有“键寄存器”和写保护机制防止误操作。

- WWDG:直接向**计数器寄存器(WWDG_CR)**写入新的计数值即可喂狗,写多少就重装多少,操作更灵活,但也更易因误操作触发复位。

8. 防误操作机制

- IWDG:通过“键寄存器(如写入0xCCCC解锁)”和写保护机制,防止程序误操作导致看门狗意外复位或关闭。

- WWDG:无专门的防误操作设计,喂狗操作完全依赖程序逻辑的正确性,因此对代码严谨性要求更高。

9. 用途差异

- IWDG:因独立时钟、长超时范围、防误操作机制,适合对时间精度要求低、但需稳定独立工作的场景(如普通嵌入式设备的“死机复位”)。

- WWDG:因精准时钟、窗口机制、早期中断,适合对程序时序要求严格的场景(如实时操作系统(RTOS)、通信协议栈中“必须在固定窗口内执行喂狗”的监控)。

有关【STM32】WDG看门狗 就到这,希望对你有所帮助,感谢观看!

码文不易,留个赞再走吧~