【无标题】Verilog中generate的用法

在使用FPGA设计时,可通过generate来简单的实现重复例化。对于generate语法具有三种形式分别为:

(1)generate case

(2)generate if

(3)generate for

一、模板的调用

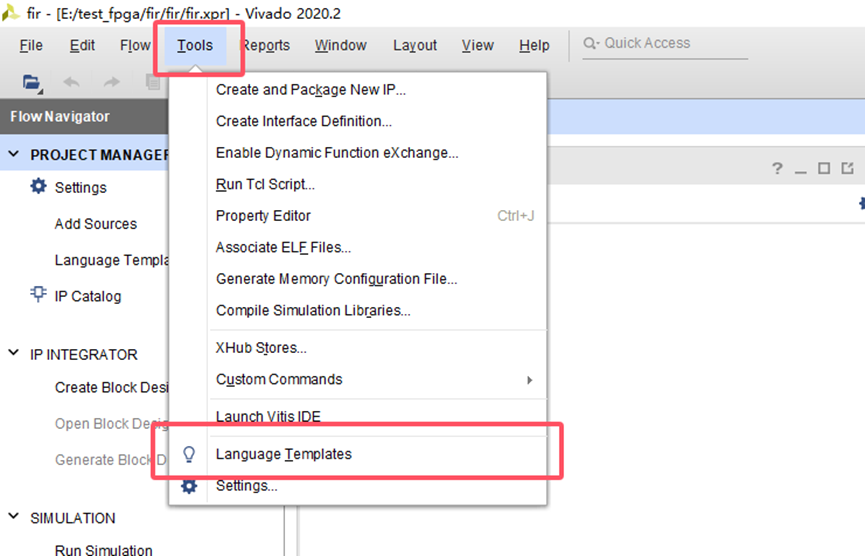

如果使用Vivado工具进行设计可以直接使用工具的模板功能来对函数进行调用。

点击菜单栏的Tools,选择Language Templates。

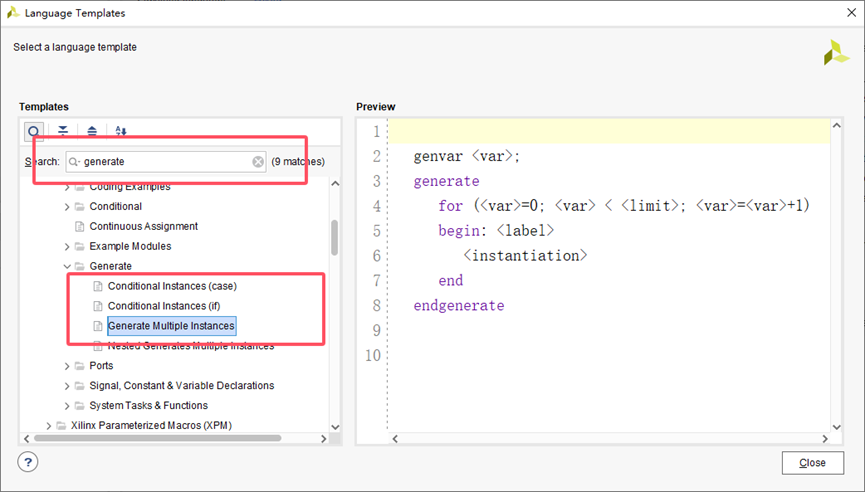

点击搜索图标,输入generate即可看到下图所示模板。

在上图中,表示变量,表示循环次数,

二、语法使用实例

1、generate case

从该语法中可以看出具有case,因此,该语法主要用于选择性综合电路,Vivado工具中给出的语法模板如下:

generatecase (<constant_expression>)<value>: begin: <label_1><code>end<value>: begin: <label_2><code>enddefault: begin: <label_3><code>endendcaseendgenerate

generate case和generate if作用上是差不多的,都是用于选择性综合电路,区别就是if语句和case语句的区别,如果你会用其中一个,那另一个也很简单,模板如下:

```c

generate

case ()

: begin:

end

: begin:

end

default: begin:

end

endcase

endgenerate

上面的例子照着改就是这样了:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out

);

localparamintegerPOL = 1;//根据POL的值来生成对应的电路

generate

case(POL)

1'b1: begin: POL1

assignout = a + b;

end

1'b0: begin: POL0

assignout = a - b;

end

default:begin:DEFAULT end

endcase

endgenerate

endmodule

一、generate if

generate if的使用场景和条件编译语句类似,比如你的代码中包含了一个加法模块和一个减法模块,对于2个输入a和b,希望使用POL来进行控制:如POL=1则进行加法,反之亦然----POL=1----out = a + b;POL=0----out = a - b。

代码是这样写的:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out

);

localparamintegerPOL = 1;//根据POL的值来生成对应的电路

generate

if (POL == 1) begin: POL1

assignout = a + b;

end else begin: POL0

assignout = a - b;

end

endgenerate

endmodule

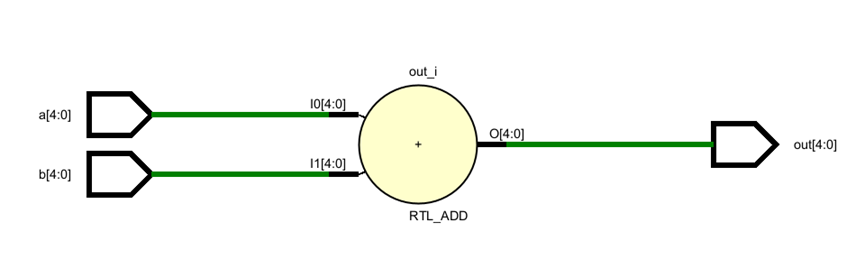

定义成POL = 1时会由vivado综合成一个加法器:

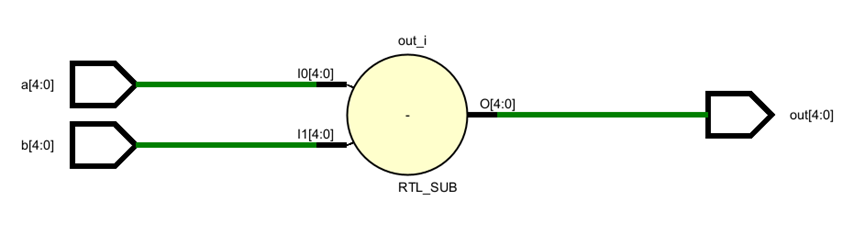

定义成POL = 0时则会由vivado综合成一个减法器:

假如不使用generate if语法,则代码是这样的:

module xor_test(

input[4:0]a,

input[4:0]b,

inputPOL,

outputreg[4:0]out

);

always@(*)begin

if(POL == 1)

out = a + b;

else

out = a - b;

end

endmodule

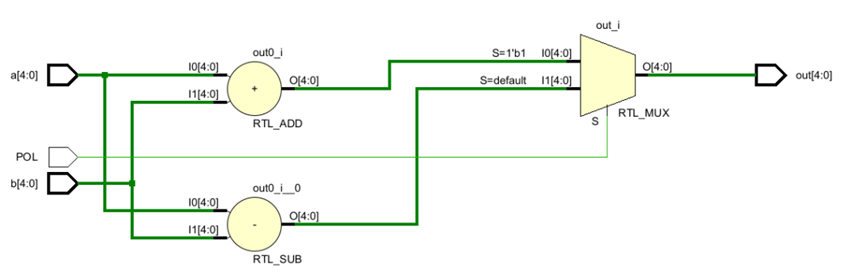

这样综合出来的就是加法电路和减法电路一起:

使用generate if可以根据需要来灵活地生成对应电路,不会浪费资源,适用于某些根据特定需求来实现电路的场景。而不使用该语句则会把所有潜在的电路均综合出来,会使电路面积增大,但是灵活性却较高。

这是vivado自带的语法模板:

generate

if () begin:;end else if () begin:;end else begin:;endendgenerate

二、generate for

假设我希望把2个输入a[4:0]和b[4:0]做一个异或操作,但是顺序要颠倒,也就是这样:

module xor_test(

input[4:0]a,

input[4:0]b,

output[4:0]out);

assignout[4] = a[4] ^ b[0];

assignout[3] = a[3] ^ b[1];

assignout[2] = a[2] ^ b[2];

assignout[1] = a[1] ^ b[3];

assignout[0] = a[0] ^ b[4];

endmodule

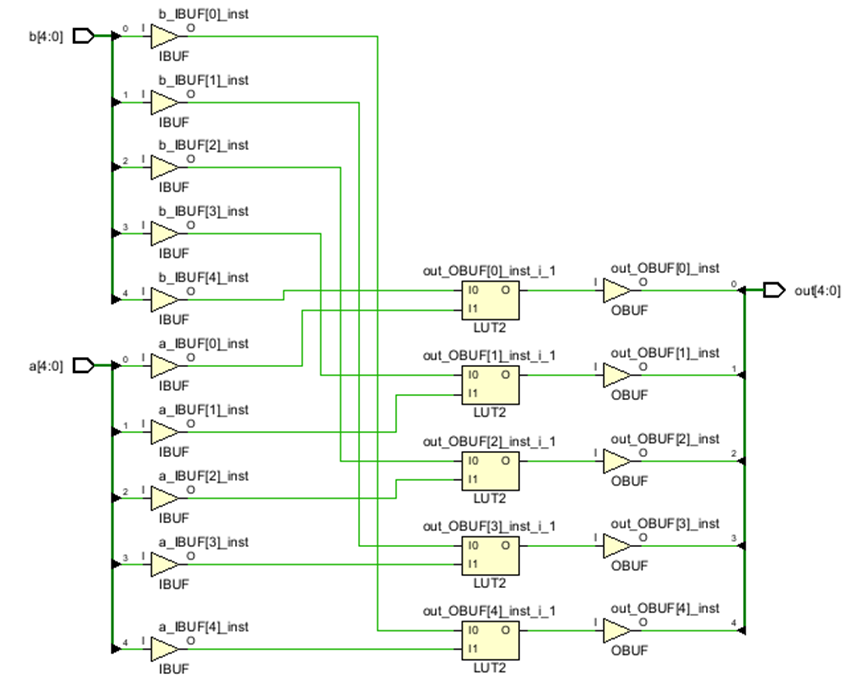

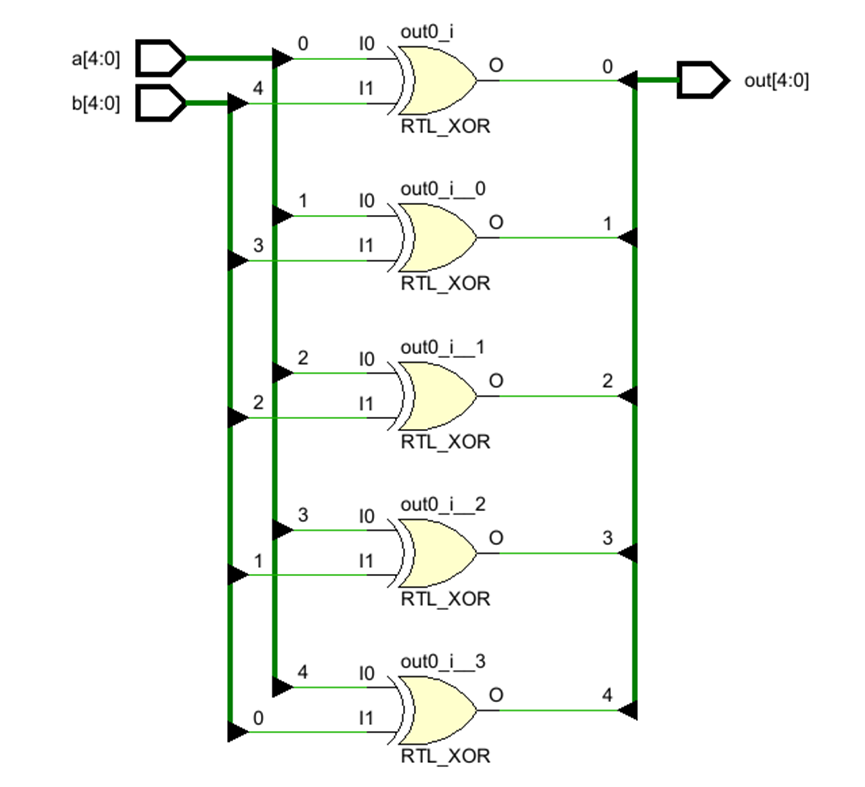

在vivado中分析出来是这样的:很简单就是两个输出的不同为做一个异或运算。

vivado综合出来是这样的:用了几个LUT来实现异或功能。