基线设计(Baseline Design)全流程拆解(二)

基线设计(Baseline Design)全流程拆解

文章目录

- 基线设计(Baseline Design)全流程拆解

- 前言

- 第一章 基线设计(Baseline Design)全流程拆解

- 1.1 知识点:基线设计三大阶段

- 1.2 解析:为什么必须“-0.3 ns”红线

- 1.3 补充:三步走检查脚本(一键模板)

- 2.1 知识点:Timing Constraints Wizard(TCW)正确打开方式

- 2.2 解析:TCW 为何有时扫不出 GT/高速收发器时钟

- 3.1 知识点:例外约束“三剑客”优先级

- 3.2 解析:为什么“只写 -setup 不写 -hold”会翻车

前言

对于例外约束,一般靠代码,而不是靠约束来规避。

第一章 基线设计(Baseline Design)全流程拆解

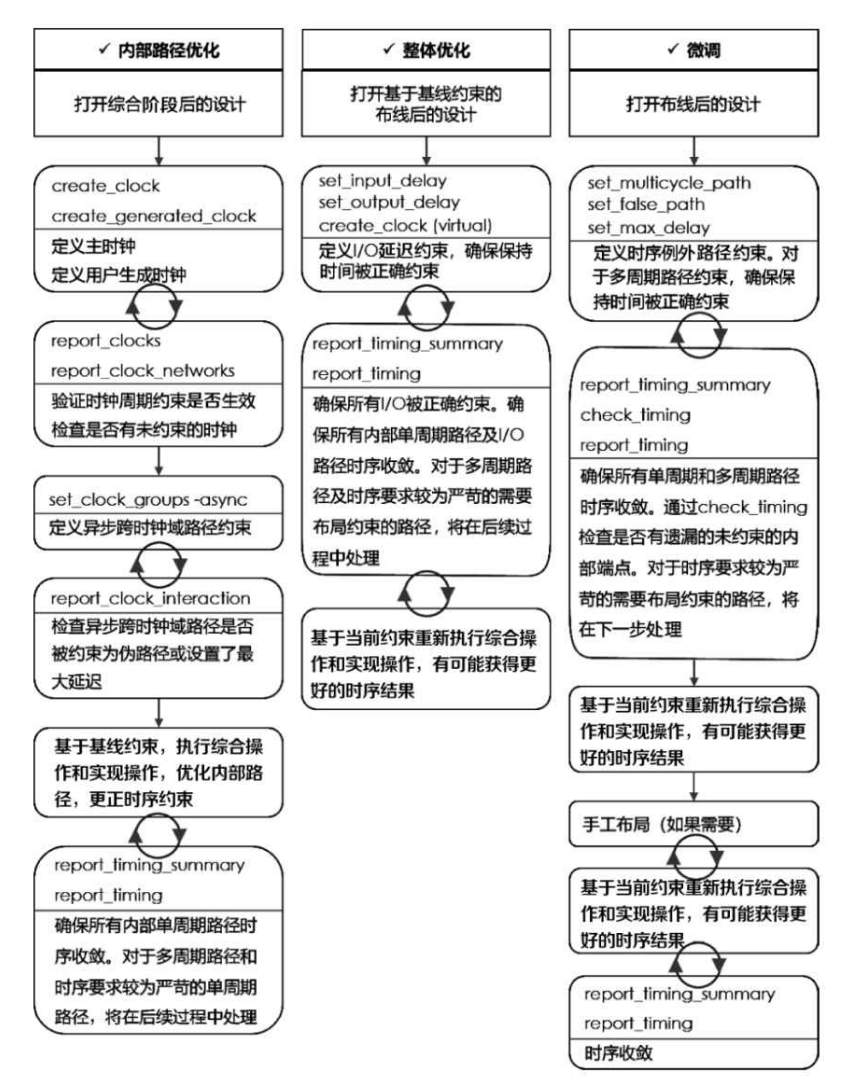

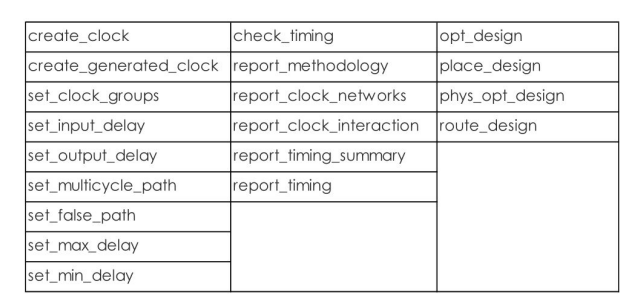

对应原书 5.2 节,官方推荐的“三步走”时序收敛骨架

1.1 知识点:基线设计三大阶段

| 步骤 | 目的 | 门槛值 | 交付物 |

|---|---|---|---|

| ① 基线约束 | 让所有内部同步路径被正确约束 | 综合后 WNS ≥ -0.3 ns | 只有时钟+异步组+明显伪路径 |

| ② 添加 IO 约束 | 让所有 IO 路径也被约束 | 实现后 WNS ≥ -0.3 ns | 加入 set_input/output_delay |

| ③ 添加例外约束 | 让多周期/虚假路径真正生效 | 最终 WNS ≥ 0 ns | 最终冻结版 XDC |

任何一步 WNS < -0.3 ns → 停!先修时序或 RTL

1.2 解析:为什么必须“-0.3 ns”红线

- 布局后 WNS < -0.3 ns 时,布线器几乎没有 slack 可借给保持时间修复 → 最终很难拉到 0 ns

- 官方经验值:-0.3 ns 是 “布线阶段还能拉回来” 的最后安全垫

- 若 -0.3 ns 仍达不到 → 必须先 逻辑优化/插流水线/换策略,而不是继续往下加约束

1.3 补充:三步走检查脚本(一键模板)

# Step-0 环境准备

open_run synth_1

set rpt_suffix [clock format [clock seconds] -format %m%d%H%M]# Step-1 基线体检

check_timing -name chk_base_$rpt_suffix

report_methodology -name ufdm_base_$rpt_suffix

report_clock_networks -name clk_base_$rpt_suffix

report_timing_summary -name ts_base_$rpt_suffix

脚本化→ nightly Jenkins 可自动判红:出现 Critical/Warning 即中断流水线

2.1 知识点:Timing Constraints Wizard(TCW)正确打开方式

- 只在综合后网表打开 → 工具能 看到真实时钟端口

- 第一阶段只填三类:

- 主时钟

create_clock - 生成时钟

create_generated_clock - 异步时钟组

set_clock_groups -async

- 主时钟

- IO 延迟、多周期、false_path 先跳过 → 保证 baseline 纯净

2.2 解析:TCW 为何有时扫不出 GT/高速收发器时钟

- GT 的

RXOUTCLK/TXOUTCLK藏在 IP 子层次,不是顶层端口 - TCW 默认 只扫顶层端口 → 会漏掉 RXOUTCLK/TXOUTCLK

- 结果:

check_timing报 no_clock → 真实频率可能 > 300 MHz,隐患极大

3.1 知识点:例外约束“三剑客”优先级

set_clock_groups > set_false_path > set_max/min_delay > set_multicycle_path

同一路径同时被多条命中 → 按上面顺序生效,后面的被忽略

3.2 解析:为什么“只写 -setup 不写 -hold”会翻车

set_multicycle_path 3 -setup只把建立捕获沿推后 2 周期- 保持检查仍用默认捕获沿 → Hold Requirement = 1 周期 → 可能报假 Hold 违例

- 必须成对写:

set_multicycle_path 3 -setup -end set_multicycle_path 2 -hold -end ;# 3-1=2